Early Introduction to Programmable Devices and Tools in Digital

advertisement

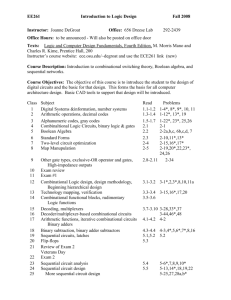

Early Introduction to Programmable Devices and tools in Digital Laboratory Course Parimal Patel Wei-Ming Lin Presented by Dr. Mehdi Shadaram Chirag Parikh John Prevost Department of Electrical and Computer Engineering University of Texas at San Antonio Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion TWD Grant: 010115-EE2003-0000 • Objective – Increase the number of high-quality graduates who are technically competent and competitive in the nation • Strategies – Student Retention and – Curriculum and Laboratory Improvement Dr. Shadaram Add Your Slide Dr. Shadaram Add Your Slide Introduction • Logic devices can be classified into: – Fixed Logic device – Programmable Logic device (PLD) • As technology evolved Complex devices were developed • Two major types of programmable devices: – Complex Programmable Logic Devices (CPLD) – Field Programmable Gate Arrays (FPGA) Introduction • Complex Programmable Logic Device – Supports lesser amount of logic compared to FPGA – Consumes less power • E.g. Xilinx Coolrunner CPLD can be run with citrus fruit – Inexpensive – Ideal for cost-sensitive, battery-operated portable applications • Mobile phones • Digital Hand-held Assistants Introduction • Field Programmable Gate Arrays – Supports dense, complex systems – Special function architectural resources • To improve silicon efficiencies – Ideal for high density applications • Data processing and storage • Digital Signal Processing • CAD Tools are required to design and implement functions Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion Curriculum • 2004-2006 – Electrical Engineering Undergraduate students were required to take • EE 2513 (Logic Design) • EE 3463 (Microcomputer Systems I) • EE 3563 (Digital Systems Design) – These courses were pre-requisites for • EE 4243 (Computer Organization and Architecture) • EE 4513 (Introduction to VLSI Design) • EE 4583 (Microcomputer Systems II) Curriculum • Topics covered: – EE 2513 • Problem solving sessions to emphasize logic design principles • Conducted by Teaching Assistants – EE 3563 • Draw and simulate simple combinational circuits – Multiplexer, 16-bit adder, sequence detector • Tools used: – Mentor Graphics for schematic capture – ModelSim for simulation Curriculum • Shortcomings in Digital Curriculum – EE 2513 • No laboratory experiments or tools exposure – EE 3563 • Barely introduced VHDL • One assignment involving VHDL (4-bit adder) – Overall limited exposure to VHDL and CAD tools • Lack of modeling even medium-complexity system – Students not exposed to hands-on experiments • Building circuits using real IC’s • Solution – Changes were made into current curriculum Curriculum • 2006-2008 – Introduction of new course • EE 2511 (Logic Design Laboratory) • Requires simultaneous enrollment or completion of EE 2513 • One 1–hour lecture and 2-hour Laboratory class • Involves CAD tools for analysis and design of digital circuits • Hands-on experience with IC’s, CPLD kits and FPGA boards Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion Logic Design Laboratory Course • New edition of textbook used – Hardware modeling concepts – CD containing LogicAid and SimuAid programs • Upon funding of proposal written to TETC – Xilinx CPLD based kits were phased in starting Fall 2005 • Designed and verified combinational circuit on hardware • Three experiments carried out during recitation sessions • Demonstration of experiment on sequential circuits Logic Design Laboratory Course • In Fall 2006 – Introduced EE 2511 course – Course objectives • Implement concepts learned in EE 2513 using 74xx IC’s • Implement concepts learned in EE 2513 using CAD tools • Develop models in VHDL and implement using CPLD/FPGA based kits – Topics covered • Schematic captures, gate-level and timing simulation • Design implementation using IC’s and 7-segment • VHDL coding, behavioral/timing simulation, synthesis and implementation Logic Design Laboratory Course – Coursework • Five tutorials and Seven lab assignments • Mid-term and final projects • Care taken that topics for laboratory assignments are covered in EE 2513 or EE 2511 beforehand • Enhance written and oral communication skills – Students asked to write formal report for projects – Students asked to give formal presentation for final project Logic Design Laboratory Course – Tutorials were developed on • • • • • • Logic reduction using Boolean Algebra (LogicAid) Entering schematics for combinatorial circuits (SimuAid) Simulation of sequential circuits (SimuAid) Logic reduction using K-Maps (LogicAid) VHDL modeling, synthesis and implementation (Xilinx ISE) Simulation (ISIM and ModelSim simulators) – Hardware kits used • Freescale MCU Project board – Build circuits using IC’s and 7-segment • Xilinx’s CoolRunner XPLA3 CPLD-based kit – Combinatorial circuit design • Xilinx’x Spartan3E-based starter kit – Sequential circuit design Logic Design Laboratory Course Topics covered in Logic Design Laboratory and theory class Spring 2007 Example Week EE 2511 EE 2513 1 Introduction to course and Lab Chap 1: Number systems and conversion 2 LogicAid tool and Lab 1 Chap 2: Boolean Algebra 3 SimuAid tool and Lab 2 Chap 3: Boolean Algebra Chap 4: Minterm and Maxterm 4 Building combinational circuits with IC’s (Lab 3) Review of Chapters 1-4 and Exam 1 5 VHDL for combinational circuits Chap 5: K-Maps 6 ISE tool / ISIM simulator Chap 6: Quine-McCluskey for combinational circuit Chap 7: Multi-level gate networks Logic Design Laboratory Course Week EE 2511 EE 2513 7 Using CPLD for combinational circuits Chap 8: Combination circuit design Chap 9: PLDs 8 Design combinational circuit – Midterm project Chap 9 continues Chap 0: Introduction to VHDL 9 SimuAid tool for sequential circuits and Lab 5 Chap 11: Latches and Flip Flops 10 Building sequential circuits with IC’s (Lab 6) Chap 12: Registers and Counters 11 VHDL for sequential circuits Chap 13: Clocked sequential circuits and Exam 2 Logic Design Laboratory Course Week EE 2511 EE 2513 12 ModelSim for sequential Chap 13 continues circuits and Lab 7 Chap 14: State Graphs and Tables 13 Using CPLD/FPGA for sequential circuits and Final Project assigned Chap 15: State Table reduction and State Assignment 14 Designing sequential circuits (Final project continues) Chap 16: Sequential circuit design 15 Final Project concluded Chap 16 continues Chap 17: VHDL for sequential logic Logic Design Laboratory Course • LogicAid Tool – Useful for boolean expression minimization using • Boolean laws and theorem • K-Maps – Labs used • Lab 1, Lab 2, Lab 3 Logic Design Laboratory Course • SimuAid Tool – Useful for simple schematic capture and combinational and sequential circuits simulation – Labs used • Lab 2, Lab 3, Lab 4 Logic Design Laboratory Course • ISE and ISIM – Useful for Xilinx CPLD and FPGA kits • VHDL Modeling • Behavioral Simulation – Labs used • Lab 6, Lab 7 – Projects used • Mid-term and Final Logic Design Laboratory Course • ICs based labs – ICs used • 7400, 7404, 7408, 7432 – Other devices used • Switches, LEDs, 7-segment – Labs used • Lab 3, Lab 6 Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion Student’s Perspective • Introduction • Hands-on approach – Access to software alone not sufficient – Build-to-learn – Wired-up • VHDL by practice – Simulation – Debugging Student’s Perspective • Process of design – Problem statement – Formulate design – Build/Test/Debug – Present/Demonstrate outcome • Exposed to FPGA’s and CPLD’s – Lecture theory only – Labs/projects gave concrete examples – Facilitated deeper level of understanding Student’s Perspective • Summary – Enhanced learning – Stimulated interest – Left with desire to “do-more” Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion Summary • Hardware boards – Freescale, Xilinx • Software tools – Logic Design by Charles Roth (Textbook) – Xilinx under University Program • Department cost – IC’s, bread-board wires EE2511 Class Enrollment • Course enrollment Number of students 25 20 15 Fall 2006 10 Spring 2007 5 0 Female Hispanics Students Total Outline • Introduction • Curriculum – 2004-2006 Catalog – 2006-2008 Catalog • Logic Design Laboratory Course • Undergraduate Student Feedback • Summary • Conclusion Conclusion • New course has helped us modify EE 3563 content – VHDL modeling (First week) – Spartan3E kits (Mid-semester) • Students implement complex finite state machines • Recommend use of – Tools, Hands-on experiments and programmable devices-based kits early in curriculum • Stimulate interests among students • Validate basic fundamentals using tools and hands-on experience