Chapter 3

advertisement

CHAPTER 3

INSTRUCTIONS:

LANGUAGE OF THE

MACHINE

1

Instruction Set Architecture

• Computer architecture instruction set is the interface

between hardware and software.

• The attributes of an instruction set include

– Instruction Set (what operations can be performed?)

– Instruction Format (how are instructions specified?)

– Data storage (where is data located?)

– Addressing Modes (how is data accessed?)

– Exceptional Conditions (what happens if something goes wrong?)

• A good understanding of computer architecture is

important for compiler writers, operating system designers,

and general computer programmers.

2

MIPS R3000 Instruction Set Architecture (Summary)

• Instruction Categories

–

–

–

–

–

–

R0 - R31

Load/Store

Computational

Jump and Branch

Floating Point

Memory Management

Special

PC

HI

LO

3 Instruction Formats: all 32 bits wide (fixed Size)

shamt funct

OP

rs

rd

rt

OP

OP

rs

rt

immediate

jump target

3

Instruction Execution

Instruction

Fetch

Instruction

Decode

Obtain instruction from program storage

Determine required actions and instruction size

Locate and obtain operand data:

Operand

Fetch

Execute

Result

Store

Next

Instruction

From where: memory, instruction, etc.

How many operands?

How are the operands located?

Compute result value or status:

What data type is the result?

Deposit results in storage for later use

Where to deposit the result?

Determine successor instruction

4

MIPS Instructions

• MIPS is an Assembly Language

• Assembly languages are more primitive than higher level

languages e.g., no sophisticated control flow

• Assembly languages are very restrictive

e.g., MIPS Arithmetic Instructions

• We’ll be working with the MIPS instruction set architecture

– similar to other architectures developed since the 1980's

– used by NEC, Nintendo, Silicon Graphics, Sony

Design goals: maximize performance and

minimize cost, reduce design time

5

Registers

• Registers are special locations on the processor

– “Bricks” of computer construction

– Used in hardware design and visible to the programmer

– Very fast access

6

MIPS Addressing Modes (Location of operands)

• Addressing modes specify where the data used by an

instruction is located. Data can be in registers, memory or

within the instruction itself (available immediately).

Mode

Example

register direct add $s1, $s2, $s3

Action

$s1 = $s2 + $s3

immediate

addi $s1, $s2, 200 $s1 = $s2 + 200

base + index

lw $s1, 200($s2)

$s1 = mem[200 + $s2]

PC-relative

beq $s1, $s2, 200

if ($s1 == $s2)

PC = PC+4+200*4

Pseudo-direct

j 4000

PC = (PC[31:28],

4000*4)

7

MIPS Addressing Modes

• All MIPS instructions are 32 bits wide - fixed length

• The instruction format depends on the addressing mode

Register (direct)

op

rs

rt

add $s1, $s2, $s3

rd

register

Immediate

Base+index

op

rs

rt

immed

addi $s1, $s2, 200

op

rs

rt

immed

What happens if immed. Increases?

register

Memory

+

lw $s1, 200($s2)

PC-relative

op

rs

PC

rt

immed

Memory

+

beq $s1, $s2, 200 9

MIPS Addressing Modes/Instruction Formats

Pseudo-direct

op

address

Memory

x$4

j 4000

Addressing

Mode

Register

(direct)

Instruction Format/Type

R-type

op

rs

rt

I-Type

op

rs

rt

rd

Immediate

Base + index

immed

PC-relative

Pseudo-direct J-Type

op

address

10

MIPS Instruction Fields : R-Type and I-Type

• Register type (R-type) and immediate type (I-Type) instructions

have the following formats:

e.g. add, sub, and, or

R-type

I-type

Field

op

rs

rt

rd

shamt

funct

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

op

rs

rt

immed

sw, lw, beq

op

Meaning

Basic operation of the instruction (opcode)

rs

First register source operand

rt

rd

Second register source operand

Register destination operand (gets result)

shamt

Shift amount

funct

Function field - selects the variant of the operation in the op field

(function code)

immed

Immediate value

11

Representing Instructions in the Computer

• Computer represents numbers in base 2 (binary)

– Series of high and low electronic signals in hardware (on and off)

• Instructions are stored in hardware in the same way

– Can be represented as numbers

• Assembly to machine code

add $t0, $s0, $s1

op

rs

rt

17

18

8

6 bits

5 bits

5 bits

5 bits

000000

10001

10010

01000

0

rd

shamt

0

5 bits

00000

funct

32

6 bits

100000

12

Register Names in MIPS Assembly Language

• There is a convention for mapping register names into general

purpose register numbers. Only 32 registers provided.

• Design Principle: smaller is faster. Why?

A large number of registers increase the instruction

execution time because electronic signals longer

travel further.

With 32 registers, each can be represented using

just 5 bits. If you increase the number of registers,

more bits will be required.

13

Register Names in MIPS Assembly Language

Register name

Register number

Register usage

$zero

0

constant 0

$at

1

assembler: large constants

$v0-$v1

2-3

results (func. ret. values)

$a0-$a3

4-7

arguments

$t0-$t7

8-15

temporaries

$s0-$s7

16-23

saved

$t8-$t9

24-25

more temps

HI, LO

26-27

multiplication and division

$gp

28

global pointer

$sp

29

stack pointer

$fp

30

frame pointer

$ra

31

return address

14

MIPS arithmetic

• A compiler translates high-level code to assembly language e.g

MIPS. All MIPS arithmetic instructions have 3 operands

– Design Principle: Simplicity favors regularity

– Same number of operands and in the same order

• Variables are typically stored in registers - why ?

• Operand order is fixed (destination first)

• Example 1:

C code:

a = b + c;

MIPS code: add $s0, $s1, $s2

The registers $s0, $s1, $s2 are associated with variables by compiler, say $s0

with a, $s1 with b and $s2 with c.

•

Example 2:

C code:

MIPS code:

a = b - c;

sub $s0, $s1, $s2

15

MIPS arithmetic: Using temporary registers

• Example 3:

C Code:

a = (b + c) - (d + c);

Assume the variables a, b, c, and d are in registers $s3, $s4,

$s5, and $s6, respectively.

Instruction

add $t2, $s4, $s5

add $t3, $s6, $s5

sub $s3, $t2, $t3

Comment

$t2 = b + c

$t3 = d + c

a = $t2 - $t3

16

Registers vs. Memory

• Arithmetic instructions operands must be registers,

— only 32 registers provided

• Compiler associates variables with registers

• What about programs with lots of variables? The compiler

keeps the most frequently used variables in registers and the

rest in memory. This is called spilling of registers.

Control

Input

Memory

Datapath

Processor

Output

I/O

17

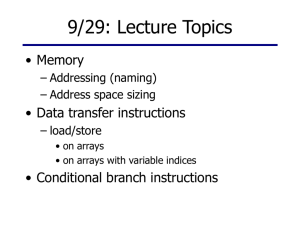

Memory Organization

• Viewed as a large, single-dimension array, with an address.

• A memory address is an index into the array

• "Byte addressing" means that each index points to a byte of

memory.

0

1

2

3

4

5

6

...

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

18

Memory Organization

• Bytes are nice, but most data items use larger "words"

• For MIPS, a word is 32 bits or 4 bytes.

0

4

8

12

...

32 bits of data

32 bits of data

32 bits of data

Registers hold 32 bits of data

32 bits of data

• 232 bytes with byte addresses from 0 to 232-1

• 230 words with byte addresses 0, 4, 8, ... 232-4

• Words are aligned. That is, their addresses are multiples of 4.

19

Stored Program Concept

• Instructions are bits

• Programs are stored in memory

— to be read or written just like data

Processor

Memory

memory for data, programs,

compilers, editors, etc.

Fetch & Execute Cycle

– Instructions are fetched and put into a special register

(PC)

– Bits in the register "control" the subsequent actions

– Fetch the “next” instruction and continue

20

Example of Using MIPS Instructions - Arrays

• Arrays are often stored in memory - why?

• Replace the C code for

A[11] = A[10] + b

•

•

•

•

by equivalent MIPS instructions.

Assume b is in register $s5, the starting address for array A is in

$s6, using and 32-bit integer data.

Instruction

Comment

lw $t3, 40 ($s6)

$t3 = A[10]

add $t4, $t3, $s5

$t4 = A[10] + b

sw $t4, 44($s6)

A[11] = $t4

Why are array indices multiplied by 4? Store word has

destination last

Write assembly instructions to:

b = A[10] + c;

A[11] = b + c;

21

MIPS – Conditional / Unconditional Instructions

• Conditional statements allow us to make decisions. These

decision making instructions

– alter the control flow,

– i.e., change the "next" instruction to be executed

• MIPS unconditional branch instructions:

j

label

• MIPS conditional branch instructions:

bne $t0, $t1, Label

beq $t0, $t1, Label

• Example:

MIPS:

if (i==j) h = i + j;

bne $s0, $s1, Label

add $s3, $s0, $s1

Label:

....

22

MIPS – Conditional / Unconditional Instructions

• Replace the C code for

if (i = = j) f = g + h; else f = g - h;

by equivalent MIPS instructions.

Assume variables f through j correspond to registers $s0 through $s4.

Instruction

bne $s3, $s4, Else

add $s0, $s1, $s2

j Exit

Else: sub $s0, $s1, $s2

Exit:

Comment

if (i != j) goto Else

f=g+h

go to Exit

f=g-h

• How would you implement the loop

while (k < j) k = k + j;

23

MIPS function assembling

• Assume v = $a0, k = $a1, temp = $s1.

• Temporaries used are $t1 (storing into array) and a

temporary holder $t2 (for address of array element).

swap(int v[], int k)

{

int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

swap:

# save s/t registers on stack here

muli $t2, $a1, 4

#t2 = k*4

add $t2, $a0, $t2 #t2 has address of v[k]

lw $s1, 0($t2)

#temp = v[k]

lw $t1, 4($t2)

#t1 gets v[k+1]

sw $t1, 0($t2)

#store t1 into v[k]

sw $s1, 4($t2)

#store temp into v[k+1]

# restore registers from stack here

jr $ra

#jump back after call

24

Machine Language

• Instructions, like registers and words of data, are also 32 bits

long

– Example: add $t0, $s1, $s2

– registers have numbers, $t0=8, $s1=17, $s2=18

• Instruction Format:

000000 10001

op

rs

10010

rt

01000

00000

100000

rd shamt funct

• Can you guess what the field names

stand for?

op = Basic operation of the instruction: opcode

rs = The first register source operand

rt = The second register source operand

rd = The register destination operand

shamt = shift amount

funct = function code

25

Machine Language

• Consider the load-word and store-word instructions,

– Design Principle: Good design demands a compromise (maintaining

same format)

• Introduce a new type of instruction format

– I-type for data transfer instructions

– Other format was R-type for register computations

• Example: lw $t0, 32($s2)

35

op

$s2

$t0

18

rs

8

rt

32

16 bit number

• Where's the compromise? (To maintain same length, we settled

with introducing another format RATHER that having the same

format but working with varying lengths)

26

Machine Language

27

So far:

• Instruction

Meaning

add $s1,$s2,$s3

sub $s1,$s2,$s3

and $s1,$s2,$s3

lw $s1,100($s2)

sw $s1,100($s2)

bne $s4,$s5,L

beq $s4,$s5,L

j Label

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = $s2 and $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

Next instr. is at Label if $s4 ° $s5

Next instr. is at Label if $s4 = $s5

Next instr. is at Label

• Formats:

R

op

rs

rt

rd

shamt

funct

I

op

rs

rt

16 bit address

J

op

26 bit address

28

Constants

• Small constants are used quite frequently (50% of operands)

e.g.,

A = A + 5;

B = B + 1;

C = C - 18;

• Design Principle: Make the common fast

– put 'typical constants' in memory and load them.

– create hard-wired registers (like $zero) for constants like zero.

addi $t0, $zero, 100

add $t0, $t1, $zero

29

Assembly Language vs. Machine Language

• Assembly provides convenient symbolic representation

– much easier than writing down numbers

– e.g., destination first

• Machine language is the underlying reality

– e.g., destination is no longer first

• Assembly can provide 'pseudo-instructions'

– e.g., “move $t0, $t1” exists only in Assembly

– would be implemented using “add $t0,$t1,$zero”

• When considering performance you should count real

instructions

30

Pseudo-instructions

• The MIPS assembler supports several pseudo-instructions:

– not directly supported in hardware

– implemented using one or more supported instructions

– simplify assembly language programming and translation

• For example, the pseudo-instruction

move $t0, $t1

is implemented as

add $t0, $zero, $t1

• The pseudo-instruction

blt $s0, $s1, Else

is implemented as

slt $at, $s0, $s1

bne $at, $zero, Else

It is safer to use labels, rather than constants, when implementing

branches. Why?

31

Other Issues

• Things we are not going to cover

sign and zero-extension

handling larger constants

support for procedures

linkers, loaders, memory layout

stacks, frames, recursion

manipulating strings and pointers

interrupts and exceptions

system calls and conventions

• We've focused on architectural issues

– basics of MIPS assembly language and machine code

32

Miscellaneous MIPS Instructions

• break

– A breakpoint trap occurs, transfers control to exception handler

• syscall

– A system trap occurs, transfers control to exception handler

• coprocessor instructions

– Provide support for floating point

• TLB instructions

– Provide support for virtual memory

• return from exception

– Used after an exception is generated to restore control to user

• load word left/right

– Supports misaligned word loads

• store word left/right

– Supports misaligned word stores

• All MIPS R2000 Instructions are given in Appendix A.10

33

Alternative Architectures

• Design alternative:

– provide more powerful operations

– goal is to reduce number of instructions executed

– danger is a slower cycle time and/or a higher CPI

• Sometimes referred to as “RISC vs. CISC” Reduced vs.

Complex Instruction Set Computer.

– virtually all new instruction sets since 1982 have been RISC

– VAX: minimize code size, make assembly language easy

instructions from 1 to 54 bytes long!

34

PowerPC

• Indexed addressing

– example:

lw $t1,$a0+$s3

– What do we have to do in MIPS?

#$t1=Memory[$a0+$s3]

• Update addressing

– update a register as part of load (for marching through arrays)

– example: lwu $t0,4($s3)

#$t0=Memory[$s3+4];$s3=$s3+4

– What do we have to do in MIPS?

• Others:

– load multiple/store multiple

– a special counter register “bc Loop”

decrement counter, if not 0 goto loop

35

80x86

•

•

•

•

•

1978: The Intel 8086 is announced (16 bit architecture)

1980: The 8087 floating point coprocessor is added

1982: The 80286 increases address space to 24 bits, + instructions

1985: The 80386 extends to 32 bits, new addressing modes

1989-1995: The 80486, Pentium, Pentium Pro add a few

instructions

(mostly designed for higher performance)

• 1997: MMX is added

“This history illustrates the impact of the “golden handcuffs” of compatibility

“adding new features as someone might add clothing to a packed bag”

“an architecture that is difficult to explain and impossible to love”

36

A dominant architecture: 80x86

• See your textbook for a more detailed description

• Complexity:

–

–

–

–

Instructions from 1 to 17 bytes long

one operand must act as both a source and destination

one operand can come from memory

complex addressing modes

e.g., “base or scaled index with 8 or 32 bit displacement”

• Saving grace:

– the most frequently used instructions are not too difficult to build

– compilers avoid the portions of the architecture that are slow

“what the 80x86 lacks in style is made up in quantity,

making it beautiful from the right perspective”

37

Summary

• Instruction complexity is only one variable

– lower instruction count vs. higher CPI / lower clock rate

• Design Principles:

–

–

–

–

simplicity favors regularity

smaller is faster

good design demands compromise

make the common case fast

• Instruction set architecture

– a very important abstraction indeed!

38

To summarize: MIPS Instructions

MIPS operands

Name

32 registers

Example

Comments

$s0-$s7, $t0-$t9, $zero, Fast locations for data. In MIPS, data must be in registers to perform

$a0-$a3, $v0-$v1, $gp,

arithmetic. MIPS register $zero always equals 0. Register $at is

$fp, $sp, $ra, $at

reserved for the assembler to handle large constants.

Memory[0],

Accessed only by data transfer instructions. MIPS uses byte addresses, so

30

2 memory Memory[4], ...,

sequential words differ by 4. Memory holds data structures, such as arrays,

words

and spilled registers, such as those saved on procedure calls.

Memory[4294967292]

add

MIPS assembly language

Example

Meaning

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; data in registers

$s1 = $s2 + 100

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

Used to add constants

Category

Arithmetic

Instruction

addi $s1, $s2, 100

lw $s1, 100($s2)

load word

sw $s1, 100($s2)

store word

lb $s1, 100($s2)

load byte

sb $s1, 100($s2)

store byte

load upper immediate lui $s1, 100

add immediate

Data transfer

Conditional

branch

Unconditional jump

$s1 = 100 * 2

16

Comments

Word from memory to register

Word from register to memory

Byte from memory to register

Byte from register to memory

Loads constant in upper 16 bits

branch on equal

beq

$s1, $s2, 25

if ($s1 == $s2) go to

PC + 4 + 100

Equal test; PC-relative branch

branch on not equal

bne

$s1, $s2, 25

if ($s1 != $s2) go to

PC + 4 + 100

Not equal test; PC-relative

set on less than

slt

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; for beq, bne

set less than

immediate

slti

jump

j

jr

jal

jump register

jump and link

$s1, $s2, 100 if ($s2 < 100) $s1 = 1;

Compare less than constant

else $s1 = 0

2500

$ra

2500

Jump to target address

go to 10000

For switch, procedure return

go to $ra

$ra = PC + 4; go to 10000 For procedure call

39

To summarize: Policy of Use Conventions

Name Register number

$zero

0

$v0-$v1

2-3

$a0-$a3

4-7

$t0-$t7

8-15

$s0-$s7

16-23

$t8-$t9

24-25

$gp

28

$sp

29

$fp

30

$ra

31

Usage

the constant value 0

values for results and expression evaluation

arguments

temporaries

saved

more temporaries

global pointer

stack pointer

frame pointer

return address

40

To summarize: MIPS Addressing Modes

1. Immediate addressing

op

rs

rt

Immediate

2. Register addressing

op

rs

rt

rd

...

funct

Registers

Register

3. Base addressing

op

rs

rt

Memory

Address

+

Register

Byte

Halfword

Word

4. PC-relative addressing

op

rs

rt

Memory

Address

PC

+

Word

5. Pseudodirect addressing

op

Address

PC

Memory

Word

41