Here - Cale Rauch

advertisement

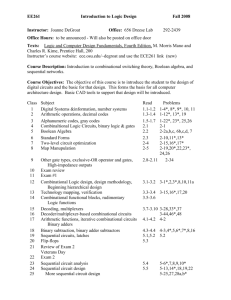

Raider High School School Board Proposal Engineering & Technology Education A Secondary Level Program Developed and taught by Cale Rauch & Alex Egan Raider High School Proposal Presentation Given: April 30, 2014 1 Table Of Contents: Installment I: Mission Statement & Goals Installment II: Course / Program Structure Installment III: Semester Offerings Installment IV: Course Descriptions Installment V: Sample Class Outline Installment VI: Facility Redesign 2 Installment I: Mission Statement & Goals Mission Statement: The Engineering & Technology Education program of Raider High School seeks to increase the technological and engineering knowledge of the students in an efficient way. This will be done through developing 21st century real-world interests, responsibilities, and skills within the students. Goals of the Program: - Describe social, ethical, and environmental impacts associated with the use of technology by increasing technological knowledge Develop a general interest of Engineering & Technology - in modern society Show and demonstrate responsibilities from a real-world technology perspective Encourage students to apply design / production principles to solve engineering and technological problems. Allow students to explore technology and engineering-related careers. Develop professionalism within the technology field to immerse students within the field Enhance, extend, and improve upon any previous knowledge within different fields of technological endeavors. 3 Installment II: Course / Program Structure Project Lead the Way: Introduction to Engineering and Design Principles Of Engineering Civil Engineering & Architecture Computer Integrated Manufacturing Engineering Design & Development Digital Electronics Aerospace Engineering Technology / Manufacturing / Productions: Introduction to Manufacturing Technology Systems Cisco Systems: Introduction to Transportation Technology Enterprises Technology & Society Cisco I Cisco II 4 Installment III: Semester Offerings Teacher 1: Alex Period Teacher 2: Cale SEMESTER 1 SEMESTER 2 SEMESTER 1 SEMESTER 2 IED POE TECH ENTER TECH & SOC PREP PREP DE DE INTRO MAN INTRO MAN PREP PREP INTRO TRANS INTRO TRANS CISCO I CISCO II TECH SYS CIVIL ENGIN COMP INT MAN COMP INT MAN ENGIN DES ENGIN DES AERO ENGIN AERO ENGIN 1 2 3 4 5 6 5 Installment IV: Course Descriptions Course Title: Introduction to Engineering & Design Course Number: TE100 (CRN: 4812) Prerequisites: None Course-length: 18 Weeks Description: This course is designed for the student interested in an engineering related field of study. The major focus of this course is to expose students to the design process, research and analysis, teamwork, various communication methods, engineering standards, and technical documentation. Through hands-on projects, students apply engineering standards while documenting their work in design. Students use industry standard 3D modeling software to help design solutions to solve proposed problems, document their work using an engineer’s notebook, and communicate solutions to peers and members of the professional community. The course assumes no previous knowledge, but students should be concurrently enrolled in mathematics and science courses. Course Title: Principles of Engineering Course Number: TE200 (CRN: 4814) Prerequisites: Introduction to Engineering & Design Course-length: 18 Weeks Description: Principles Of Engineering (POE) is a high school-level survey course of engineering. The course exposes students to some of the major concepts that they will encounter in a postsecondary engineering course of study. Students have an opportunity to investigate engineering and high tech career POE gives students the opportunity to develop skills and understanding of course concepts through activity-, project-, and problem-based (APPB) learning. Used in combination with a teaming approach, APPB learning challenges students to continually hone their interpersonal skills, creative abilities, and problem solving skills based upon engineering concepts. It also allows students to develop strategies to enable and direct their own learning, which is the ultimate goal of education. 6 Course Title: Computer Integrated Manufacturing Course Number: TE201 (CRN: 4812) Prerequisites: Introduction to Engineering & Design Course-length: 36 Weeks Description: Computer Integrated Manufacturing is a specialized course within the Engineering Academy. This course teaches the fundamentals of computerized manufacturing technology. It builds on the solid-modeling skills developed in the Introduction to Engineering Design Course. Students use 3-D computer software to solve design problems. They assess their solutions through the relationship of design, function and materials, modify their designs, and use prototyping equipment to produce 3-D models. This course can be taken concurrently with Digital Electronics and articulates for college credit. (Prerequisite: Principles of Engineering and Introduction to Engineering Design) Course Title: Civil Engineering & Architecture Course Number: TE300 (CRN: 4812) Prerequisites: Introduction to Engineering & Design, Principles of Engineering and/or Computer Integrated Manufacturing Course-length: 18 Weeks Description: The major focus of this course is completing long-term projects that involve the development of property sites. As students learn about various aspects of civil engineering and architecture, they apply what they learn to the design and development of a property. The course provides teachers and students freedom to develop the property as a simulation or to students to model the experiences that civil engineers and architects face. Students work in teams, exploring hands-on activities and projects to learn the characteristics of civil engineering and architecture. In addition, students use 3D design software to help them design solutions to solve major course projects. Students learn about documenting their project, solving problems, and communicating their solutions to their peers and members of the professional community of civil engineering and architecture. 7 Course Title: Engineering Design & Development Course Number: TE301 (CRN: 4812) Prerequisites: Introduction to Engineering & Design, Principles of Engineering and/or Computer Integrated Manufacturing Course-length: 36 Weeks Description: Students work as part of a team to develop a solution to a technical problem of your choosing. Challenge yourself with one of those “don’t you hate it when...” issues of the world and try to solve it. Or see a need here at TCD, your home high school, or your community and find a way to meet that need. Research, design, test, and construct your solution or recommendations, then present it to industry or community partners. You and your team will use what you’ve already learned to guide you through the process of design and product development. Who knows? You may solve a problem that has stumped others! Course Title: Digital Electronics Course Number: TE302 (CRN: 4826) Prerequisites: Introduction to Engineering & Design, Principles of Engineering and/or Computer Integrated Manufacturing Course-length: 36 Weeks Description: Digital Electronics TM is the study of electronic circuits that are used to process and control digital signals. In contrast to analog electronics, where information is represented by a continuously varying voltage, digital signals are represented by two discreet voltages or logic levels. This distinction allows for greater signal speed and storage capabilities and has revolutionized the world electronics. Digital electronics is the foundation of all modern electronic devices such as cellular phones, MP3 players, laptop computers, digital cameras, high definition televisions, etc. 8 Course Title: Aerospace Engineering Course Number: TE303 (CRN: 4826) Prerequisites: Introduction to Engineering & Design, Principles of Engineering and/or Computer Integrated Manufacturing Course-length: 36 Weeks Description: Aerospace Engineering (AE) is the study of the engineering discipline which develops new technologies for use in aviation, defense systems, and space exploration. The course explores the evolution of flight, flight fundamentals, navigation and control, aerospace materials, propulsion, space travel, orbital mechanics, ergonomics, remotely operated systems and related careers. In addition, the course presents alternative applications for aerospace engineering concepts. Course Title: Introduction to Manufacturing Course Number: TE400 (CRN: 4700) Prerequisites: None Course-length: 36 Weeks Description: This course provides students with ways of analyzing manufacturing systems in terms of material flow and storage, information flow, capacities, and times and durations of events. Fundamental topics covered include probability, inventory and queuing models, forecasting, optimization, process analysis, and linear and dynamic systems. This course also covers factory planning and scheduling topics including flow planning, bottleneck characterization, buffer and batch-size tactics, seasonal planning, and dynamic behavior of production systems. 9 Course Title: Introduction to Transportation Course Number: TE401 (CRN: 4701) Prerequisites: None Course-length: 36 Weeks Description: Focuses on fundamental principles of transportation systems, introduces transportation systems components and networks, and addresses how one invests in and operates them effectively. The tie between transportation and related systems is emphasized. Course Title: Technology Systems Course Number: TE500 (CRN: 4700) Prerequisites: None Course-length: 18 Weeks Description: Focuses on systems throughout technology, such as transportation, water-systems, air-systems, and others. This course ties the knot between many fields of study throughout technology, and with what this school offers for other courses. Course Title: Technology Enterprises Course Number: TE501 (CRN: 4806) Prerequisites: None Course-length: 18 Weeks Description: Synthesis course that allows students to apply technology and managerial principles in organizing, financing, and operation a company to produce a product, structure, or service. In a competitive marketplace, today’s enterprises must be developed and operated in an efficient manner. This class will focus on these areas by allowing students to structure and operate a real-life enterprise in a classroom environment. The students will: identify human needs and wants; obtain resources; apply “produce-develop-use” activities to make artifacts and services: and, assess their impacts on individuals, society, and the environment. 10 Course Title: Technology and Society Course Number: TE502 (CRN: 4804) Prerequisites: None Course-length: 18 Weeks Description: This course considers technological change from historical, artistic, and philosophical perspectives and its effect on human needs and concerns. Emphasis is placed on the causes and consequences of technological change. Upon completion, students should be able to critically evaluate the implications of technology. Course Title: Cisco I Course Number: TE600 (CRN: 5000) Prerequisites: None Course-length: 18 Weeks Description: Students will dive into the world of networking at its core. Implementations such as switching, routing, Local-access, cabling, and others will be discussed in detail. Course Title: Cisco II Course Number: TE601 (CRN: 5001) Prerequisites: Cisco I Course-length: 18 Weeks Description: This advanced CISCO course is the second installation of the two classes offered within the curriculum. The focus is to gain a better grip within the networking field, implement new ideas, build advanced topologies, and design networks fluidly. 11 Course Description Bibliography: No Author. "PLTW – Introduction to Engineering Design." Columbia Area Career Center. National Communication Association, n.d. Web. 29 Apr. 2014. http://career-center.org/careerpaths/engineering-industrialtechnology/project-lead-the-way/pltw-introduction-to-engineering-design/ Cahoon, and Bernstein. "Principles of Engineering (PLTW)." Severna Park High School. School World, 2014. Web. 29 Apr. 2014. http://www.myteacherpages.com/webpages/sphsteched/index.cfm?subpage =245799 No Author. “COMPUTER INTEGRATED MANUFACTURING (PLTW) SYLLABUS.” Hazelwood School District. Project Lead The Way. Wed, 29 Apr. 2014. Pg1. No Author. "Technology Education & Engineering / PLTW Civil Engineering & Architecture." Wappingers Central School District. John Jay High School, 2014. Web. 29 Apr. 2014. http://www.wappingersschools.org/page/6955 No Author. "Engineering Design & Development (EDD) - PLTW." Technology Center of Dupage. Schoolwires Inc., 2014. Web. 29 Apr. 2014. http://www.tcdupage.org/Domain/215 No Author. "Aerospace Engineering (AE)." Technology Center of Dupage. Schoolwires Inc., 2014. Web. 29 Apr. 2014. http://www.tcdupage.org/Page/1220 No Author. "Digital Electronics." CourseSites. Blackboard, 2014. Web. 29 Apr. 2014. https://www.coursesites.com/webapps/Bb-sites-course-creationBBLEARN/handleSelfEnrollment.htmlx?course_id=_279504_1 No Author. "Introduction to Manufacturing Systems." MIT OpenCourseWare. OCW Consortium, 2014. Web. 29 Apr. 2014. http://ocw.mit.edu/courses/mechanical-engineering/2-854-introduction-tomanufacturing-systems-fall-2010/ No Author. "Introduction to Transportation Systems." MIT OpenCourseWare. OCW Consortium, 2014. Web. 29 Apr. 2014. http://ocw.mit.edu/courses/civil-andenvironmental-engineering/1-201j-introduction-to-transportation-systems-fall2006/ No Author. "Greensburg Community School Corporation Curriculum." Greensburg.k12. N.p., 2014. Web. 29 Apr. 2014. http://www.greensburg.k12.in.us/gchs/Curriculum/Industrial%20Technology/ Technology%20Enterprise%20Curriculum.pdf No Author. “Technology and Society.” Central Carolina Community College. 2014. Web. 29 Apr. 2014. http://www.cccc.edu/instruction/slympany/ 12 Installment V: Sample Class Outline The following is an example breakdown of a development / build of a Digital Electronics Course. A Sample Unit for this course will be included. This is meant to shed light on what is to be expected within future curriculum/coursedevelopments of the Engineering and Technology Education program. High School Name: Raider High School Course Name: Digital Electronics Topics that are exclusive to the class: Fundamentals of Analog and Digital Electronics Combinational Logic Sequential Logic Microcontrollers Ideal Textbooks for the class: Digital Electronics (Robert Dueck)- Publication Date: September 20, 2011 | ISBN-10: 1439060002 | ISBN-13: 978-1439060001 | Edition: 1 Grob: Basic Electronics (Electronics Books Series) (Bernard Grob): Publication Date: January 27, 1997 | ISBN-10: 002802253X | ISBN-13: 9780028022536 | Edition: 8 Major units of instruction within the class 36-Week Unit 1: Fundamentals of Analog and Digital Electronics (30 [32] Total Days) Unit 2: Combinational Logic (60 Total Days) Unit 3: Sequential Logic (60 [56] Total Days) Unit 4: Microcontrollers (30 [29] Total Days) [] = Projected/Predicted Day-Count () = Needed Day Count *All will be adjusted as need-be based on student needs, school days, work-loads, and other elements. 177 total 13 Sample Unit: *INTRODUCTION The class in which is featuring this unit is called Digital Electronics by Project Lead the Way. The unit being covered for the remainder of the project will be Unit 2: Combinational Logic. This Unit will be 60 days in total, and cover the following: - Lesson 2.1: Introduction to AOI Logic (20 days) Lesson 2.2: Introduction to NAND and NOR Logic (14 days) Lesson 2.3: Date of Birth Design (9 days) Lesson 2.4: Specific Combinational Logic Circuits & Misc. Topics (10 days) Lesson 2.5: Programmable Logic - Combinational (7 days) Each lesson-set contains academic-learning, project, quiz/test, work, and review days. This is a very project-based class; therefore some lesson-sets contain an entire project throughout the lesson. The lessons get progressively more “difficult” as the semester progresses due to the knowledge building on itself. Building upon previous knowledge will be stressed throughout the class due to its importance. *OBJECTIVES Lesson 2.1: Introduction to AOI Logic - - - - Lesson-sets 2.1.0-2.1.1: Combinational Logic Design Processes - Day 1 o Students will understand a broad scope of what they will be learning over the next 60 days. o Students will develop comprehensive knowledge of vocabulary within this part of the unit. Lesson-set 2.1.2: Binary Numbers Conversion - Day 2 o Students will understand the binary number systems for base ten and base two conversion factors. o Students will develop the first part of the knowledge required to begin the “Majority Vote” project assigned on Day1. Lesson-set 2.1.3: Truth Tables Logic Expressions - Day 3 o Students will understand truth tables and Boolean expressions basic diagrams demonstrated to them throughout the lesson. o Students will develop the first part of the knowledge required to begin the “Majority Vote” project assigned on Day1. Lesson-set 2.1.4: Work Day & AOI Logic Analysis - Days 4 - 5 o Students will work on assignments at hand and proceed to complete either part or all of the assignments. 14 - - - - - - - - - - - - o Students will understand how to analyze, form, troubleshoot, and breakdown an AOI circuit. Lesson-set 2.1.5: AOI Logic Implementation - Day 6 o Students will understand how to design and implement an AOI logic circuit from a Sum-Of-Products (SOP) logic expression. o Students will understand how to design and implement an AOI logic circuit from a Product-Of-Sums (POS) logic expression. Review and Work Day for Quiz - Day 7 o Students will ask questions about any place within the previous lessons that need any clarification. o Students will work on assignments or projects at hand and proceed to complete either part or all of the assignments. Quiz Day: 2.1.0-2.1.5 - Day 8 o Students will work on and complete the quiz by the end of class. Lesson-set 2.1.6: Boolean Algebra - Day 9 o Students will be able to implement Boolean theorems through electronic circuitry equations and diagrams. Project work day: Majority Vote Project - Day 10 o Students will complete steps 3 and 4 of the Majority Vote Project by the end of class. Lesson-set 2.1.7: DeMorgan’s Theorems - Day 11 o Students will be able to implement DeMorgan’s theorems within truth tables and electronic circuitry equation environments. Project work day: Majority Vote Project - Day 12 o Students will complete step 4 of the Majority Vote Project and have the DeMorgan assignment started or finished by the end of class. Project work day: Majority Vote Project - Day 13 o Students will have step 5 of the Majority Vote Project finished by the end of class. Project work day: Majority Vote Project - Day 14 o Students will have step 6 of the Majority Vote Project finished by the end of class. Project work day: Majority Vote Project - Day 15 o Students will have step 7 of the Majority Vote Project finished by the end of class. Project work day: Majority Vote Project - Day 16 o Students will have step 8 of the Majority Vote Project finished by the end of class. Project Wrap-up day: Majority Vote Project - Day 17 o Students will have successfully completed the Majority Vote Project, and conclusion paper. Review Day: Boolean - Day 18 o Students will absorb sufficient knowledge of Boolean Algebra to better themselves, and perform well on the quiz. Review Day: DeMorgan - Day 19 o Students will absorb sufficient knowledge of DeMorgan’s Theorem to better themselves, and perform well on the quiz. 15 - Quiz Day: 2.1.6-2.1.7 - Day 20 o Students will work on and complete the quiz by the end of class. Lesson 2.2: Introduction to NAND & NOR Logic - - - - - Lesson-sets 2.2.0-2.2.1: KMapping - Days 21 - 22 o Students will be able to implement KMapping. o Students will be able to implement, understand, read, design, integrate, and break down KMapping. Lesson-set 2.2.2: NAND - Days 23 - 24 o Students will be able to implement, understand, read, design, integrate, and break down the Universal Gate - NAND. Lesson-set 2.2.3: NOR - Days 25 - 26 o Students will be able to implement, understand, read, design, integrate, and break down the Universal Gate - NOR. Lesson-set 2.2.4: Logic Conversions - Days 27 - 28 o Students will be able to use the Logic Converter efficiently within the Multi-SIM environment. o Students finish the SIM-portion of the assignment by the end of class. Review Day - Day 29 o Students will absorb sufficient knowledge of KMapping, NAND, and NOR Logic to better themselves, and perform well on the quiz. Quiz Day - Day 30 o Students will work on and complete the quiz by the end of class. Lesson-set 2.2.5: Fireplace Control Circuit PROJECT - Days 31 - 34 o Students will begin work on the Fireplace Control Circuit project, and make progress. o Students will work on the Fireplace Control Circuit project, and make progress. o Students will work on the project and will have everything turned into me for grading by the end of class. Lesson 2.3: Date Of Birth Project - - Lesson-sets 2.3.0-2.3.1: Seven Segment Displays - Days 35 - 36 o Students will understand how to design and implement using seven-segment displays. o Students will utilize, design, and implement using seven-segment displays. Lesson-set 2.3.2: Date of Birth PROJECT - Days 37 - 43 o Students will understand the design implementations they will need to be utilizing throughout the project at hand. This will allow them to effectively begin working on the assignment after the lecture and for the rest of the class. o Students will work on the Date Of Birth project, and make progress. o Students will finish and turn the project in by the end of class. Lesson 2.4: Specific Combinational Logic Circuits - - Lesson-sets 2.4.0-2.4.1: Octal Hexadecimal - Days 44 - 45 o Students will understand the relationships and correlations between Binary, Octal, and Hex. Lesson-set 2.4.2: XOR & NOR Adders - Days 46 - 47 16 Students will understand the basic functions and ways to implement XOR, XNOR, and binary Adders. o They will make progress or finish the activity at hand. Lesson-set 2.4.3: Twos Complement Arithmetic - Days 48 - 49 o Students will understand the relationships and correlations with twos complement. Lesson-set 2.4.4: Multiplexers & Demultiplexers - Days 50 - 51 o Students will understand the basic functions of the multiplexer and demultiplexer - and the integration thereof. Review Day - Day 52 o Students will absorb sufficient knowledge of the reviewed material in order to better themselves, and perform well on the quiz. Quiz Day - Day 53 o Students will work on and complete the quiz by the end of class. o - - - Lesson 2.5: Programmable Logic-Combinational - - Lesson-sets 2.5.0-2.5.1: Programmable Logic - Days 54 - 55 o Students will begin work on the 2 activities at hand and will make progress until the end of class. Students will develop an understanding for programmable logic devices using the simulation software and tutorials. Lesson-set 2.5.2: Date Of Birth with PLD - Days 56 - 57 o Students will begin the DOBPLD project and make progress by the end of class. Lesson-set 2.5.3: Copier Jam Detector PROJECT - Days 58 - 60 o Students will understand the design implementations they will need to be utilizing throughout the project at hand. This will allow them to effectively begin working on the assignment after the lecture and for the rest of the class. o Students will continue to make progress on the project for the rest of the class. o Students will finish the project during class and turn it in for a grade. o *ALIGNMENT WITH ACADEMIC STANDARDS Standard-sets being used within the unit: Technology Student Organization (TSA) & STEM Integration Technology Education Standards: Link Indiana Department Of Education (DOE) - Technology Education Content Standards, 2006 edition: Link Lesson 2.1: Introduction to AOI Logic: TSA: 3, 7, 8, 9, 10, 11, 12, 13, 16 DOE: 2, 3, 4, 7, 8, 9, 10, 11, 12, 13 17 Lesson 2.2: Introduction to NAND and NOR Logic: TSA: 3, 7, 8, 9, 10, 11, 12, 13, 16 DOE: 2, 3, 4, 7, 8, 9, 10, 11, 12, 13 Lesson 2.3: Date of Birth Design TSA: 3, 7, 8, 9, 10, 11, 12, 13, 16 DOE: 2, 3, 4, 5, 7, 8, 9, 10, 11, 12, 13, 14, 18 Lesson 2.4: specific Combinational Logic Circuits & Misc TSA: 3, 7, 8, 9, 10, 11, 12, 13, 16 DOE: 2, 3, 4, 7, 8, 9, 10, 11, 12, 13, 14, 18 Lesson 2.5: Programmable Logic – Combinational: TSA: 3, 7, 8, 9, 10, 11, 12, 13, 16 DOE: 2, 3, 4, 7, 8, 9, 10, 11, 12, 13, 14 TSA Standards List: Standard 3: Students will develop an understanding of the relationships among technologies and the connections between technology and other fields of study. Standard 7: Students will develop an understanding of the influence of technology on history. Standard 8: Students will develop an understanding of the attributes of design. Standard 9: Students will develop an understanding of engineering design. Standard 10: Students will develop an understanding of the role of troubleshooting research and development, invention and innovation, and experimentation in problem solving. Standard 11: Students will develop abilities to apply the design process. Standard 12: Students will develop abilities to use and maintain technological products and systems. Standard 13: Students will develop abilities to assess the impact of products and systems. 18 Standard 16: Students will develop an understanding of and be able to select and use energy and power technologies. DOE Standards List: Standard 2: Describe technology as a system with inputs, processes, ouputs, impacts, and feedback Standard 3: Understand the integrated relationship of technology with other academic fields, particularly language arts, math, science, and social studies. Standard 4: Describe technology as it is applied in the context of communication, construction, design, manufacturing, transportation, and related technologies. Standard 5: Work cooperatively and productivity in groups to deign and use technology to solve technological problems. Standard 7: Develop and refine alternate solutions that address technological needs and opportunities. Standard 8: Evaluate and select appropriate solutions that address technological needs and opportunities. Standard 9:Apply engineering principles when planning, developing, implementing, and analyzing technological solutions. Standard 10: Specify solutions to stated needs and opportunities using appropriate technical means. Standard 11: Select the appropriate resources needed to produce and operate communication, construction, manufacturing, transportation, and other technological systems and artifacts. Standard 12: Select the appropriate processes need to produce or operate products, structures, and systems. Standard 13: Efficiently use appropriate processes to produce communication, construction, manufacturing, transportation, and related devices and systems. Standard 14: Appropriately operate technological devices and systems. Standard 18: Properly dispose or recondition worn out and obsolete technological devices. 19 *CONTENT OUTLINE Lesson 2.1: Introduction to AOI Logic An understanding of the binary number system and its relationship to the decimal number system is essential in the combinational logic design process. The first step in designing a combinational logic circuit is to translate a set of design specifications into a truth table. A truth table describes the behavior of a combinational logic design by listing all possible input combinations and the desired output for each. Logic expressions can be derived from a given truth table; likewise, a truth table can be constructed from a given logic expression. All logic expressions can be expressed in one of two forms: sum-of-products (SOP) or products of sum (POS). All logic expressions, whether simplified or not, can be implemented using AND, OR, & Inverter Gates. There is a formal design process for translating a set of design specifications into a functional combinational logic circuit. Lesson 2.2: Introduction to NAND and NOR Logic Karnaugh Mapping is a graphical technique for simplifying logic expressions containing two, three, and four variables. A don’t care condition is a situations where the design specifications “don’t care” what the output is for one or more input conditions. Don’t care conditions in K-Maps can lead to significantly simpler logic expressions and circuit implementations. A NAND gate is considered a universal gate because it can be used to implement an AND gate, OR gate, and an inverter gate. Any combinational logic expression can be implemented using only NAND gates. A NOR gate is considered a universal gate because it can be used to implement an AND gate, OR gate, and an inverter gate. Any combinational logic expression can be implemented using only NOR gates. There is a formal design process for translating a set of design specifications into a functional combinational logic circuit implement with NAND or NOR gates. Combinational logic designs implemented with NAND gates or NOR gates will typically require fewer Integrated Circuits (IC) than AOI equivalent implementations. Lesson 2.3: Date of Birth Design 20 Seven-segment displays are used to display the digits 0-9 as well as some alpha characters. The two varieties of seven-segment displays are common cathode and common anode. Any combinational logic expression can be implemented with AOI, NAND, or NOR logic. A formal design process exists for translating a set of design specifications into a functional combinational logic circuit. Lesson 2.4: Specific Comb Logic Circuits & Misc. Topics An understanding of the hexadecimal and octal number systems and their relationship to the decimal number system is necessary for comprehension of digital electronics. XOR and XNOR gates can be used to implement combinational logic circuits, but their primary intended purpose is for implementing binary adder circuits. The addition of two binary numbers of any bit length can be accomplished by cascading one half-adder with one or more full adders. Multiplexer/de-multiplexer pairs are most frequently used when a single connection must be shared between multiple inputs and multiple outputs. Electronics displays that use multiple seven-segment display utilize demultiplexers to significantly reduce the amount of power required to operate the display. Two’s complement arithmetic is the most commonly used method for handling negative numbers in digital electronics. Lesson 2.5: Programmable Logic – Combinational Engineers and technicians use Circuit Design Software to enter and synthesize digital designs into programmable logic devices. Programmable logic devices can be used to implement combinational logic circuits. Circuits implemented with programmable logic devices require significantly less wiring than discrete logic, but they typically require a dedicated printed circuit board to hold the device. Programmable logic devices can be used to implement any combinational logic circuits but are best suited for larger, more complex designs. 21 *DAILY SCHEDULE 2.1 - Introduction to AOI Logic Day 1: Combinational Logic Design Processes Day 2: Binary Numbers Conversion Day 3: Truth Tables Logic Expressions Day 4: Work Day for Majority Vote Project Steps 1 & 2 Day 5: AOI Logic Analysis Day 6: AOI Logic Implementation Day 7: Work Day & Review for Quiz Day 8: Quiz (2.1.0-2.1.5) Day 9: Boolean Algebra Day 10: Work Day for Majority Vote Project Steps 3 & 4 Day 11: DeMoegan’s Theorems Day 12: Work Day for Majority Vote Project Step 4 Catch-up & DeMorgan’s Theorems Day 13: Work Day for Majority Vote Project Step 5 Day 14: Work Day for Majority Vote Project Step 6 Day 15: Work Day for Majority Vote Project Step 7 Day 16: Work Day for Majority Vote Project Step 8 Day 17: Wrap-up for Majority Vote Project Day 18: Review Day 1: Boolean Day 19: Review Day 2: DeMorgan Day 20: Quiz (2.1.6-2.1.7) 2.2 - Introduction to NAND & NOR Logic 22 Days 21-22: KMapping Days 23-34: NAND Days 25-26: NOR Days 27-28: Logic Conversions - MultiSIM Day 29: Review for Quiz Day 30: Quiz (2.2.0-2.2.3) Days 31-34: Fire Place Control Circuit Project 2.3 - Date Of Birth Project NON PLD Days 35-36: Seven Segment Displays Days 37-43: Date of Birth Project 2.4 - Specific Combinational Logic Circuits Days 44-45: Octal & Hexadecimal Days 46-47: XOR & NOR Adders Days 48-49: Twos Complement Arithmetic Days 50-51: Multiplexers & Demultiplexers Day 52: Review for Quiz Day 53: Quiz (2.4.0-2.4.4) 2.5 - Programmable Logic - Combinational Days 54-55: Programmable Logic Days 56-57: Date of Birth with PLD Days 58-60: Copier Jam Detector Project 23 *CHAPTERS IN TEXTBOOKS THAT ADDRESS THIS CONTENT & ANY ACTIVITES Digital Electronics (Robert Dueck)- Publication Date: September 20, 2011 | ISBN-10: 1439060002 | ISBN-13: 978-1439060001 | Edition: 1 2.1 - Introduction to AOI Logic Chapter 3 o 3.3: The Binary Number System Chapter 4 o 4.1: Basic Logic Functions o 4.3: DeMorgan’s Theorems and Gate Equivalence o 4.6: Integrated Circuit Logic Gates Chapter 5 o 5.1: Boolean Expressions, Logic Diagrams, and Truth Tables o 5.2: Sum-of-Products and Product-of-Sums Forms o 5.3: Simplifying SOP Expressions o 5.5: Simplification by DeMorgan Equivalent Gates 2.2 - Introduction to NAND & NOR Logic Chapter 4 o 4.2: Derived Logic Functions o 4.4: Logic Switches and LED Indicators o 4.5: Enable and Inhibit Properties of Logic Gates Chapter 5 o 5.4: Simplification by the Karnaugh Map Method o 5.6: A General Approach to Logic Circuit Design 2.3 - Date Of Birth Project NON PLD Chapter 6 o 6.1: Decoders o 6.2: Encoders 2.4 - Specific Combinational Logic Circuits Chapter 3 o 3.4: Hexadecimal Numbers Chapter 4 o 4.2: Derived Logic Functions 24 Chapter 6 o 6.3: Multiplexers o 6.4: Demultiplexers 2.5 - Programmable Logic – Combinational Chapter 8 o 8.1: Problem-solving Techniques o 8.2: Sample Application: A Small Calculator o 8.4: Troubleshooting *RESOURCES THAT MIGHT BE REQUIRED FOR ACTIVITES **All lessen-sets need the following: Pencil, Paper, Calculator, and Computer. 2.1 - Introduction to AOI Logic 2.1.1: Majority Vote Project o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS04, 74LS08, & 74LS32) o Jumper Wire 2.1.5: AOI Logic Implementation o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS04, 74LS08, 74LS32) o Jumper Wire 2.2 - Introduction to NAND & NOR Logic 2.2.2: NAND Logic Design o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS00) o Jumper wire 2.2.3: NOR Logic Design o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS02) o Jumper wire 2.2.4: Logic Converter o Circuit Design Software (CDS) 25 2.2.5: Fireplace Control Circuit o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS00 & 74LS02) o Jumper wire 2.3 - Date Of Birth Project NON PLD 2.3.1: Seven Segment Display o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits (74LS04 & 74LS32) o Common Cathode Seven -Segment Display o Jumper Wire 2.3.2: Date Of Birth Project o Circuit Design Software (CDS) o Digital Logic Board (DLB) o Integrated Circuits 74LS00 74LS02 74LS04 74LS08 74LS10 74LS11 74LS27 74LS32 o Common Cathode Seven-Segment Display o Resistors and Jumper Wire 2.4 - Specific Combinational Logic Circuits 2.4.2: XOR, XNOR, and Binary Adders o Circuit Design Software (CDS) 2.4.4: Multiplexers & De-Multiplexers o Circuit Design Software (CDS) 2.5 - Programmable Logic – Combinational 2.5.1: Programmable Logic Tutorial o Circuit Design Software (CDS) o Xilinx Programming Software (XPS) 26 o Digital Logic Board (DLB) 2.5.2: Date of Birth with a PLD o Engineering notebook o Circuit Design Software (CDS) o Xilinx Programming Software o Digital Logic Board (DLB) 2.5.3: Copier Jam Detector o Engineering notebook o Circuit Design Software (CDS) o Xilinx Programming Software (XPS) o Digital Logic Board (DLB) o Fischertechnik® Paper Jam Detector Kit o Variable power supply o Jumper wire 2.5.3V: Copier Jam Detector Design o Engineering notebook o Circuit Design Software (CDS) o Xilinx Programming Software (XPS) o Digital Logic Board (DLB) o VEX® Paper Jam Detector Kit o Jumper wire o 15K and 22K resistors o Piezoelectric Buzzer (optional) *EVALUATION SCHEME Primary Points: Homework-Activities: 170pts – 19% Lab-Activities: 195pts – 22% Projects: 340pts – 38% Quizzes: 190pts – 21% Points Possible: 895 Other Points: Participation (2pts per Lab and Project): 26pts – 50% Safety (2pts per Labs and Projects): 26pts – 50% Points Possible: 52 All Points: Homework-Activities: 170pts – 18% Lab-Activities: 195pts – 20% Projects: 340pts – 36% Quizzes: 190pts – 20% 27 Participation (2pts per Lab and Project): 26pts – 3% Safety (2pts per Labs and Projects): 26pts – 3% Points Possible: 947 Break down of points within the class Lesson 2.1.0 - 2.1.7 2.1.0: Key Terms Worksheet………..............10pts 2.1.1: Majority Vote Project……………………..85pts 2.1.2: Binary Numbers Conversion…………..20pts 2.1.3: Truth Tables and Logic Expressions…..20pts 2.1.4: AOI Logic Analysis…………………………….20pts 2.1.5: AOI Logic Implementation……………….25pts Quiz…………………………………………………………60pts 2.1.6: Boolean Algebra……………………………20pts 2.1.7: DeMorgan’s Theorems………………..20pts Quiz………………………………………………………..36 Lesson 2.2.0 - 2.2.5 2.2.1: Karnaugh Mapping…………………....20pts 2.2.2: NAND Logic Design……………………25pts 2.2.3: NOR Logic Design……………………..25pts 2.2.4: Logic Converter……………………….20pts Quiz…………………………………………………56pts 2.2.5: Fireplace Control Circuit Project…85pts Lesson 2.3.0 - 2.3.2 2.3.1: Seven Segment Display…………….25pts 2.3.2: Date Of Birth Project………………..85pts Lesson 2.4.0 - 2.4.4 2.4.1: Octal Hexadecimal Number Systems…20pts 2.4.2: XOR XNOR Binary Adders……………….20pts 2.4.3: Two’s Complement Arithmetic…….20pts 2.4.4: Multiplexers and DeMultiplexers…..20pts Quiz……………………………………………………….38pts Lesson 2.5.0 - 2.5.3 2.5.1: Programming Tutorial…………………………..….5pts 2.5.1: Xilinx Tutorial……………………………………………5tps 2.5.2: Date Of Birth with Programming Logic Device…25pts 2.5.3: Copy Jam Detector Design……………………………..85pts Other Points Participation…………………………..………………2pts per classroom activity/project Classroom Safety Practices/proper use and handling………………….2pts per classroom activity/project 28 Installment VI: Facility Redesign This is the facility redesign done within the area designated for Raider High School’s Engineering and Technology Education program. New designs were created / drawn by the two teachers of the program. The goal was to develop the best use for the spaces available based on the classes that would be taught within. Original outline of available area: 29 RAIDER HIGH SCHOOL TECHNOLOGY & ENGINEERING EDUCATION FACILITY REDESIGN: 30 31 32 33 34 35 36 37