ECE 353 Lesson Slides

advertisement

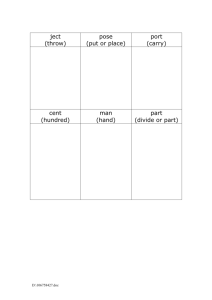

ECE 353 Introduction to Microprocessor Systems Week 9 Michael J. Schulte Topics I/O port basics I/O ports with MSI devices P compatible devices Address decoding for isolated and memory-mapped I/O Conditional I/O 80C188EB integrated I/O unit 82C55A PPI I/O Port Basics I/O subsystems allow CPU to interact with the outside world Input, output, and combined I/O blocks Input ports Byte Word Output ports Byte Word Unconditional I/O MSI I/O Ports Medium Scale Integration (MSI) circuits are available to construct ports Simple byte input ports can be constructed from… Octal buffers Octal registers Simple byte output ports can be constructed from octal latches P Compatible I/O Devices Complex I/O devices typically require complex interface and control logic P compatible I/O devices have the necessary logic built in to the device itself Interface designed to be reasonably compatible with many microprocessor buses Need to add decoding/selection logic Examples Device controllers Used to control complex I/O devices (LCD, disk drives, etc.) Generic model I/O Address Decoding I/O address decoding determines the logical location of the I/O device Isolated I/O Memory-mapped I/O Input vs. output ports Same address does not guarantee same function! Device select pulses Wait states Using the CSU with I/O devices I/O Address Decoding PAL/PLA Decoders Nonspecific I/O strobes /IOW /IOR Linear selection Conventional decoders Device select strobes Cascading (cont.) Conditional I/O Conditional vs. unconditional transfers Hardware example Polling Overhead Flags / semaphores Wait loops Timeouts Software exercise Possible race condition 80C188EB Integrated I/O Unit Port 1 Functions Port 2 Functions Bidirectional pin structure Synchronizer Programming Port Port Port Port Control Register Direction Register Data Latch Register Pin State Register 82C55A Programmable Peripheral Interface (PPI) LSI device providing 24 bits of I/O Logical organization Block diagram Software configurable ports Three modes of operation Mode 0 Basic Input/Output ports Mode 1 Strobed Input/Output Mode 2 Bidirectional data bus Bit set/reset capability Real-World Example Interface the MAX154 8-bit, 4-channel ADC to the 80C188EB Hardware interface Use /GCS0 at I/O address 1000h (CSU) Poll conversion status using Port 2. P2CON / P2DIR / P2LTCH / P2PIN Software interfacing Write a procedure that does an ADC conversion and then reads the ADC value using mode 1 Input: AL = ADC input channel to use (0-3) Output: ADC value returned in AL What about mode 0? Timing? Byte Input Port Example Byte Output Port Example 74HC540/541 74HC573 74HC574 MAX1200 AD7865 Generic Device Controller (Fig 12.3-2) CPU address data control registers status registers A(n-1):0 D7:0 chip select /CS /WR /RD /WE /OE I/O DEVICE data registers TIMING AND CONTROL CLOCK Hitachi HD44780U LCD Controller Port 1 Functions Port 2 Functions Bidirectional Port Pin Port Control Register Port Direction Register Port Data Latch Register Port Pin State Register Conditional I/O Exercise Write a procedure to read data from an input device like the hardware example. Assume that the flag is a READY signal (active high). If the device does not become ready after 1 million polling attempts, return with the carry flag set, otherwise, return with the data in AL and the carry flag cleared. 82C55A Block Diagram 82C55A Modes of Operation 82C55A Mode 1 Input 82C55A Mode 1 Output ChipSelect Start Reg ChipSelect Stop Register Part 1 ChipSelect Stop Register Part 2 Conditional I/O Example D7:0 Q1 Q2 Q3 D1 74HC574 D2 D3 Q4 D4 Q5 D5 Q6 D6 Q7 D7 Q8 D8 INPUT DEVICE CLK < OC A13 A14 A15 /S2 /RD VCC A0 A1 A2 Y0 74HC138 Y1 Y2 E1 Y3 Y4 E2 E3 Y5 Y6 vcc Y7 D7 Q PR D CLK < 74HC125 74HC74 CL Synchronization