International Journal of Science, Engineering and Technology Research (IJSETR)

Volume 1, Issue 1, July 2012

Development of Digital Logic Trainer for Student’s

Experimentation

Myo Su Su Theint1, Zaw Myo Tun2

Abstract– This research work describes design, development

and application of a digital trainer circuit prototyping system,

for student in their digital electronic course. The primary

objective is to design an inexpensive, simple to use device that

could be retained by students, so that they could undertake

digital experimentations. This research paper is one part of the

Digital Trainer Board which contains power supply section,

logic gate section, function generator section and

encoder/decoder section. It mainly concerns with logic gate

section. Logic gate section is aimed to perform basic Boolean

functions, such as AND, OR, NOT, NOR, NAND and so on. All

logic gate circuits are firstly simulated in Multisim simulation

environment and then constructed. After construction, several

tests have been performed and satisfactory results are obtained

Index Terms— Digital logic trainer, AND gate, NAND gate,

NOR gate, OR gate, NOT gate.

I. INTRODUCTION

Digital electronics is now used in all fields of electronics

from computers to digital phones and most industrial

machines and motor vehicles. When prototyping digital

electronic circuits, specific digital input signals are required

to design the digital circuit. To accomplish this task, a

teaching device known as a “Digital Trainer” is utilized. The

purpose of this research work is to provide a method for

students to test digital circuits, with a simple and inexpensive

digital trainer. Digital trainer kit is a self contained set of

electronic circuits that can be interlinked by students to create

working circuits. Component parts cannot be removed or lost

in the classroom and interlinking is performed by short

coloured cables fitted with small insulated alligator clips.

Rapid changes in the field of engineering technology have

increased the need for universities to provide engineering and

engineering technological students with meaningful and

relevant practical experiences. To partial fulfill this need,

study and implementation of digital logic trainer board has

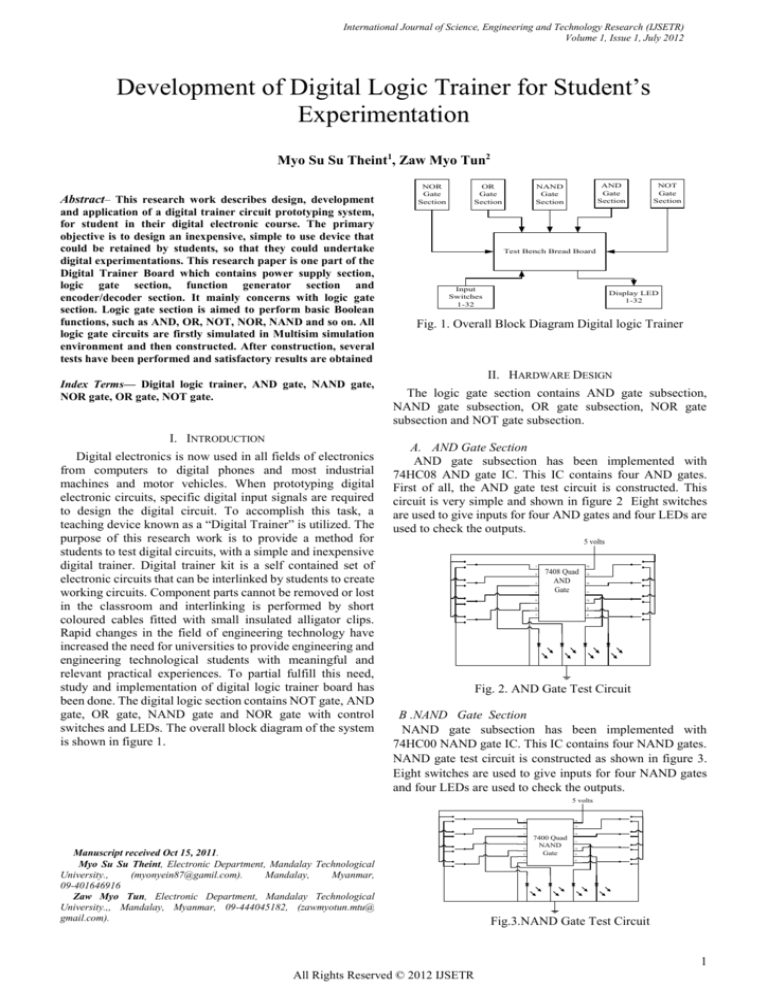

been done. The digital logic section contains NOT gate, AND

gate, OR gate, NAND gate and NOR gate with control

switches and LEDs. The overall block diagram of the system

is shown in figure 1.

NOR

Gate

Section

OR

Gate

Section

AND

Gate

Section

NAND

Gate

Section

NOT

Gate

Section

Test Bench Bread Board

Input

Switches

1-32

Display LED

1-32

Fig. 1. Overall Block Diagram Digital logic Trainer

II. HARDWARE DESIGN

The logic gate section contains AND gate subsection,

NAND gate subsection, OR gate subsection, NOR gate

subsection and NOT gate subsection.

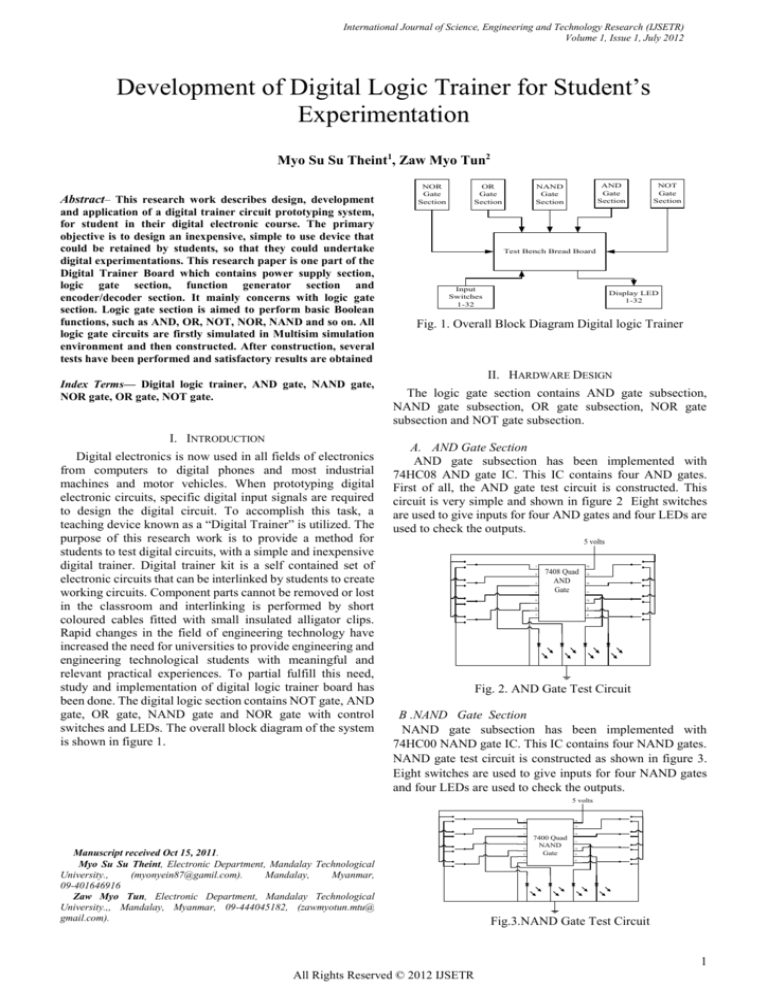

A. AND Gate Section

AND gate subsection has been implemented with

74HC08 AND gate IC. This IC contains four AND gates.

First of all, the AND gate test circuit is constructed. This

circuit is very simple and shown in figure 2 Eight switches

are used to give inputs for four AND gates and four LEDs are

used to check the outputs.

5 volts

1

2

3

4

14

7408 Quad

AND

Gate

13

12

11

5

10

6

9

7

8

Fig. 2. AND Gate Test Circuit

B .NAND Gate Section

NAND gate subsection has been implemented with

74HC00 NAND gate IC. This IC contains four NAND gates.

NAND gate test circuit is constructed as shown in figure 3.

Eight switches are used to give inputs for four NAND gates

and four LEDs are used to check the outputs.

5 volts

1

14

2

13

3

4

Manuscript received Oct 15, 2011.

Myo Su Su Theint, Electronic Department, Mandalay Technological

University.,

(myonyein87@gamil.com).

Mandalay,

Myanmar,

09-401646916

Zaw Myo Tun, Electronic Department, Mandalay Technological

University.,, Mandalay, Myanmar, 09-444045182, (zawmyotun.mtu@

gmail.com).

5

6

7

12

7400 Quad

NAND

Gate

11

10

9

8

Fig.3.NAND Gate Test Circuit

1

All Rights Reserved © 2012 IJSETR

International Journal of Science, Engineering and Technology Research (IJSETR)

Volume 1, Issue 1, July 2012

C.OR Gate Section

OR gate subsection has been implemented with 74HC32

OR gate IC. This IC contains four OR gates. OR gate test

circuit is constructed as shown in figure 4. Eight switches are

used to give inputs for four OR gates and four LEDs are used

to check the outputs.

5 volts

1

14

2

13

3

4

5

6

NOT gate. The circuits for logic gates are simulated

separately.

Figure 7 shows the simulation window for AND gate

logic circuit. Two switches are used as input signals for the

gate and output is tested with Light Emitting Diode (LED).

The trainer uses 7408 Quad AND gate and the results assure

the AND logic.

12

7432 Quad

OR

Gate

11

10

9

7

8

Fig .4. OR Gate Test Circuit

D.NOR Gate Section

NOR gate subsection has been implemented with 74HC02

NOR gate IC. This IC contains four NOR gates. NOR gate

test circuit is constructed as shown in figure 6. Eight switches

are used to give inputs for four NOR gates and four LEDs are

used to check the outputs.

5 volts

1

13

3

5

6

Figure 8 shows the simulation window for OR gate logic

circuit. Two switches are used as input signals for the gate

and output is tested with Light Emitting Diode (LED). The

trainer uses 7432 Quad OR gate and the results assure the OR

logic.

14

2

4

Fig .7. Simulation Window for AND Gate Logic Test Circuit

12

7402 Quad

NOR

Gate

7

11

10

9

8

Fig .5. NOR Gate Circuit Test

E.NOT Gate Section

NOT gate subsection has been implemented with 74HC02

NOT gate IC. This IC contains six NOT gates. NOT gate test

circuit is constructed as shown in figure 6. Six switches are

used to give inputs for six NOR gates and six LEDs are used

to check the outputs.

5 volts

1

16

2

3

4

5

15

7404

NOT

Gate

Fig. 8. Simulation Window for AND Gate Logic Test Circuit

Figure 9 shows the simulation window for NAND gate

logic circuit. Two switches are used as input signals for the

gate and output is tested with Light Emitting Diode (LED).

The trainer uses 7400 Quad NAND gate and the results

assure the NAND logic.

14

13

12

6

11

7

10

8

9

Fig.6.NOT Gate Circuit Test

III. SIMULATION

The simulation of logic gate section has been done with

Multisim Simulation Software. The logic gates used in the

trainer are AND Gate, NAND Gate, OR gate, NOR gate and

Figure.9. Simulation Window for NAND Gate Logic Test

Circuit

2

All Rights Reserved © 2012 IJSETR

International Journal of Science, Engineering and Technology Research (IJSETR)

Volume 1, Issue 1, July 2012

Figure 10 shows the simulation window for NOR gate

logic circuit. Two switches are used as input signals for the

gate and output is tested with Light Emitting Diode (LED).

The trainer uses 7402 Quad NOR gate and the results assure

the NOR logic.

(a)

(b)

Fig .10. Simulation Window for NOR Gate Logic Test

Circuit

Figure 11 shows the simulation window for NOT gate

logic circuit. One only switch is required as input signal for

the gate and output is tested with Light Emitting Diode

(LED). The trainer uses 7404 NOT gate IC and it contains six

NOT gates.

(c)

(d)

Fig.12. Results with AND gate with various inputs; (a) inputs

(1,1), (b) inputs (1,0), (c)inputs (0,0), (d)inputs (0,1)

Table .1 .Truth Table for AND gate

Fig .11. Simulation Window for NOT Gate Logic Test

Circuit

.

Test and results of OR gate implementation is shown in

figure 1to 4. The results satisfy that truth table for

OR gate shown in table 2.

IV. TEST AND RESULTS OF DEVELOPED TRAINER BOARD

Test and results of AND gate implementation is shown in

figure 1to 4. The results satisfy that truth table for

AND gate shown in table 1.

3

All Rights Reserved © 2012 IJSETR

International Journal of Science, Engineering and Technology Research (IJSETR)

Volume 1, Issue 1, July 2012

(a)

Fig .14. Results with NOR gate with various inputs; (a) inputs

(1,1), (b) inputs (1,0), (c)inputs (0,0), (d)inputs (0,1)

Table .3. Truth Table for NOR gate

(c)

(d)

Fig .13. Results with OR gate with various inputs; (a) inputs

(0,0), (b) inputs (0,1), (c)inputs (1,0), (d)inputs (1,1)

Table .2. Truth Table for OR gate

Test and results of NAND gate implementation is shown in

figure 1to 4. The results satisfy that truth table for

NAND gate shown in table 4.

(a)

(b)

Test and results of NOR gate implementation is shown in

figure 1to 4. The results satisfy that truth table for

NOR gate shown in table 3.

(c)

(d)

Fig.15. Results with NAND gate with various inputs; (a)

inputs (0,1), (b) inputs (1,0), (c)inputs (0,0), (d)inputs (1,1)

Table. 4 .Truth Table for NAND gate

(a)

(b)

A

0

0

1

1

B

0

1

0

1

Output

1

1

1

0

Test and results of NOT gate implementation is shown in

figure 1to 4. The results satisfy that truth table for

NOT gate shown in table 5.

(c)

(d)

4

All Rights Reserved © 2012 IJSETR

International Journal of Science, Engineering and Technology Research (IJSETR)

Volume 1, Issue 1, July 2012

[2]

[3]

[4]

[5]

[6]

(a)

Bio-technology, Mohai, India, Microcontroller Based Home

Automation System with Security”

Umm Al-Qura University,Computer Engineering Department,

“ Digital Design Lab Manual

[http://www.elenco.com/digital/analog trainer/XK 550

EcE-2022 Digital Electronics, Department of Electronic

Engineering Department of Technological and Vocational Education,

Ministry of Science and Technology, Myanmar.

www.ALLDATASHEET.com

1972 EXAR Corporation, Datasheet June 1997

(b)

Fig .16 .Results with NOT gate with various inputs; (a) inputs

(0), (b) inputs (1),

Table .5. Truth Table for NOR gate

Fig .17. Complete Circuit Diagram of Digital Logic Gate

Section

V .SUMMARY

The hardware design and software implementation of the

digital logic trainer is described. The simulation results of

logic gate section has been done in Multisim. Thirty-two

switches labeled SW1 to SW32 are applied as an input in this

system.

VI. CONCLUSION

The development of digital logic trainer for students’

experimentation is described. The components required in

trainer board are chosen. The overall circuit for logic trainer

is designed The complete system can be implemented to

perform higher standard than any other commercial products.

An inexpensive and excellent digital trainer board is designed

and implemented. Multisim software is used for simulation.

The results are convenient and simple for students to test.

REFERENCES

[1] Inderpreet Kaur (Asstt.Prof), Rayat and Bahra Institute of Engineering and

5

All Rights Reserved © 2012 IJSETR