Chapter 05

advertisement

Today…

Homework #4 due today.

Lab 4 – Microarchitecture due Friday.

microArch430.exe – Rev 2.1a

Download from website

Report any problems

Questions?

BYU CS 224

Stacks / Interrupts

1

Addressing Modes

01 w/R0 = Symbolic Mode

add.w cnt,r10

; r10 += M[cnt]

Memory

PC

PC

PC

0x501a

0x000c

CPU

Registers

0x501a IR

PC

+2

ADDER

cnt

R10

ALU

*Also called PC Relative address mode

BYU CS 224

Stacks / Interrupts

2

Evaluate Source Operand

Source: Symbolic Mode – label

PC incremented

at end of phase

PC

PC

PC

Use PC to obtain

relative index and

for base register

BYU CS 224

Stacks / Interrupts

3

Quiz 2.2.5

Present the destination operand of the following

instruction to the ALU:

add.w r4,cnt

; M[cnt] += r4

Memory

CPU

Registers

0x5480 IR

PC

PC

PC

PC

0x5480

0x0218

R4

ADDER

cnt

BYU CS 224

ALU

Stacks / Interrupts

4

Quiz 2.2.5 (solution)

Present the destination operand of the following

instruction to the ALU:

add.w r4,cnt

; M[cnt] += r4

Memory

CPU

Registers

0x5480 IR

PC

PC

PC

PC

PC

0x5480

0x0218

Data Bus (+1 cycle)

R4

ADDER

1. Put PC on Address Bus

+2

2. Present ADDER Op1

w/Data Bus

3. Present ADDER OP2

w/PC

4. Put ADDER on Address

Bus

Address Bus

cnt

Data Bus (+1 cycle)

ALU

5. Load ALU OP2 from

Data Bus

6. Increment PC by 2

BYU CS 224

Stacks / Interrupts

5

Quiz 2.2.6

Show how to retrieve a PC-relative destination

operand from memory and present to the ALU:

BYU CS 224

Stacks / Interrupts

6

Quiz 2.2.6 (solution)

Show how to retrieve a PC-relative destination

operand from memory and present to the ALU:

PC

PC

PC

BYU CS 224

Stacks / Interrupts

7

Addressing Modes

Execute Phase: jne func

jne func

; pc += sext(IR[9:0]) << 1

Memory

PC

PC

0x3c21

CPU

Registers

0x3c2a IR

PC

SEXT[9:0]<<1

+2

R2

ADDER

Jump Next

func

COND

ALU

BYU CS 224

Stacks / Interrupts

8

Execute Cycle

Execute Phase: Jump

PC

2’s complement,

sign-extended

Select “COND” to

conditionally change PC

BYU CS 224

Stacks / Interrupts

9

How Can This Be True?

5

13

5

?

13

BYU CS 224

Stacks / Interrupts

10

1996

1998

1982

1995

S05: Stacks / Interrupts

Required:

Recommended:

PM: Ch 7.4, pgs 95-96

Wiki: Stack_(data_structure)

Google "Activation Record"

(Read 1 article)

CS 224

Chapter

Lab

Homework

L01: Warm-up

L02: FSM

HW01

HW02

L03: Blinky

L04: Microarch

L05b: Traffic Light

L06a: Morse Code

HW03

HW04

HW05

HW06

L07b: Morse II

L08a: Life

L09b: Snake

HW07

HW08

HW09

HW10

S00: Introduction

Unit 1: Digital Logic

S01: Data Types

S02: Digital Logic

Unit 2: ISA

S03: ISA

S04: Microarchitecture

S05: Stacks / Interrupts

S06: Assembly

Unit 3: C

S07: C Language

S08: Pointers

S09: Structs

S10: I/O

BYU CS 224

Stacks / Interrupts

12

Learning Outcomes…

The Stack

Subroutines

Subroutine Linkage

Saving Registers

Stack Operations

Activation Records

Recursive Subroutines

Interrupt Stack Usage

BYU CS 224

Stacks / Interrupts

13

Terms…

Activation Record – parameters activated on the stack by a

subroutine call

Callee-Safe – subroutine saves registers used.

Caller-Safe – caller saves registers needing to be saved.

Interrupt – asynchronous subroutine call.

LIFO – Last In First Out, a stack.

Loosely Coupled – all parameters passed as arguments.

Pop – removing top element of stack.

Push – putting an element on a stack

Stack – first in, first out abstract storage data structure.

Stack Pointer – address of stack.

Stong Cohesion – subroutine performs one specific task.

Subroutine – synchronous task or unit.

BYU CS 224

Stacks / Interrupts

14

Levels of Transformation

Problems

Algorithms

Language (Program)

Programmable

Machine (ISA) Architecture

Computer Specific

Microarchitecture

Manufacturer Specific

Circuits

Devices

BYU CS 224

Stacks / Interrupts

15

The Stack

Stacks

Stacks are the fundamental data structure of

computers today.

A stack is a Last In, First Out (LIFO) abstract data

structure.

A true stack is a restricted data structure with two

fundamental operations, namely push and pop.

Elements are removed from a stack in the reverse

order of their addition.

Memory stacks are used for random access of

local variables.

BYU CS 224

Stacks / Interrupts

16

The Stack

MSP430 Stack

Hardware support for stack

Register R1 – Stack Pointer (SP)

Initialized to highest address of available RAM

MSP430G2553 0x0400 (512 bytes)

MSP430F2274 0x0600 (1k bytes)

Stack grows down towards lower memory addresses.

Initialize stack pointer at beginning of program

STACK

.equ

start: mov.w

BYU CS 224

0x0400

; top of stack

#STACK,SP

; init stack pointer

Stacks / Interrupts

17

The Stack

MSP430 Stack

The MSP430 stack is a word structure

Elements of the stack are 16-bit words.

The LSB of the Stack Pointer (SP) is always 0.

The SP points to the last word added to the stack (TOS).

The stack pointer is used by

PUSH – push a value on the stack

POP – pop a value off the stack

CALL – push a return address on the stack

RET – pop a return address off the stack

RETI – pop a return address and status register

off the stack (Chapter 6)

Interrupts – push a return address and status register

on the stack (Chapter 6)

BYU CS 224

Stacks / Interrupts

18

The Stack

Computer Memory – Up or Down?

x0000

xFFFF

Up

Down

Stack

1995

1982

1998

1996

Down

xFFFF

BYU CS 224

Unlike a coin stack, a memory

stack DOES NOT move the

Data in memory, just the

pointer to the top of stack.

TOS

Up

x0000

Stacks / Interrupts

19

Quiz 2.3.1

List the values found in the stack and the value of the

stack pointer after each instruction.

Instructions:

R1

Push #0x0018

Push #0x0025

Push #0x0058

Pop R15

Push #0036

x0280

0x0282

0x0280

TOP

0x027E

0x027C

0x027A

0x0278

BYU CS 224

Stacks / Interrupts

20

Quiz 2.3.1 (solution)

List the values found in the stack and the value of the

stack pointer after each instruction.

Instructions:

Push #0x0018

027E

Pop R15

Push #0036

027A

027C

027A

0x027C

0018

0025

0018

0025

0018

0025

0x027A

0058

TOP 0058

R1

0280

Push #0x0025

Push #0x0058

0x0282

0x0280

0x027E

TOP

0018

TOP

TOP

0036

TOP

0x0278

BYU CS 224

Stacks / Interrupts

21

Subroutines

Subroutines

A subroutine is a program fragment that performs

some useful function.

Subroutines help to organize a program.

Subroutines should have strong cohesion – perform

only one specific task.

Subroutines should be loosely coupled – interfaced

only through parameters (where possible) and be

independent of the remaining code.

Subroutines keep the program smaller

Smaller programs are easier to maintain.

Reduces development costs while increasing reliability.

Fewer bugs – copying code repeats bugs.

Subroutines are often collected into libraries.

BYU CS 224

Stacks / Interrupts

22

Subroutines

The Call / Return Mechanism

Faster programs.

Less overhead.

BYU CS 224

Smaller programs.

Easier to maintain.

Reduces development costs.

Increased reliability.

Fewer bugs do to copying code.

More library friendly.

Stacks / Interrupts

23

Subroutine Linkage

Subroutine Linkage

A subroutine is “called” in assembly using the MSP430

CALL instruction.

The address of the next instruction after the subroutine call

is saved by the processor on the stack.

Parameters are passed to the subroutine in registers

and/or on the stack.

Local variables are created on the stack at the beginning

of the subroutine and popped from the stack just before

returning from the subroutine.

At the end of a subroutine, a RET instruction “pops” the top

value from the stack into the program counter.

BYU CS 224

Stacks / Interrupts

24

Subroutine Linkage

Stack Operations

Single operand instructions:

Mnemonic

Operation

Description

PUSH(.B or .W) src

SP-2SP, src@SP

Push byte/word source on stack

CALL

dsttmp ,SP-2SP,

PC@SP, tmpPC

Subroutine call to destination

TOSSR, SP+2SP

TOSPC, SP+2SP

Return from interrupt

dst

RETI

Emulated instructions:

Mnemonic

Operation

Emulation

Description

RET

@SPPC

SP+2SP

MOV @SP+,PC

Return from subroutine

POP(.B or .W) dst

@SPtemp

SP+2SP

tempdst

MOV(.B or .W) @SP+,dst

Pop byte/word from stack to

destination

BYU CS 224

Stacks / Interrupts

25

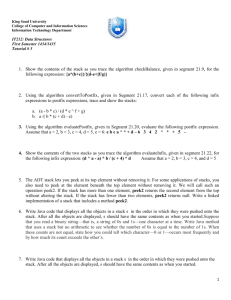

Quiz 2.3.2

1. What is the value of the stack pointer after the second

call to delay?

2. Is there a problem with the program?

start:

mov.w

mov.w

bis.b

#0x0400,SP

#WDTPW+WDTHOLD,&WDTCTL

#0x01,&P1DIR

; P1.0 as output

mainloop:

bis.b

push

call

bic.b

call

jmp

#0x01,&P1OUT

#1000

#delay

#0x01,&P1OUT

#delay

mainloop

; turn on LED

delay:

mov.w

2(sp),r15

; get delay counter

delaylp2:

sub.w

jnz

ret

#1,r15

delaylp2

; delay over?

; n

; y

.sect

.word

.end

".reset"

start

; reset Vector

; start address

BYU CS 224

Stacks / Interrupts

; turn off led

26

Quiz 2.3.2 (solution)

1. What is the value of the stack pointer after the second

call to delay?

2. Is there a problem with the program? Yes! Stack Overflow.

start:

mov.w

mov.w

bis.b

#0x0400,SP

#WDTPW+WDTHOLD,&WDTCTL

...

#0x01,&P1DIR

; P1.0 as output

mainloop:

bis.b

push

call

bic.b

call

jmp

#0x01,&P1OUT

#1000

#delay

#0x01,&P1OUT

#delay

mainloop

0400

; turn on LED

delay:

mov.w

2(sp),r15

; get delay counter

delaylp2:

sub.w

jnz

ret

#1,r15

delaylp2

; delay over?

...

; n

; y

.sect

.word

.end

".reset"

start

; reset Vector

; start address

BYU CS 224

Stacks / Interrupts

→

→ 03fe

R1

R1

; turn off led

03fc

1000

Return

address

03fa

03f0

27

Call

Call Instruction

call #func

; M(--sp) = PC; PC = M(func)

Memory

PC

PC

PC

0x12b0

0x801e

CPU

Registers

0x12b0 IR

PC

SP

fffe

+2

ADDER

func

PC

0x4130

SP

SP

BYU CS 224

ALU

Stacks / Interrupts

28

Subroutine Linkage

Subroutine Call

CALL

Syntax

Operation

Description

Status Bits

Example

BYU CS 224

Subroutine

CALL dst

dst tmp

(SP−2) SP

PC @SP

tmp PC

A subroutine call is made to an address anywhere in

the 64K address space. All addressing modes can

be used. The return address (the address of the

following instruction) is stored on the stack. The call

instruction is a word instruction.

Status bits are not affected.

Stacks / Interrupts

29

Subroutine Linkage

CALL Examples

CALL #EXEC ; Call on label EXEC or immediate address (e.g. #0A4h)

; @PC+ → tmp, SP−2 → SP, PC → @SP, tmp → PC

CALL EXEC ; Call on the address contained in EXEC

; X(PC)→tmp, PC+2→PC, SP−2→SP, PC→@SP, tmp→PC

CALL &EXEC ; Call on the address contained in absolute address EXEC

; X(0)→tmp, PC+2→PC, SP−2→SP, PC→@SP, tmp→PC

CALL R5

; Call on the address contained in R5

; R5→tmp, SP−2→SP, PC→@SP, tmp→PC

CALL @R5 ; Call on the address contained in the word pointed to by R5

; @R5→tmp, SP−2→SP, PC→@SP, tmp→PC

CALL @R5+ ; Call on the address contained in the word pointed to by R5

; and increment pointer in R5.

; @R5+→tmp, SP−2→SP, PC→@SP, tmp→PC

CALL X(R5) ; Call on the address contained in the address pointed to by

; R5 + X (e.g. table with address starting at X)

; X can be an address or a label

; X(R5)→tmp, PC+2→PC, SP−2→SP, PC→@SP, tmp→PC

BYU CS 224

Stacks / Interrupts

30

Subroutine Linkage

Caution…

The destination of branches and calls is used indirectly,

and this means the content of the destination is used as

the address.

Errors occur often when confusing symbolic and

absolute modes:

; Subroutine’s address is stored in MAIN

; Subroutine starts at address MAIN

The real behavior is easily seen when looking to the

branch instruction. It is an emulated instruction using the

MOV instruction:

CALL MAIN

CALL #MAIN

BR MAIN

; Emulated instruction BR

MOV MAIN,PC ; Emulation by MOV instruction

The addressing for the CALL instruction is exactly the

same as for the BR instruction.

BYU CS 224

Stacks / Interrupts

31

Return

Return Instruction

ret

; mov.w @sp+,PC

Memory

0x12b0

0x801e

PC

CPU

Registers

0x4130 IR

PC

SP

0002

+2

ADDER

PC

PC

PC

0x4130

SP

SP

SP

BYU CS 224

ALU

Stacks / Interrupts

32

Subroutine Linkage

Return from Subroutine

RET

Syntax

Operation

Emulation

Description

Status Bits

Example

BYU CS 224

Return from subroutine

RET

@SP→ PC

SP + 2 → SP

MOV @SP+,PC

The return address pushed onto the stack by a CALL

instruction is moved to the program counter. The

program continues at the code address following the

subroutine call.

Status bits are not affected.

Stacks / Interrupts

33

Saving Registers

Saving and Restoring Registers

Called routine -- “callee-save”

Calling routine -- “caller-save”

At beginning of subroutine, save all registers that will be

altered (unless a register is used to return a value to the

calling program or is a scratch register!)

Before returning, restore saved registers in reverse order.

Or, avoid using registers altogether.

If registers need to be preserved across subroutine calls,

the calling program would save those registers before

calling routine and restore upon returning from routine.

Obviously, avoiding the use of registers altogether would be

considered caller-safe.

Values are saved by storing them in memory,

preferably on the stack.

BYU CS 224

Stacks / Interrupts

34

Saving Registers

Caller-Save vs. Callee-Save

Save Registers

call subroutine

Save Registers

subroutine

call subroutine

Restore Registers

BYU CS 224

subroutine

Restore Registers

Stacks / Interrupts

35

Quiz 2.3.3

1. What is wrong (if anything) with the following code?

2. How many times will delay execute for each loop?

3. How long will myDelay delay?

4. Is myDelay callee-save?

loop:

xor.b

call

jmp

#0x01,&P4OUT

#myDelay

loop

myDelay: mov.w

call

call

#0,r15

#delay

#delay

delay:

#1,r15

delay

BYU CS 224

sub.w

jne

ret

Stacks / Interrupts

; toggle LED

; delay some

; repeat

36

Quiz 2.3.3 (answers)

1. What is wrong (if anything) with the following code? No, it’s a tail.

2. How many times will delay execute for each loop? 3 times.

3. How long will myDelay delay?

3 65536 3 cycles.

4. Is myDelay callee-save? No.

loop:

xor.b

call

jmp

#0x01,&P4OUT

#myDelay

loop

myDelay: mov.w

call

call

#0,r15

#delay

#delay

delay:

#1,r15

delay

BYU CS 224

sub.w

jne

ret

Stacks / Interrupts

; toggle LED

; delay some

; repeat

37

Stack Operations

Stack Operations

Single operand instructions:

Mnemonic

Operation

Description

PUSH(.B or .W) src

SP-2SP, src@SP

Push byte/word source on stack

CALL

dsttmp ,SP-2SP,

PC@SP, tmpPC

Subroutine call to destination

TOSSR, SP+2SP

TOSPC, SP+2SP

Return from interrupt

dst

RETI

Emulated instructions:

Mnemonic

Operation

Emulation

Description

RET

@SPPC

SP+2SP

MOV @SP+,PC

Return from subroutine

POP(.B or .W) dst

@SPtemp

SP+2SP

tempdst

MOV(.B or .W) @SP+,dst

Pop byte/word from stack to

destination

BYU CS 224

Stacks / Interrupts

38

Subroutine Linkage

Stack Operations

0400:

0xf820: ...

0xf822: call #subroutine

0xf826: ...

03fe:

03fc:

03fa:

subroutine:

0xf852: push r15

0xf854: push r14

...

03f8:

03f6:

03f4:

03f2:

0xf882: pop r14

0xf884: pop r15

0xf886: ret

BYU CS 224

0xf826

r15

r14

SP

SP

SP

SP

Unprotected!

Stacks / Interrupts

39

Activation Records

Activation Records

A subroutine is activated when called and an activation

record is allocated (pushed) on the stack.

An activation record is a template of the relative positions

of local variables on the stack as defined by the

subroutine.

Return address

Memory for local subroutine variables

Parameters passed to subroutine from caller

Saved registers used in subroutine (callee-save)

A new activation record is created on the stack for each

invocation of a subroutine or function.

A frame pointer indicates the start of the activation record.

When the subroutine ends and returns control to the

caller, the activation record is discarded (popped).

BYU CS 224

Stacks / Interrupts

40

Activation Records

Activation Record Example

DELAY

.cdecls C,"msp430.h"

.equ

(50/8)

; MSP430

reset:

.text

mov.w

mov.w

bis.b

#0x0400,SP

#WDTPW+WDTHOLD,&WDTCTL

#0x01,&P1DIR

;

;

;

;

xor.b

push.w

call

jmp

#0x01,&P1OUT

#DELAY

#delay

mainloop

beginning of code

init stack pointer

stop WDT

set P1.0 as output

Delay Activation Record:

mainloop:

4(SP) = delay

; toggle

P1.0count

; pass

2(SP) delay

= return count

address on stack

; call

subroutine

0(SP) delay

= r15

; delay subroutine: stack usage 4| DELAY | \

;

2| ret | subroutine frame (6 bytes)

;

(SP) => 0| r15 | /

Stack:

delay:

push.w r15

; callee-save

2(SP)

= delay

mov.w

#0,r15

; use

R15

as count

inner counter

0(SP) = return address

delay02:

BYU CS 224

sub.w

jne

sub.w

jne

pop.w

mov.w

ret

#1,r15

delay02

#1,4(SP)

delay02

r15

@SP+,0(SP)

;

;

;

;

;

;

;

.sect

.word

.end

".reset"

reset

; MSP430

reset Vector

Stack:

; start

address

(emply)

Stacks / Interrupts

inner delay over?

n

y, outer done?

nStack:

y,

restore

register(s)

0(SP)

= return address

pop input delay count

return from subroutine

41

Quiz 2.3.4

Change the following code to use a callee-save,

loosely coupled, cohesive subroutine.

start:

.cdecls

.text

mov.w

mov.w

bis.b

C,"msp430.h"

#0x0400,SP

#WDTPW+WDTHOLD,&WDTCTL

#0x01,&P1DIR ; P1.0 as output

mainloop: bis.b

mov.w

#0x01,&P1OUT ; turn on LED

#10000,r15

; delay counter

delaylp1: sub.w

jnz

bic.b

mov.w

#1,r15

delaylp1

#0x01,&P1OUT

#0,r15

; delay over?

;n

; turn off led

; delay counter

delaylp2: sub.w

jnz

mov.w

#1,r15

delaylp2

#0,r15

; delay over?

;n

; delay counter

delaylp3: sub.w

jnz

jmp

#1,r15

delaylp3

mainloop

; delay over?

;n

; y, toggle led

".reset"

start

; reset vector

; start address

.sect

.word

.end

BYU CS 224

Stacks / Interrupts

42

Quiz 2.3.4 (solution)

Change the following code to use a callee-save,

loosely coupled, cohesive subroutine.

start:

.cdecls

.text

mov.w

mov.w

bis.b

C,"msp430.h"

.cdecls

.text

mov.w

mov.w

bis.b

C,"msp430.h"

#0x0400,SP

Cohesive (delays)

#WDTPW+WDTHOLD,&WDTCTL

#0x01,&P1DIR ; P1.0 as output

start:

mainloop: bis.b

mov.w

#0x01,&P1OUT ; turn Loosely

on LED coupled

#10000,r15

; delay counter

; turn on LED

; delay counter

delaylp1: sub.w

jnz

bic.b

mov.w

#1,r15

delaylp1

#0x01,&P1OUT

#0,r15

mainloop: bis.b

#0x01,&P1OUT

mov.w #10000,r15

call

#delay

bic.b

#0x01,&P1OUT

mov.w #0,r15

call

#delay

call

#delay

jmp

mainloop

delay:

r15

; callee save

#1,r15

delaylp1

r15

; delay over?

;n

; y, restore r15

".reset"

start

; reset vector

; start address

delaylp2: sub.w

jnz

mov.w

delaylp3: sub.w

jnz

jmp

.sect

.word

.end

BYU CS 224

#1,r15

delaylp2

#0,r15

; delay over?

;n

; turn off led

; delay counter

; delay over?

;n

; delay counter

push

delaylp1: sub.w

jnz

pop

ret

#1,r15

delaylp3

mainloop

; delay over?

;n

; y, toggle led

".reset"

start

Callee-save

; reset vector

; start address

Stacks / Interrupts

.sect

.word

.end

#0x0400,SP

#WDTPW+WDTHOLD,&WDTCTL

#0x01,&P1DIR ; P1.0 as output

; turn off led

; delay counter

; y, toggle led

43

Recursive Subroutines

Recursive Subroutine

A subroutine that makes a call to itself is said to be a

recursive subroutine.

Recursion allows direct implementation of functions

defined by mathematical induction and recursive divide

and conquer algorithms

Factorial, Fibonacci, summation, data analysis

Tree traversal, binary search

Recursion solves a big problem by solving one or more

smaller problems, and using the solutions of the smaller

problems, to solve the bigger problem.

Reduces duplication of code.

MUST USE STACK!

BYU CS 224

Stacks / Interrupts

44

Interrupts

Interrupts

Execution of a program normally proceeds predictably,

with interrupts being the exception.

An interrupt is an asynchronous signal indicating

something needs attention.

Some event has occurred

Some event has completed

The processing of an interrupt subroutine uses the stack.

Processor stops with it is doing,

stores enough information on the stack to later resume,

executes an interrupt service routine (ISR),

restores saved information from stack (RETI),

and then resumes execution at the point where the

processor was executing before the interrupt.

BYU CS 224

Stacks / Interrupts

45

BYU CS 224

Stacks / Interrupts

46

Interrupts

Interrupt Stack

Item 1

Item 2

SP

Prior to Interrupt

PC

add.w

jnc

add.w

r4,r7

$+4

#1,r6

add.w

r5,r6

xor.b

reti

#1,&P1OUT

Interrupt (hardware)

Item 1

Item 2

PC

SR

SP

Program Counter pushed on stack

Status Register pushed on stack

Interrupt vector moved to PC

Further interrupts disabled

Interrupt flag cleared

PC

Execute Interrupt Service Routine (ISR)

Item 1

Item 2

PC

SR

BYU CS 224

SP

Return from Interrupt (reti)

Status Register popped from stack

Program Counter popped from stack

Stacks / Interrupts

PC

add.w

jnc

add.w

r4,r7

$+4

#1,r6

add.w

r5,r6

47

The Stack

Implementing Stacks in Memory

Unlike a coin stack, in a memory stack, the data does not

move in memory, just the pointer to the top of stack.

Current SP

X0280

x0282

x0280

x027E

x027C

x027A

////

////

////

////

////

Current SP

R1

x027E

x0282

TOP x0280

x027E

x027C

x027A

////

////

#18

////

////

Push #0x0018

BYU CS 224

Current SP

R1

x027A

x0282

x0280

TOP x027E

x027C

x027A

////

////

#18

#25

#58

Push #0x0025

Push #0x0058

Current SP

x027C

R1

x0282

x0280

x027E

x027C

TOP x027A

////

////

#18

#25

#58

Pop R15

Current SP

R1

x027A

x0282

x0280

x027E

TOP x027C

x027A

////

////

#18

#25

#36

R1

TOP

Push #0036

#58 -> R15

Stacks / Interrupts

48

The Stack

Quiz 5.1

List the values found in the stack and the value of the

stack pointer after each instruction.

Current SP

X0280

x0282

x0280

x027E

x027C

x027A

////

////

////

////

////

Current SP

R1

x027E

x0282

TOP x0280

x027E

x027C

x027A

////

////

#18

////

////

Push #0x0018

BYU CS 224

Current SP

R1

x027A

x0282

x0280

TOP x027E

x027C

x027A

////

////

#18

#25

#58

Push #0x0025

Push #0x0058

Current SP

x027C

R1

x0282

x0280

x027E

x027C

TOP x027A

////

////

#18

#25

#58

Pop R15

Current SP

R1

x027A

x0282

x0280

x027E

TOP x027C

x027A

////

////

#18

#25

#36

R1

TOP

Push #0036

#58 -> R15

Stacks / Interrupts

49

The Stack

Implementing Stacks in Memory

Unlike a coin stack, in a memory stack, the data does not

move in memory, just the pointer to the top of stack.

Current SP

X0280

x0282

x0280

x027E

x027C

x027A

////

////

////

////

////

Current SP

R1

x027E

x0282

TOP x0280

x027E

x027C

x027A

////

////

#18

////

////

Push #0x0018

BYU CS 224

Current SP

R1

x027A

x0282

x0280

TOP x027E

x027C

x027A

////

////

#18

#25

#58

Push #0x0025

Push #0x0058

Current SP

x027C

R1

x0282

x0280

x027E

x027C

TOP x027A

////

////

#18

#25

#58

Pop R15

Current SP

R1

x027A

x0282

x0280

x027E

TOP x027C

x027A

////

////

#18

#25

#36

R1

TOP

Push #0036

#58 -> R15

Stacks / Interrupts

50

The Stack

Quiz 5.1 (solution)

List the values found in the stack and the value of the

stack pointer after each instruction.

Push #0x0018

Current SP

X0280

x0282

x0280

x027E

x027C

x027A

////

////

////

////

////

BYU CS 224

Current SP

R1

x027E

x0282

TOP x0280

x027E

x027C

x027A

////

////

#18

////

////

Push #0x0025

Push #0x0058

Pop R15

Current SP

R1

x027A

x0282

x0280

TOP x027E

x027C

x027A

////

////

#18

#25

#58

Current SP

x027C

R1

x0282

x0280

x027E

x027C

TOP x027A

Stacks / Interrupts

////

////

#18

#25

#58

Push #0036

Current SP

R1

x027A

x0282

x0280

x027E

TOP x027C

x027A

////

////

#18

#25

#36

R1

TOP

51

Push

Push Instruction

push.w cnt

; M(--sp) = M(cnt)

Memory

PC

PC

PC

cnt

SP

SP

0x1210

0x000c

0xa5a5

0xa5a5

BYU CS 224

CPU

Registers

0x1210 IR

Data Bus (+1 cycle)

PC

SP

fffe

+2

ADDER

ALU

Stacks / Interrupts

52

Stack Operations

Push Operand

Push word or byte onto stack

PUSH{.W or .B} src

SP − 2 → SP

src → @SP

Description

The stack pointer is decremented by two, then

the source operand is moved to the RAM word

addressed by the stack pointer (TOS).

Status Bits

Status bits are not affected.

Example

PUSH SR

; save SR

PUSH R8

; save R8

PUSH.B &TCDAT

; save data at address

; TCDAT onto stack

Note: The system stack pointer (SP) is always decremented by two,

independent of the byte suffix.

PUSH

Syntax

Operation

BYU CS 224

Stacks / Interrupts

53

Stack Operations

Pop Operand

Pop word or byte from stack to destination

POP{.W or .B} dst

@SP −> temp

SP + 2 −> SP

temp −> dst

Emulation

MOV{.W or .B} @SP+,dst

Description

The stack location pointed to by the stack

pointer (TOS) is moved to the destination. The

stack pointer is incremented by two afterwards.

Status Bits

Status bits are not affected.

Example

POP R7

; Restore R7

POP.B LEO

; The low byte of the stack is

; moved to LEO.

Note: The system stack pointer (SP) is always incremented by two,

independent of the byte suffix.

POP

Syntax

Operation

BYU CS 224

Stacks / Interrupts

54

Learning Objectives…

After discussing microarchitecture and studying the reading

assignments, you should be able to:

Explain what a computer stack is.

Describe how subroutines are used in computer programs.

Program digital I/O using computer ports.

Explain what an activation record is.

Explain how a recursive program uses the stack.

Explain the difference between clock cycles and instruction steps.

BYU CS 224

Stacks / Interrupts

55