Title With Picture Layout - My FIT

advertisement

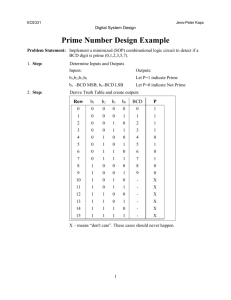

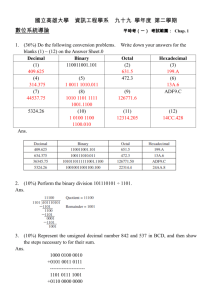

ECE- 1551 DIGITAL LOGIC LECTURE 11: STANDARD CIRCUITS Assistant Prof. Fareena Saqib Florida Institute of Technology Fall 2015, 09/24/2015 Recap Don’t Care Conditons Karnaugh map of Product of Maxterms Exclusive OR Function Code Convertors Excess 3 Agenda Code Convertors BCD to Gray Code Parity Generator BCD to 7 segment display decoder Design Code Converters Binary codes and how to develop code converters. An n-bit binary code is a group of n bits that assumes up to 2^n distinct combinations of 1’s and 0’s. With each combination representing one element o the set that is being coded IN Combinational Logic OUT Binary Codes BCD, Binary representation of decimal numbers. Excess 3 Gray Code ASCII Gray Code- Specification Specification: Excess‐3 is an unweighted code in which each coded combination is obtained from the corresponding binary value plus 3. Application:its selfcomplementing property. Example 9’s complement of 3 is 6 and 6 9’s complement is 3. Excess 3 representation of 3 is 0110 and of 6 is 1001 9’s complement of 3 only requires flipping the bits from 1 to 0 and 0 to 1 (as we did in 1’s complement). Its not true in BCD where 3 is 0011 and 6 is 0110. We cannot directly calculate the 9’s complement. Gray Code: Specification to truth table b3 b2 b1 b0 e3 e2 e1 E0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 1 1 0 0 1 0 1 0 1 1 1 0 1 0 0 1 0 0 0 1 1 0 0 1 0 0 1 1 1 0 1 1 0 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 0 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 1 1 0 0 0 Gray Code:– Minimization using K-maps g0 b3b2 g1 b1b0 00 cd 00 01 11 10 b3b2 b1b0 01 11 10 10 b3b2 01 11 10 11 10 00 01 11 g2 00 b1b0 g0 = b0’ 00 g3 01 11 10 b3b2 00 00 01 11 01 11 10 10 g2 = b2’b1+b2b1’b0 g1 = (b1 xor b0)’ b1b0 00 01 g3 = b3+b2b0+b2b1 Application 2: Parity Generator b3 b2 b1 b0 P0 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 Parity Generator : K-maps P0 b3b2 b1b0 cd 00 10 11 01 00 0 1 0 1 01 11 1 0 1 0 0 1 10 1 0 P0 = ?? 1 1 0 Parity Generator Design circuit. Discussed in class BCD to 7 segment display decoder b3 b2 b1 b0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 a b c d e f g Parity Generator : K-maps a b b1b0 b3b2 cd 00 01 11 10 1 10 11 01 00 1 1 1 1 X X X X 1 1 X X b3b2 b1b0 01 11 X b3b2 01 11 d X 10 c= ?? 10 11 01 00 X X X X X b= ?? b1b0 cd 00 X 10 a= ?? c 10 11 01 00 cd 00 b3b2 b1b0 X X 01 11 X X 10 X X d= ?? 10 11 01 00 cd 00 X X X X Parity Generator : K-maps e f b1b0 b3b2 cd 00 10 11 01 00 1 1 1 1 01 11 0 1 1 1 X X X X 10 1 1 X X b3b2 X f= ?? 10 11 01 00 0 0 1 1 01 11 1 0 0 1 X X X X 10 1 1 X X g= ?? X 10 11 01 00 cd 00 10 b1b0 cd 00 b1b0 01 11 e= ?? g b3b2 X X X X