ALU Control

advertisement

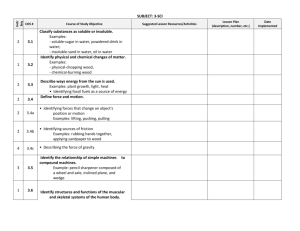

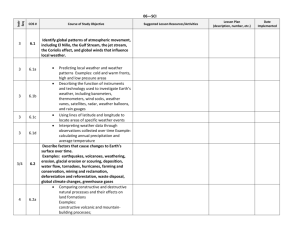

CSE 331 Computer Organization and Design Fall 2006 Week 10 Section 1: Mary Jane Irwin (www.cse.psu.edu/~mji) Section 2: Feihui Li (www.cse.psu.edu/~feli ) Course material on ANGEL: cms.psu.edu [adapted from D. Patterson slides] CSE331 W10.1 Irwin&Li Fall 2006 PSU Head’s Up Last Designing a MIPS single cycle datapath This week’s material week’s material More on single cycle datapath design and exam review - Reading assignment – PH: 5.4, B.8, C.1-C.2 Next week’s material Multicycle MIPS datapath implementation - Reading assignment – PH: 5.5, C.3 Reminders Final Exam is Tuesday, Dec 19, 4:40 to 6:30, 110 Business HW 7 will be due, ~ Nov 30 (by 11:55pm) Quiz 6 will be due, ~ Dec 4 (by 11:55pm) Nov 27 is the late-drop deadline CSE331 W10.2 Irwin&Li Fall 2006 PSU Each MAS (microarchitectural specifications) included Pipeline and block diagrams Textual description of the theory of operation Unit inputs and outputs and protocols governing data transfers Corner cases of the design that were especially tricky New circuits required for implementation Notes on testing and validation The Pentium Chronicles, Colwell, pg. 82 CSE331 W10.3 Irwin&Li Fall 2006 PSU Review: Creating a Datapath from the Parts Assemble the datapath elements, add control lines as needed, and design the control path Fetch, decode and execute each instructions in one clock cycle – single cycle design no datapath resource can be used more than once per instruction, so some must be duplicated (e.g., why we have a separate Instruction Memory and Data Memory) to share datapath elements between two different instruction classes need multiplexors at the input of the shared elements with control lines to do the selection Cycle time is determined by length of the longest path CSE331 W10.4 Irwin&Li Fall 2006 PSU Review: A Simple MIPS Datapath Design Add 4 Shift left 2 RegWrite Instruction Memory PC Read Address Instruction CSE331 W10.5 MemWrite MemtoReg Address ALU Data Memory Read Data Write Data Data 2 Sign 16 Extend PCSrc ALUSrc ALU control ovf zero Read Addr 1 Register Read Read Addr 2 Data 1 File Write Addr Read Write Data Add MemRead 32 Irwin&Li Fall 2006 PSU Adding the Control Selecting the operations to perform (ALU, Register File and Memory read/write) Controlling the flow of data (multiplexor inputs) Information comes from the 32 bits of the instruction 31 25 20 15 10 5 0 Observations R-type: op rs rt rd shamt funct op field always 31 25 20 15 0 in bits 31-26 I-Type: op address offset addr of two rs rt registers to be read are always specified by the rs and rt fields (bits 25-21 and 20-16) base register for lw and sw always in rs (bits 25-21) addr. of register to be written is in one of two places – in rt (bits 20-16) for lw; in rd (bits 15-11) for R-type instructions offset for beq, lw, and sw always in bits 15-0 CSE331 W10.6 Irwin&Li Fall 2006 PSU (Almost) Complete Single Cycle Datapath 0 Add 4 Shift left 2 RegDst Instruction Memory PC Read Address Instr[31-0] RegWrite Sign 16 Extend 1 PCSrc ALUSrc MemWrite MemtoReg ovfzero Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[151 Data 2 Write Data -11] Instr[15-0] Add Address ALU Data Memory Read Data 1 Write Data 0 0 1 32 ALU control MemRead Instr[5-0] ALUOp CSE331 W10.7 Irwin&Li Fall 2006 PSU ALU Control ALU's operation based on instruction type and function code ALU control input 0000 0001 0010 0011 0110 1110 1111 Function and or xor nor add subtract set on less than Notice that we are using different encodings than in the book CSE331 W10.8 Irwin&Li Fall 2006 PSU ALU Control, Con’t Controlling the ALU uses of multiple decoding levels main control unit generates the ALUOp bits ALU control unit generates ALUcontrol bits Instr op lw sw beq add subt and or xor nor slt CSE331 W10.10 funct ALUOp action add xxxxxx 00 add xxxxxx 00 subtract xxxxxx 01 100000 10 add 100010 10 subtract 100100 10 and 100101 10 or 100110 10 xor 100111 10 nor 101010 10 slt ALUcontrol 0110 0110 1110 0110 1110 0000 0001 0010 0011 1111 Irwin&Li Fall 2006 PSU ALU Control Truth Table F5 F4 F3 F2 F1 F0 X X X X X X X X X X X X X X X X X X X X 0 0 0 0 X 0 0 1 0 X 0 1 0 0 X 0 1 0 1 X 0 1 1 0 X 0 1 1 1 X 1 0 1 0 Our ALU m control input ALU Op1 ALU Op0 ALU control3 ALU control2 ALU control1 ALU control0 0 0 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 1 1 0 0 1 1 1 0 0 0 0 0 1 0 1 1 Add/subt Mux control Four, 6-input truth tables CSE331 W10.12 Irwin&Li Fall 2006 PSU ALU Control Logic From the truth table can design the ALU Control logic Instr[3] Instr[2] Instr[1] Instr[0] ALUOp1 ALUOp0 ALUcontrol3 ALUcontrol2 ALUcontrol1 ALUcontrol0 CSE331 W10.13 Irwin&Li Fall 2006 PSU (Almost) Complete Datapath with Control Unit 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.14 Irwin&Li Fall 2006 PSU Main Control Unit Instr RegDst ALUSrc MemReg RegWr MemRd MemWr Branch ALUOp Rtype 000000 lw 100011 sw 101011 beq 000100 Completely determined by the instruction opcode field Note that a multiplexor whose control input is 0 has a definite action, even if it is not used in performing the operation CSE331 W10.16 Irwin&Li Fall 2006 PSU R-type Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.17 Irwin&Li Fall 2006 PSU R-type Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.18 Irwin&Li Fall 2006 PSU Store Word Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.19 Irwin&Li Fall 2006 PSU Store Word Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.20 Irwin&Li Fall 2006 PSU Load Word Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.21 Irwin&Li Fall 2006 PSU Load Word Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.22 Irwin&Li Fall 2006 PSU Branch Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.23 Irwin&Li Fall 2006 PSU Branch Instruction Data/Control Flow 0 Add Add Shift left 2 4 ALUOp 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.24 Irwin&Li Fall 2006 PSU Main Control Unit Instr R-type RegDst ALUSrc MemReg RegWr MemRd MemWr Branch ALUOp 1 0 0 1 0 0 0 10 0 1 1 1 1 0 0 00 X 1 X 0 0 1 0 00 X 0 X 0 0 0 1 01 000000 lw 100011 sw 101011 beq 000100 Setting of the MemRd signal (for R-type, sw, beq) depends on the memory design CSE331 W10.25 Irwin&Li Fall 2006 PSU Control Unit Logic From the truth table can design the Main Control logic Instr[31] Instr[30] Instr[29] Instr[28] Instr[27] Instr[26] R-type lw sw beq RegDst ALUSrc MemtoReg RegWrite MemRead MemWrite Branch ALUOp1 ALUOp0 CSE331 W10.26 Irwin&Li Fall 2006 PSU Review: Handling Jump Operations Jump operation have to replace the lower 28 bits of the PC with the lower 26 bits of the fetched instruction shifted left by 2 bits 31 0 J-Type: op jump target address Add 4 4 Instruction Memory PC CSE331 W10.27 Read Address Shift left 2 Jump address 28 Instruction 26 Irwin&Li Fall 2006 PSU Adding the Jump Operation Instr[25-0] Shift left 2 26 1 28 32 0 PC+4[31-28] 0 Add Jump ALUOp Add Shift left 2 4 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.28 Irwin&Li Fall 2006 PSU Adding the Jump Operation Instr[25-0] Shift left 2 26 1 28 32 0 PC+4[31-28] 0 Add Jump ALUOp Add Shift left 2 4 1 PCSrc Branch MemRead MemtoReg MemWrite Instr[31-26] Control Unit ALUSrc RegWrite RegDst Instruction Memory PC Read Address Instr[31-0] ovf Instr[25-21] Read Addr 1 Register Read Instr[20-16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15-0] Write Data zero ALU Address Data Memory Read Data 1 Write Data 0 0 Data 2 1 Sign 16 Extend 32 ALU control Instr[5-0] CSE331 W10.29 Irwin&Li Fall 2006 PSU Main Control Unit Instr R-type RegDst ALUSrc MemReg RegWr MemRd MemWr Branch ALUOp Jump 1 0 0 1 0 0 0 10 0 0 1 1 1 1 0 0 00 0 X 1 X 0 0 1 0 00 0 X 0 X 0 0 0 1 01 0 X X X 0 0 0 X XX 1 000000 lw 100011 sw 101011 beq 000100 j 000010 Setting of the MemRd signal (for R-type, sw, beq) depends on the memory design CSE331 W10.30 Irwin&Li Fall 2006 PSU Single Cycle Implementation Cycle Time Unfortunately, though simple, the single cycle approach is not used because it is very slow Clock cycle must have the same length for every instruction What is the longest path (slowest instruction)? CSE331 W10.31 Irwin&Li Fall 2006 PSU Instruction Critical Paths Calculate cycle time assuming negligible delays (for muxes, control unit, sign extend, PC access, shift left 2, wires) except: Instruction and Data Memory (4 ns) ALU and adders (2 ns) Register File access (reads or writes) (1 ns) Instr. I Mem Reg Rd Rtype load 4 1 2 4 1 2 4 store 4 1 2 4 beq 4 1 2 jump 4 CSE331 W10.33 ALU Op D Mem Reg Wr Total 1 8 1 12 11 7 4 Irwin&Li Fall 2006 PSU Single Cycle Disadvantages & Advantages the clock cycle inefficiently – the clock cycle must be timed to accommodate the slowest instr Uses especially problematic for more complex instructions like floating point multiply Cycle 1 Cycle 2 Clk lw sw Waste May be wasteful of area since some functional units (e.g., adders) must be duplicated since they can not be shared during a clock cycle but It is simple and easy to understand CSE331 W10.34 Irwin&Li Fall 2006 PSU Where We are Headed Another approach Address Read Data (Instr. or Data) Write Data CSE331 W10.35 Read Addr 1 Register Read Read Addr 2Data 1 File Write Addr Read Write Data Data 2 ALU ALUout Memory A PC B use a “smaller” cycle time have different instructions take different numbers of cycles a “multicycle” datapath IR MDR Irwin&Li Fall 2006 PSU