Read Operation (1)

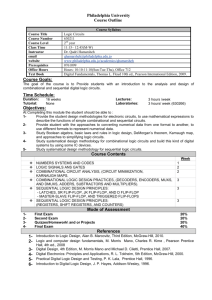

advertisement

CHAPTER 16 Memory Circuits Introduction The 2 major logic classifications are Combinational circuits: Their output depends only on the present value of the input. These circuits do not have memory. Sequential circuits: Logic circuits that incorporate memory are called sequential circuits. Their output depends not only on the present of the input but also on the input’s previous values. 2 approaches to provide memory to a digital circuits: Static sequential circuits: It employs positive feedback to provide a circuit with 2 stable states (bistable state). Dynamic sequential circuits: It utilize a capacitor to store the charge. 2 The Latch The basic memory element, the latch, is shown below. The latch memorizes the external action by staying indefinitely in the acquired state. The state will be changed when it is triggered. Point B is an unstable operating point. By considering the noise that causes positive (negative) small increment at W, the regenerative process will shift the point B upward (downward) to point C (A). Figure 16.1 (a) Basic latch. (b) The latch with the feedback loop opened. (c) Determining the operating point(s) of the latch. 3 Figure 16.2 The SR Flip-Flop The latch together with the triggering circuitry forms a flip-flop. When S/R are raised to 1 simultaneously, Q/Q become 0. However, when S/R return to rest state (S=R=0), the state of flipflop will be undefined. Figure 16.3 (a) The set/reset (SR) flip-flop and (b) its truth table. 5 CMOS Implementation of SR Flip-Flops (1) The clocked version of an SR flip-flop has the 2 cross-coupled inverters as the heart and only NMOS transistors are used in the setrest circuitry (no conducting path between VDD and ground). If the flip-flop stores “0” (Q=0 and Q=1) initially, we wish to set it. 1 Arrange VDD on S input while R is held at 0V. 0 ψ goes high Q5/Q6 conduct and pull the VQ down. If VQ goes below the VTH of Q3/Q4 inverter, it will change state VQ rises. 1 0 The increase of VQ is fed to Q1/Q2 inverter, causing the VQ go down further. Figure 16. 4 CMOS implementation of a clocked SR flip flop. The clock signal is denoted by Φ 6 CMOS Implementation of SR Flip-Flops (2) 1 The normal operation of the flip-flop is based on 2 important assumptions. Transistors Q5/Q6 supply sufficient current to pull the node Q down to a voltage at least slightly below the VTH of Q3/Q4 inverter. 0 The set signal remains high for an interval long enough to cause regeneration to take over the switching process.. 0 1 7 Example 16.1 , p.1310 IDeq >= ID2 VGD=(1/2)VDD>Vt Example 16.1 iC= iDeq - iD2 Figure 16.7 A simpler CMOS implementation of the clocked SR flip-flop. This circuit is popular as the basic cell in the design of static random-access memory (SRAM) chips. D Flip-Flop Circuits (1) The important type of flip-flop, the data (D) flip flop is shown below. When the clock is low, the flip-flop is in the memory (rest) state. As the clock goes high, the flip-flop acquires the logic level that existed on the D-line just before the rising edge of the clock. Such a flip-flop is said to be edge-triggered. Figure 16.8 A block diagram representation of the D flip-flop. 11 D Flip-Flop Circuits (2) A simple implementation of the D flip-flop is shown below and its operation can be described as follows. Non-overlapping clock When ψ is high, the loop is opened, and the input D is connected to input of inverter G1. The capacitance at input of G1 (G2) is charged to the value of D (D). When ψ is low, the input line is isolated and the closed feedback loop makes the latch acquire the state corresponding to the value of D just before ψ went down. Figure 16.9 A simple implementation of the D flip-flop. The circuit in (a) utilizes the two-phase non-overlapping clock whose waveforms are shown in (b). 12 D Flip-Flop Circuits (3) The following is a flip-flop with a master-slave configuration. When ψ1 is high and ψ2 is low, feedback loop of slave is closed and Q remains the value previously stored. Input capacitance of the master latch is charged to the value of D. When ψ1 is low and ψ2 is high, master latch locks the value of D and the node capacitances in the salve are charged to D. When ψ1 goes high again, the slave latch locks the new value of D and output Q=D. Figure 16.10 (a) A master–slave D flip-flop. The switches can be, and usually are, implemented with CMOS transmission gates. (b) Waveforms of the two-phase nonoverlapping clock required. 13 16.2 Types of Semiconductor Memories (1) Computer memory can be divided into 2 types: main memory and mass storage memory. The main memory is usually of the random-access type. A randomaccess memory (RAM) is one in which the time required for writing and reading information is independent of the physical location in which the information is stored. RAMs should be contrasted with serial or sequential memories. Sequential access means that the accessing a piece of information will take a varying amount of time, depending on which piece of information was accessed last. The device may need to seek (e.g. to position the read/write head correctly), or cycle (e.g. to wait for the correct location in a revolving medium to appear below the read/write head). Floppy disk and hard disk are of this type. 14 Types of Semiconductor Memories (2) Source: G. Chou at ProMOS 15 Memory-Chip Organization The bits on a memory chip are addressable either individually or in groups of 4 to 16. 64M-bit chip in which all bits individually addressable is said to be organized as 64M words x 1 bit (64M x 1, it needs a 26-bit address). It can also be organized as 16M words x 4 bits (16M x 4, 24-bit address is required). The bulk of the memory circuit consists of the cells in which the bits are stored. Each memory cell is an electronic circuit capable of storing one bit. Source: ProMOS 16 Innovation in Organization As the number of cells in the array increases, the physical lengths of the word lines and bit lines increase. This has occurred even though for each generation of memory chips, the transistor size has decreased (currently 90 nm feature size are utilized). The net increase in word-line and bit-line length increases their total resistance and capacitance, and slows down the transistor response. This problem has been solved by partitioning the memory chip into a number of blocks. 17 Memory Structure (2M rows x 2N columns) Figure 16.11 A 2M+N -bit memory chip organized as an array of 2M rows × 2N columns. 18 Memory Chip Timing The memory access time is the time between the initialization of a read operation and the appearance of the output data. The memory cycle time is the minimum time allowed between 2 consecutive memory operation. MOS memories have access and cycle times in the range of a few to few hundred nano-seconds. More information about memory chip timing will be discussed in DRAM part. 19 16.3 Random-Access Memory Cells There are basically 2 types of MOS RAM: static and dynamic. Static RAMs (called SRAMs for short) utilize static latches as the storage cells. SRAMs can hold their stored data indefinitely, provided the power supply remains on. Dynamic RAMs (called DRAMs), store the binary data on capacitors, resulting in further reduction in cell area. It requires periodic refreshing to regenerate the data stored on the capacitors. Both static and dynamic RAMs are volatile, that is, they require continuous presence of a power supply. 20 Static Memory Cell Structure A CMOS SRAM memory cell is a flip-flop comprising 2 cross-coupled inverters and 2 access transistors, Q5 and Q6. Figure 16.12 A CMOS SRAM memory cell. 21 Static Memory Cell - Read Operation (1) Relevant parts of the SRAM cell circuit during a read operation when the cell is storing a logic 1. 1 The cell must be designed so that the changes in vQ and vQ are small enough to prevent the flip-flop from changing state during readout. 22 Static Memory Cell - Read Operation (2) Assume the cell is storing a 1 (Q=1/Q=0). B and B lines are precharged to an intermediate voltage, between the low and high values, say VDD (usually VDD/2). When word line is selected and Q5/Q6 are turned on current flow from VDD through Q4/Q6 and onto line B, charging CB. current flow from precharged B line through Q5/Q1 to ground, discharging CB. Voltage across CB will rise and that across C B will fall. A differential voltage develops between line B and line B. Usually only 0.2 V is required for the sense amplifier to detect the presence of a 1 in the cell. The read operation in an SRAM is non-destructive. 23 (W/L)5 ↓, ensure VQ < Vtn of latch Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. ∆t = CB *∆V/I5 (16.7) Large I5→ small ∆t Figure 16.15 Voltage waveforms at various nodes in the SRAM cell during a read-1 operation. Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. 0 1 Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. Static Memory Cell - Write Operation (1) Assume the cell is storing a 1 (Q=1/Q=0) and we wish to write a 0. The B line is lowered to 0 and the B line is raised to VDD. The cell is selected by raising the word line to VDD. Q is being pulled up from 0 toward VDD/2 and Q is being pulled down from VDD toward VDD/2. CQ will discharge faster than CQ will charge because The current (ICQ=I5-I1) that charges the CQ will decrease when current of Q1 increases due to the raised VQ. Body effect of Q5 makes the I5 decreases as VQ increases. * There are some corrections above !! 27 Static Memory Cell - Write Operation (2) The write delay is much smaller than the corresponding component in the read operation. This is because in the write operation, only the small capacitance CQ needs to be charged (discharged), whereas in the read operation, charge (discharge) the much larger capacitances CB is required. 28 To ensure VQ < Vtn, (W/L)4 / (W/L)6 ↓, Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. Dynamic Memory Cell (1) Where can we find DRAMs? 30 Dynamic Memory Cell (2) The memory controller acts like a traffic signal that directs the movement of data across the memory channel. For example, data arriving to the Memory Controller is first stored in the memory modules (2), then is re-read (3) and finally transferred to the processor (4). 31 Dynamic Memory Cell (3) The DRAM cell consists of a single N-MOSFET (access transistor) and a storage capacitor Cs. When the cell is storing a 1, the capacitor is charged to VDD-Vt; when a 0 is stored, the capacitor is discharged to 0V. Because of the leakage effect, the cell must be periodically refreshed. During refresh, the cell content is read and the data bit is re-written, thus restoring the capacitor voltage to a proper value. The refresh operation must be performed every 5-10 ms (currently 64 ms). During refresh, the chip is not available for read/write operation. The interval required to refresh the entire chip is less than 2% between refresh cycles. Figure 16.18 The one-transistor dynamic RAM (DRAM) cell. 32 Dynamic Memory Cell (4) Transistor (電晶體) Capacitor (電容器) Cell (記憶胞) = 1 bit Transistor (電晶體) + Capacitor (電容器) = Cell (記憶胞) 33 Dynamic Memory Cell – Read Operation The bit lines are precharged to VDD/2. The word line is raised to VDD and the access transistors on the selected row will conduct. Small voltage difference will appear on the bit lines. Assume the initial voltage on the cell capacitor be VCS (it is VDD-Vt for a “1” and 0 V for a “0”). For CB is 30 CS, VDD=5V and Vt=1.5V, V (0) = -83 mV and V (1) = 33 mV. VDD is currently 1.8 V for DDR2 DRAM chip. The readout process of DRAM is destructive. Figure 16.19 When the voltage of the selected word line is raised, the transistor conducts, thus connecting the storage capacitor CS to the bit-line capacitance CB. 34 Dynamic Memory Cell – Read Operation cycle time access time 35 16.4 Sense amplifiers and address decoders Peripheral Circuits of A RAM Chip Besides memory cell, other important circuit blocks in a memory chip are peripheral circuits. It contains sense amplifiers and address decoders. The input and output terminals are the same for a sense amplifier. The sense amplifier is required to detect a small signal appearing between B and B and to provide a full-swing signal at B and B. The output of a sense amplifier is directed to the chip I/O pin and at the same time is used to rewrite a data into cell. 36 Operation of A Sense Amplifier (1) Before read operation, B and B line are equal voltage (VDD/2) by turning on Q7/Q8/Q9 through the signal ψp. Q7 helps speed the process by equalizing the initial voltages on the two lines. Initially the latch will be at its unstable equilibrium point. ψs controls whether to turn on the sense amplifier. This is important to conserve power. 37 Operation of A Sense Amplifier (2) When read operation commences, the voltage between the 2 lines develops and the latch will quickly move to one of its 2 equilibrium points. Figure 16.21 38 Operation of A Sense Amplifier (3) What happens to the B line when a particular word line is selected? Dummy cell has a storage capacitor CD = CS. Figure 16.22 An arrangement for obtaining differential operation from the single-ended DRAM cell. Note the dummy cells at the far right and far left. 39 Figure 16.23 Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. Figure 16.24 The active-loaded MOS differential amplifier as a sense amplifier. Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. The Row-Address Decoder The row-address decoder is required to select on of 2M word lines in response to an M-bit address input. For M=3, 1 out of 8 lines is selected using 3 bit address. Each row connects to 3 transistors. During precharge (ψp is low) and all word lines at at VDD. For A2A1A0=011, row 3 is selected and kept at high voltage. precharge and then turn off QP. off 0 off off 1 1 address bits are applied. Figure 16.25 A NOR address decoder in array form. One out of eight lines (row lines) is selected using a 3-bit address. 42 The Column-Address Decoder (1) A column decoder realized by a combination of a NOR decoder and a pass-transistor multiplexer. Figure 16.26 A column decoder realized by a combination of a NOR decoder and a pass-transistor multiplexer. 43 The Column-Address Decoder (2) A tree column decoder. Note that the colored path shows the transistors that are conducting when A0 = 1, A1 = 0, and A2 = 1, the address that results in connecting B5 to the data line. Small number of transistors but with slower speed (relatively large number of series transistors in the signal path). Figure 16.27 A tree column decoder. Note that the colored path shows the transistors that are conducting when A0 = 1, A1 = 0, and A2 = 1, the address that results in connecting B5 to the data line. 44 The Ring Oscillator The ring oscillator is formed by connecting an odd number of inverters in a loop. Note that the rising edge at node 1 propagates through gate 1, 2, and 3 to return inverted after a delay of 3 tp. The circuit oscillates with a period of 6 tp. Figure 16.28 (a) A ring oscillator formed by connecting three inverters in cascade. (Normally at least five inverters are used.) (b) The resulting waveform. Observe that the circuit oscillates with frequency 1/6tP. 45 Figure 16.29 (a) A one-shot or monostable circuit. Utilizing a delay circuit with a delay T and an XOR gate, this circuit provides an output pulse of width T. (b) The delay circuit can be implemented as the cascade of N inverters where N is even, in which case T = NtP . Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. How to Measure Propagation Delay (1) Ring oscillators propagation delays are used to benchmark the performance of CMOS fabrication process. The simplest ring oscillator contains an odd number of cascaded inverters, with the output of the cascade fed back to the input of the inverter chain. In this configuration, the oscillator frequency is completely dependent on the inherent inverter time delay and is therefore not externally controllable. 47 How to Measure Propagation Delay (2) For a ring oscillator, odd-number n (usually n > 5) of inverters are connected in a chain and it will oscillate with period T. Source: K. Banerjee at UC Santa Barbara 48 How to Measure Propagation Delay (3) If the gate delay (CV/I) of a transistor is less than 1 ps, then we call it a TeraHertz transistor. To further improve transistor speed for TeraHertz operation, the following structure will be used. Source: 2001 Si nanotechnology workshop from Intel 49 A MOS ROM The following is a 32 bit (8 words x 4 bit) MOS ROM. The major disadvantage is the static power dissipation. The data stored in the ROMs is determined at the time of fabrication. Figure 16.30 A simple MOS ROM organized as 8 words ×4 bits. 50 Mask-Programmable ROMs and PROMs Mask-programmable ROMs To avoid having to custom-design each ROM from scratch, ROMs are manufactured using a process known as mask programming. MOSFET can be included at all bit locations, but only the gates of those transistors where 0s are to be stored are connected to the word lines. Programmable ROMs PROMs are ROMs that can be programmed by the user, but only once (They are frequently seen in computer games, or such products as electronic dictionaries). A typical PROM comes with all bits reading as 1, burning a fuse during programming causes its bit to read as 0. The memory can be programmed just once after manufacturing by "blowing" the fuses (using a PROM blower), which is an irreversible process. 51 EPROMs (1) Erasable-Programmable ROMs It is a type of computer memory chip that retains its data when its power supply is switched off. Once programmed, an EPROM can be erased only by exposing it to strong ultraviolet light (wavelength=2537A). EPROMs are easily recognizable by the transparent window in the top of the package, through which the silicon chip can be seen, and which permits UV light during erasing. 52 EPROMs (2) Its structure and programming principle are illustrated below. Figure 16.31 (a) Cross section and (b) circuit symbol of the floating-gate transistor used as an EPROM cell. Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. Figure 16.32 Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. Figure 16.33 The floating-gate transistor during programming. Microelectronic Circuits, International Sixth Edition Sedra/Smith Copyright © 2011 by Oxford University Press, Inc. EEPROMs A more versatile PROM is the electrically erasable PROM (EEPROM). As the name implies, an EEPROM can be erased and reprogrammed electrically without the need for ultraviolet illumination. The difference between EPROM and EEPROM lies in the thickness of the insulating layer — in an EPROM it is about 25 nm thick whereas in an EEPROM it is much thinner — typically around 10 nm. This thinner insulating layer allows for lower voltages to be used for programming. 56 Flash Memory Flash memory is a form of non-volatile computer memory that can be electrically erased and reprogrammed. Unlike EEPROM, it is erased and programmed in blocks consisting of multiple locations. Flash memory costs far less than EEPROM and therefore has become the dominant technology wherever a significant amount of non-volatile, solid-state storage is needed. Source: Samsung Electronics 57