PPT - The University of Toledo

advertisement

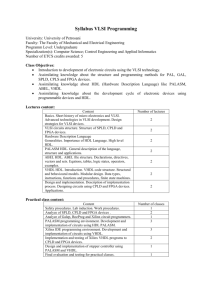

Introduction to HDLs Hardware Description Languages CSET 4650 Field Programmable Logic Devices Dan Solarek Hardware Description Languages Hardware Description Languages, or HDLs, are languages used to design hardware. Similar to procedural programming languages (e.g., C) Digital hardware only An HDL can also be used to describe the functionality of hardware as well as its implementation. Leads to simulation Allows functional verification 2 Hardware Description Languages In electronics, a hardware description language or HDL is any language from a class of computer languages for formal description of digital electronic circuits. An HDL can describe digital circuit's operation its design and tests to verify its operation by means of simulation 3 Hardware Description Languages Describe hardware modules at varying levels of abstraction (more later …) Structural description Textual replacement for schematic Hierarchical composition of modules from primitives Behavioral/functional description Describe what module does, not how Synthesis step generates circuit for module Simulation semantics are included 4 Levels of Design Abstraction Levels of abstraction for VLSI circuit design. Adapted from Michael D. Ciletti. HDLs 5 Why HDLs ? The complexity of logic circuits has increased dramatically in the past few decades Other forms of EDAs are no longer effective HDLs offer a consistent and efficient method for both design and synthesis HDLs are relatively easy to learn 6 Why HDLs ? 7 Why HDLs ? 8 Why HDLs ? 9 Hardware Description Languages The principal feature of a hardware description language is that it contains the capability to describe the function (behavior) of hardware independent of implementation. The great advance with modern HDLs was the recognition that a single language could be used to describe the function of the design and also to describe the implementation. 10 History of HDLs The first HDL was ISP*, invented by C. Gordon Bell and Alan Newell at Carnegie Mellon University (CMU) and described in their book Computer Structures published in 1972. * Instruction-set Processor language Gordon Bell Alan Newell 11 History of HDLs ISP was the first HDL to use the term register-transfer level (RTL). This term came from the use of ISP in describing the behavior of the PDP-8 computer as a set of registers and logical functions describing the transfer of data from source register to destination register. DEC PDP-8 12 History of HDLs Subsequent HDLs included VHSIC HDL (VHDL) which was begun in 1979 Verilog ABEL UDLI which was developed by NTT HiLo, which was the predecessor to Verilog ISP', which was a successor to ISP (implemented by the N-dot simulator). and more … 13 HDLs ISP (circa 1971) - research project at CMU Written by Bell and Newell Simulation, but no synthesis ABEL (circa 1983) - developed by Data-I/O Targeted to programmable logic devices Not good for much more than state machines Verilog (circa 1985) - developed by Gateway (absorbed by Cadence) Similar to Pascal and C Delays is only interaction with simulator Fairly efficient and easy to write IEEE standard 14 HDLs VHDL (circa 1987) - DoD sponsored standard Similar to Ada (emphasis on re-use and maintainability) Simulation semantics visible Very general but can get verbose IEEE standard Updated in 1993 The current trend is to move away from proprietary HDLs and towards the two leading standards, VHDL and Verilog HDL. 15 HDLs vs. Programming Languages An HDL is a standard text-based expression of the temporal behavior (timing) and/or (spatial) circuit structure of an electronic system. In contrast to a software programming language, an HDL's syntax and semantics include explicit notations for expressing time and concurrency which are the primary attributes of hardware. 16 HDLs vs. Programming Languages An HDL is analogous to a software programming language, but with subtle differences. Both types of language are processed by a compiler. An HDL compiler often works in several stages, first producing a logic description file in a proprietary format, then converting that to a logic description file in the industry-standard EDIF format, then converting that to a JEDEC-format file. The JEDEC file contains instructions to a PLD programmer for building logic. Joint Electron Device Engineering Council 17 HDLs vs. Programming Languages Program Structure Instantiation of multiple components of the same type Specify interconnections between modules via schematic Hierarchy of modules Assignment Continuous assignment (logic always produces an output signal) Propagation delay (signals take time) Timing of signals is important (when does a specific signal or set of signals have an effect on the circuit) 18 HDLs vs. Programming Languages Data structures Size explicitly spelled out - no dynamic structures No pointers Parallelism Hardware is naturally parallel (must support multiple threads) Assignments can occur in parallel (not just sequentially) 19 HDLS and Combinational Logic Modules: specification of inputs, outputs, bidirectional, and internal signals Continuous assignment: a gate's output is a function of its inputs at all times (doesn't need to wait to be "called") Propagation delay: concept of time and delay in input affecting gate output Composition: connecting modules together with wires Hierarchy: modules encapsulate functional blocks Specification of don't care conditions (accomplished by setting output to “x”) 20 HDLs and Sequential Logic Flip-Flops Representation of clocks - timing of state changes Asynchronous vs. synchronous FSMs Structural view (FFs separate from combinational logic) Behavioral view (synthesis of sequencers) Data-paths = ALUs + registers Use of arithmetic/logical operators Control of storage elements Parallelism Multiple state machines running in parallel Sequential don't cares 21