Memory Address Register

advertisement

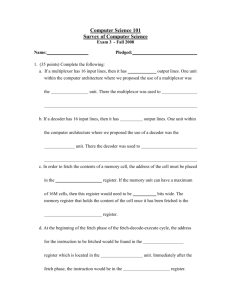

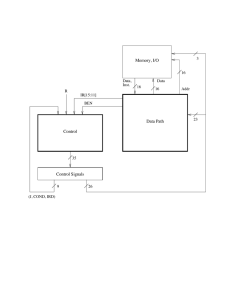

Computer Science 101 Computer Systems Organization MEMORY Pappaw, our puter broke. What’s a man to do? Perfectly clear, huh? I think I’m getting a headache. Von Neumann Architecture Basic Architecture of most computers Four Major Subunits • • • • Memory Input-output Arithmetic-logic unit (ALU) Control Unit Stored Programs Von Neumann Architecture Execution Cycle • Fetch Instruction • Decode • Execute HP Pavilion Media Center Processor speed: 2.8GHz giga- G 1000^3 1024^3 = 2^30 = 1,073,741,824 Hz- cycle per second 2.8 billion cycles per second Major Components HP Pavilion Media Center Bus Speed: 800MHz Front Side Bus Bus Memory Control Unit ALU CPU Input Output Units Memory Stores: Numbers, text, programs, addresses, graphics, sound, video, etc. that are currently in use. Divided into fixed size cells (fixed number of bits). This size is commonly 8 bits, and this 8-bit unit is called a byte. The simple hypothetical lab machine uses 16 bit cells. The lab machine is a simulated version of a very simple, but illustrative computer. HP Pavilion Media Center Memory: 1024MB PC2-4200 DDR2 SDRAM memory (expandable to 2GB) A bit is what the dentist uses to fix your byte? Memory Addresses Each cell has an address, an unsigned integer. All accesses to memory are via a specific address Address Cell Content 0 1 2 00100110 3 10101010 10100110 00111110 Basic Memory Operations Memory Fetch • Given a specific memory address. • Retrieve the content stored at that address. Memory Store • Given a specific memory address and • a specific value, • store the given value in the cell with the specified address. Memory Fetch Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Content: Memory Fetch Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Content: Memory Fetch Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Content: Memory Fetch Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Content: Memory Fetch Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Content: 00111110 Memory Store Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Given Value: 10101010 Memory Store Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Given Value: 10101010 Memory Store Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Given Value: 10101010 Memory Store Address 2002 Cell Content 2003 2004 10100110 2005 10101010 00100110 00111110 Given Address: 2004 Given Value: 10101010 Memory Store Address 2002 Cell Content 2003 2004 10100110 10101010 2005 10101010 00100110 Given Address: 2004 Given Value: 10101010 Memory Facts and Terminology A cell is the minimum unit of access. Access time is same for all cells - Random Access Memory or RAM (nanoseconds billionths of second) ROM - Read only Memory (fetch but not store) Some data items require more than one cell. For example, an instruction might need four cells. Note: ints require 4 cells (bytes) More on Memory All addresses are of some fixed number of bits, say N. Addresses would be 0000…0 0 0000…1 1 … 1111…1 2N – 1 Total of 2N cells Note: This is an application of unsigned numbers. Terminology Storage capacity: • K 210 = 1024 Kilo as in Kb • M 220 = 1,048,576 Mega as in Mb • G 230 = 1,073,741,824 Giga as in Gb Speed • 1 = 1 microsecond = 1 millionth of second • 1 ms = 1 millisecond = 1 thousandth of second • 1 ns = 1 nanosecond = 1 billionth of second Cycle rate: Hertz is cycle per second Memory Registers A register is an extremely fast cell - more expensive than RAM cells - fewer of them - for special purposes. MAR - Memory Address Register - size is same as size of an address - holds the address of the cell to access. MDR - Memory Data Register - size is multiple of RAM cell size - holds content of cell fetched or value to be stored. MAR and Max Memory Size MAR of size N bits gives 2N possible addresses; so up to 2N possible memory locations. HP Pavilion Media Center Memory: 1024MB PC2-4200 DDR2 SDRAM memory (expandable to 2GB) This HP has maximum memory of 2GB or 231; so MAR must be 31 bits. Memory Fetch- More Detail Fetch (address) To obtain data at a given address: • Load address into MAR • Address is decoded and cell is selected • Contents of cell put into MDR Fetch(10110) Address MAR MDR 10110 0011110 Cell Content 10100 00100110 10101 10110 10100110 10111 10101010 00111110 Memory Store- More Detail Store (address,value) To store a given value at a given address: • Load address into MAR • Load value into MDR • Address is decoded and cell is selected • Value from MDR is put into the selected cell Store(10110,11111111) Address MAR MDR 10110 11111111 Cell Content 10100 00100110 10101 10110 10100110 10111 10101010 00111110 11111111 Address Decoding Recall: Decoder has n inputs, 2n outputs, inputs select one output to be 00100110 1, others 0. MAR ---n--- 10100110 2n lines 00111110 10101010 00100110 n to 2n decoder 10100110 00111110 10101010 Address decoding (cont.) Note: If we have 26 bit addresses, this allows for 226 = 64M cells. In the diagram before, the decoder would have 26 input lines and 67,108,864 output lines. That’s a lot of lines. Two-dimensional memory layout Now picture the 64M memory laid out as a 2dimensional grid. There would be 213 rows and 213 columns. Suppose we use half of the address (13 bits) to choose a row and half to choose the column in order to locate the cell. This would use two decoders - one for the row and one for the column. Two-dimensional Memory Layout Here we have 2* 213= 16384 lines as opposed to 67,108,864 as in 1-dimensional MAR 13 13 n to 213 n to 213