Sustainable Computing

advertisement

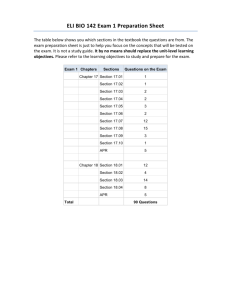

Green Computing Reducing the environmental and economic impact of energy consumption by low-power Integrated Circuit Design Faculty Forum, April 1, 2008 Peiyi Zhao, Ph.D. Department of Mathematics, Computer Science, and Physics Chapman University Overview Integrated Circuits Power Consumption Green Computing Understanding the levels of a Computer Where does the power go? How can we reduce power? Apr. 01, 2008 2 Integrated Circuits The first transistor was built in 1947. The first integrated circuit was invented in 1959. Market driven by military, computer, communications, and consumer needs. Equipment once used by the military are now available on a number of consumer products. Apr. 01, 2008 3 Integrated Circuits are Everywhere Climate Control Lighting Dashboard Display Door Modules Engine Control Fuel Injection Entertainment Chassis Electronics Safety Control Apr. 01, 2008 4 Integrated Circuit Market Apr. 01, 2008 Six billion microcontroller units were shipped in 2004, predicted to be increasing by 10% each year from 20042009 (Instate Inc. market research) Semiconductor annual revenue of 2004 is estimated at US $211.4 billion. 5 Power Consumption Desktop consumption has reached 100 watts Total Personal Computer(400 million) energy usage in 2000 = 26 nuclear power plants Power is the bottleneck of improving the system performance Power consumption is causing serious problems because of excessive heat. Water Cooled Computer (www.water-cooling.com) Apr. 01, 2008 6 Power Consumption of Processor Power Density (W/cm2) 1000 100 Pentium 4 Hot Plate 10 Pentium 3 Pentium 2 Pentium Pro Pentium 1 1980 Apr. 01, 2008 Nuclear Reactor 386 486 1990 2000 2010 7 Power Consumption Apr. 01, 2008 As circuit speed increases, power consumption grows Designing low power circuits has been the most important issue Mobile applications demand long battery life Low power consumption is listed as the second greatest challenge for the industry 8 The Current Situation Energy provisioning is arguably the most important business, geo-political, and societal issue of our time Global Warming is influencing policies and laws which require energy usage and greenhouse emissions to be measured and controlled The cost of energy and increases in IT power requirements present significant expense, supply, and handling challenges for data centers •“Intelligent Energy” Dr. Bernard S. Meyerson, IBM Fellow, VP Strategic Alliances and CTO, IBM Systems & Technology Group, on ASE – Great Energy Efficiency Day, February 14, 2007 - Washington, DC Apr. 01, 2008 9 Power Consumption & Data Centers Where are the web pages you browse? Data Center One single room in Datacenter contains 100 Racks 1 Rack = 5 to 20 kW Contributed to the 2000/2001 California Energy Crisis Internet Client Racks Apr. 01, 2008 Data Center 10 Apr. 01, 2008 200 M tons of CO2= CO2 produced by 40 million cars 11 Atmospheric CO2 concentrations measured at Mauna Loa Observatory. Apr. 01, 2008 12 Cooling the Data Center Flickr.com Current coolants: CFCs and HCFCs = Ozone Depletion The other alternative coolant: HFC = increase in green house emission 1300 times (http://www.cs.virginia.edu/kim/course s/cs771/lectures/CS771-22.ppt) Siberia umw.edu Moving Datacenters to exotic locations(Microsoft -> Cold Siberia, Sun -> underground) Underground Japan Apr. 01, 2008 13 Apr. 01, 2008 14 Energy Usage of Data Centers 2006: $15 Billion for energy usage http://www.westportnow.com Impact of 10% Reduction of Power Consumption of Data Centers • $15b x 10% = $1.5 billion in savings • 200 x 10% = 20 million tons of CO2 • 4 million cars (Number of cars that would have to be taken off the road to reduce the same amount of CO2 emissions.) Apr. 01, 2008 15 Reducing Power Consumption Data centers = huge energy bill + produce CO2 + green house emission + air pollution… Moore’s Law: transistor density doubles every 18 months. “We must reduce power usage. Computing is part of the solution, part of the problem” Source: University of Delaware -- ”Sustainable Computing,” David Douglas, VP, Ecological Responsibility, Sun Microsystems Apr. 01, 2008 16 Green Computing In order to achieve sustainable computing, we need to rethink from a “Green Computing” perspective. Green Computing: Maximize energy efficiency Reduce of the use of hazardous materials such as lead Maximize recyclability of both a defunct product and of any factory waste. “Green Computing” in view of energy efficiency at the nanometer scale - design low power consumption integrated circuits at 180nm and below. Apr. 01, 2008 17 A Perfect “Green Computing” Example A super low-power “processor”: Apr. 01, 2008 800x faster 1000x more memory 3000x less power 18 A super low power “Processor” Modern Processor made by hundreds of PH.D. researchers (The MOS transistor was built from Silicon, the pre-dominant atom in rock and sand, after processed in a high temperature.) Human Brain ( containing 100 billion neurons, each linked to as many as 10,000 other neurons.) Speed 2.0 GHz Equivalent to 1,700 GHz processor Memory 100 GB 100,000 GB 45 mW/cm3 15 mW/cm3 (Source: Oracle Corporation: http://library.thinkquest.org/C0015 01/the_saga/compare.htm, computer vs. brain) Power (Source: UC Berkeley, EE241 class) Apr. 01, 2008 19 What can we do about power? Apr. 01, 2008 Understand all levels of the computer Understand where power is dissipated Think about ways to reduce power usage at all levels 20 The 6 Levels of a Computer Apr. 01, 2008 5 High Level Programming 4 Assembly Language 3 Operating System 2 Instruction Set Architecture 1 Digital Logic 0 Integrated Circuit Software Hardware 21 The Need for Both Sides “The performance of software systems is dramatically affected by how well software designers understand the basic hardware technologies at work in a system. Similarly, hardware designers must understand the far-reaching effects their design decisions have on software applications.” - John Hennessy, President of Stanford University & David Patterson, UC Berkeley, President of ACM “[Students] should know the device, layout, circuit, architecture, algorithm, and system-6 levels.” - Dr. Mehdi Hatamian, V.P, Broadcom, Nov.2006 Apr. 01, 2008 22 The Chapman Approach Apr. 01, 2008 5 High Level Programming 4 Assembly Language 3 Operating System 2 Instruction Set Architecture 1 Digital Logic 0 Integrated Circuit CPSC 230/231, 350, 353, 354, 402, 408 CPSC 250 CPSC 380 CPSC 252 CPSC 330 CPSC 465 23 Where does power go? Apr. 01, 2008 Power Breakdown of an Itanium 2 Processor 24 Processor Clock Power consumption is proportional to clock frequency. Clock frequency: how often the clock changes every second; of course, every change of the clock consumes power. Analogous to how many times the motor spins per second in your car. Traditionally only one edge of the clock is used to process information, and the other edge is ignored. - Figure shows the Clock signal - Rising edge is used while falling clock edge(dot line) is not used for data information processing Apr. 01, 2008 25 Using Double Edge Clocking Using double edge clocking, the clock frequency can be reduced to half. “Low Power clock branch sharing Double-Edge Flip-Flop,” P. Zhao, Jason McNeely, Pradeep Golconda, agdy A. Bayoumi, Kuang W.D, and Robert Barcenas, IEEE Transactions on Very Large Scale Integration (VLSI) Systems,Vol.15, No.3, pp. 338-345, March 2007. Proposed clock branch sharing technique: used least number of clocked transistors to implement double edge clocking efficiently. Conventional Single edge Design: Proposed Design: Apr. 01, 2008 Falling clock edge(dot line) is not used for data information processing Both rising and falling clock edges are used for data information processing, the clock frequency is reduced to half(clock period is doulbed) 26 Potential Savings 33% x 0.5 = 15% Clock Power Usage Savings from Double Edge Usage by using half of the frequency Power Savings $15b x 15% = $2.25b Annual Energy Cost of Data Centers Apr. 01, 2008 Savings Annual Savings 27 Peer Reviewed Journal Publications, Patent for Low Power Consumption Peer Reviewed Journal Publications (all as first author) P. Zhao, T. Darwish, M. Bayoumi, “High Performance and Low Power Conditional Discharge Flip-Flop,” in Institute of Electrical and Electronics Engineers (IEEE) Transactions on Very Large Scale Integration (VLSI) Systems, Vol 12., No. 5, pp. 477-484, May 2004. P. Zhao, Jason McNeely, Pradeep Golconda, Magdy A. Bayoumi, Kuang W.D, and Robert Barcenas, “Low Power Clock Branch Sharing DoubleEdge Triggered Flip-Flop,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems,Vol.15, No.3, pp. 338-345, March 2007. Journal Paper under Revision: P. Zhao, Jason McNeely, G. P. Kumar, Nan Wang, M. Bayoumi, and Robert Barcenas, “Low Power Clocked-pseudo-NMOS Flip-flops for Level Conversion in Dual Supply Systems,” submitted to IEEE Transactions on Very Large Scale Integration (VLSI) Systems under 1st revision. Patent Single transistor clocked flip flop, by P.Zhao, T.Darwish, M.Bayoumi Apr. 01, 2008 28 Student Research Assistance Chapman undergraduate student Robert Barcenas is involved with research and is one of the co-authors of a journal paper Two previous students who worked with me on my project were hired by Intel Apr. 01, 2008 29 Low Power Research Recognition Our research results are comparable to the results from other more well-funded research groups: Competing with: Academy Industry University of California, Davis, Intel Second journal paper (Mar. 2007) University of California, Davis, Intel Third journal paper under 1st revision University of California, Berkeley, Toshiba First journal paper (May 2004) Cited 6 times in Web of Science, Cited 11 times in Google Scholar [accessed Mar.,2008] Citations: three are from peer reviewed journals( IEEE TRANSACTIONS ON VLSI SYSTEMS,, ACM Computing Surveys (CSUR)) and one is from industry (published on the IEEE Transactions). Apr. 01, 2008 Our designs outperformed those of Intel and UC Davis Our designs have attracted industry attention from Toshiba 30 Thank You Apr. 01, 2008 31