ENGR43Lab12

advertisement

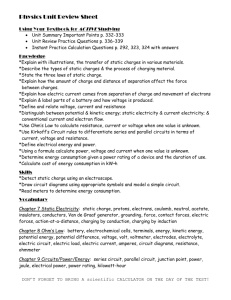

ENGR 43 Lab Activity Student Guide LAB 12 – MOSFET Amplifiers Student Name: ___________________________________________________ Overview Getting Started In this activity the student will characterize the operation of a class A MOSFET amplifier and multiple configurations of a class AB MOSFET multistage amplifier. Lab Activity and Deliverables: It should take students approximately 2 hours to complete the lab activity, and 1 hours of homework time to complete the lab report. Before Starting This Activity Equipment & Supplies This activity assumes that the student has already completed the introduction activities for MultiSim and the NI-ELVIS trainer. Download the following files from the GoogleDocs site or the ENGR 43 course website: E60Lab5-MOSFET.ms10 E60Lab5-BJT.ms10 E54wk5-(1, 2, 3, 4, 5).ms10 ENGR43Lab12.xlsx Item MultiSim and Excel applications NI-ELVIS trainer 2N3904 NPN transistor IRFZ48 MOSFET 100 µF capacitor 1 µF capacitor 100 Ω resistor 1 kΩ resistor 330 kΩ resistor 1 MΩ potentiometer Learning Outcomes For Activity Relevant knowledge (K), skill (S), or attitude (A) student learning outcomes 1 1 1 1 2 3 1 2 1 1 Special Safety Requirements K1. Analyze DC biasing in BJT and MOSFET voltage-divider bias circuits The MultiSim simulation allows you to subject the virtual components to electrical abuse that would damage real components. Do not exceed the maximum ratings for the components when characterizing the components with the NI-ELVIS. If you do not know the published maximum ratings, refer to the manufacturer’s specification sheet for the component. K2. Describe the effect of component values on circuit biasing, gain and distortion. S1. Analyze class A and class AB amplifiers with the MultiSim oscilloscope and distortion analyzer tools. S2. Compare calculated values with measured performance data. Lab Preparation Verify that the NI-ELVIS trainer has the standard proto test board installed, is powered up, and connected via USB to the lab PC. A1. Increase awareness of amplifier circuit characterization and configuration. LAB 11 – Diode Characteristics ENGR 43 Qty 1 © 2012 ENGR 43 Lab Activity Student Guide Task #1 – Class A MOSFET Amplifier Biasing off power, remove the pot from the circuit and measure the resistance of the pot. Enter the value in the Excel table and reconnect the pot in the circuit. 6. Add the jumper to connect the IRFZ48 gate to the voltage divider (the same effect as closing the switch in the simulation). Turn the +10V supply on and measure the DC base voltage. Can you explain what happened? How much “loading effect” does the gate present to the voltage divider? 7. Adjust the pot, if necessary, to restore the DC gate voltage to 4.9 V. Turn off power, remove the pot from the circuit and measure the resistance of the pot. Enter the value in the Excel table and reconnect the pot in the circuit. 8. For comparison, open the E60Lab5BJT.ms10 file in Multisim. Run the simulation. With the switch closed, adjust the pot for 1.2 VDC at Probe 1. Press the space bar to open the switch. Compare the loading effect of the MOSFET circuit with the BJT (bipolar junction transistor) circuit. How does the loading effect of the MOSFET circuit compare with the BJT? 1. Open the E60Lab5-MOSFET.ms10 file in MultiSim. VDD 10V V(p-p): V(dc): V(p-p): V(dc): V(p-p): V(dc): R1 330kΩ Cload V1 50mVpk 1kHz 0° 1µF Probe2,Probe2 J1 Cin Probe4,Probe4 V(p-p): V(dc): RD 1kΩ 1µF Q1 Probe1,Probe1 Key = Space V(p-p): V(dc): Probe5,Probe5 RL 1kΩ IRFZ48N R2 1MΩ 50% Key=A Probe3,Probe3 RS 100Ω CS 100µF Figure 1 2. Note that this simulation uses the Measurement Probe tool to display multiple circuit measurements at the points labeled Probe 1-5. The voltage displayed is relative to the circuit ground. 3. Press the space bar to open the switch, if closed. We want to adjust potentiometer R2 to produce a DC gate bias voltage, VG, of 4.9 V. Calculate the resistance of R2 with the voltage divider formula that will produce 4.9 V, and enter your data on the Excel worksheet. 4. With the switch still open, run the simulation and adjust the potentiometer with the “A” key to get a DC base voltage as close to 4.9 V as possible. Enter the resistance in the Simulation column on the Excel sheet (resistance = 1 MΩ x pot%, for example, at 8% the resistance is 80 kΩ). 5. Construct the circuit on the ELVIS breadboard. Instead of using a switch, use a jumper to make the connection between the voltage divider and the IRFZ48 gate. Leave the jumper disconnected for now. Apply 10 V to the circuit and adjust the pot for 4.9 V. Turn LAB 11 – Diode Characteristics ENGR 43 ________________________________ ________________________________ ________________________________ ________________________________ ________________________________ 9. Optionally, you can replace the MOSFET in your circuit with the 2N3904 NPN transistor to compare the loading effect results. 2 © 2012 ENGR 43 Lab Activity Student Guide Task #2 – Class A MOSFET Amplifier Gain and Bandwidth to find its low-frequency cut-off frequency, and enter your data in the Excel table. 8. Add capacitors, one at a time, in parallel with the input, output, and bypass capacitors to find which one is limiting the low-frequency output. Can you calculate the effect of each of these capacitors? Repeat the simulation and measurements of step 13 for each capacitor. 9. Use the AC Analysis tool in MultiSim to find the high-frequency cut-off frequency, which is defined as the point where the output voltage is 0.707 times the passband output. This is called the “half-power point.” Measure your circuit to find its high-frequency cut-off frequency (if possible), and enter your data in the Excel table. 10. The Miller capacitance, which is the output terminal capacitance reflected back to the input terminal, usually limits the high-frequency limit of a transistor amplifier. This means that as gain increases, more output capacitance is reflected back to the input, reducing the high-frequency response. Find the highfrequency limit when you disconnect the load resistor to increase gain, and remove the source bypass capacitor, to reduce gain. If within the frequency limit of the function generator, measure the high-frequency limit of your circuit on the ELVIS breadboard. 1. Return to the E60Lab5-MOSFET.ms10 file in MultiSim. If you swapped transistors in the optional step 9 of the previous task, put the IRFZ48 MOSFET back in the circuit. 2. With a capacitor in parallel with the source resistor RS, the source resistance is “bypassed” for AC signals. This increases the gain of the amplifier. A basic formula for AC voltage gain, Av, is Av = rDtotal*gm. In this circuit the total AC drain resistance is RD in parallel with RL, or 500 Ω. The transconductance, gm or gfs, is found on the spec sheet for the device. Note that at this operating point, gm may be significantly different than the rated value, which is typically measured near the maximum operating drain voltage and current. The actual at this operating point can be measured on a curve tracer or the NI-ELVIS 3-wire IV analysis VI. 3. Apply the 10 mVpk (20 mVpp) 1 kHz input, measure the output voltage and calculate the gain Av = vout/vin. Enter your value in the Excel table. 4. Check your work by running the simulation (press the space bar to close the switch, if necessary) and measuring the input and output voltages and calculating the gain. 5. Remove the source bypass capacitor, CS. Now the total AC source resistance is RS+ rDS(on). Repeat steps 8, 9 and 10. 6. Replace CS and remove RL. Now the total AC drain resistance is RD. Repeat steps 8, 9, and 10. 7. Use the AC Analysis tool in MultiSim to find the low-frequency cut-off frequency, which is defined as the point where the output voltage is 0.707 times the passband output. This is called the “half-power point.” Measure your circuit LAB 11 – Diode Characteristics ENGR 43 3 © 2012 ENGR 43 Lab Activity Student Guide Task #3 – Class AB MOSFET Push-Pull Follower Circuit 2 Circuit 1 5. Open the file E54wk5-2.ms10. We have added two enhancement-mode MOSFETS (one n-channel, one pchannel) in a push-pull follower, also known as a complementary-symmetry output. 6. Run the simulation and observe the output. Note that the MOSFETs are capable of high current flow, but due to the turn-on characteristics they do not start conducting until the gate voltage reaches almost 4 volts. Note the low output voltage and significant “zero crossing” distortion. Open the distortion analyzer tool, note the distortion, and enter your data in the Excel table. 1. Open the file E54wk5-1.ms10. Note that this op-amp circuit is driving an 8 Ω load, a typical impedance for a speaker. The op-amp is configured as a follower, which provides a voltage gain of 1, but with high input impedance and low output impedance. 2. With a source voltage of 0.1 V pk, compare the input with the output on the oscilloscope. 3. Stop the simulation, increase the signal voltage to 1.0 V, and start the simulation. Note the clipping of the output. This is because we are exceeding the maximum current output capability of the op-amp. 4. Repeat step 3 with a source voltage of 5 V. Note that the output is still significantly clipped. LAB 11 – Diode Characteristics ENGR 43 4 © 2012 ENGR 43 Lab Activity Student Guide Circuit 4 Circuit 3 11. Open the file E54wk5-4.ms10. This circuit uses another technique to reduce distortion: biasing the MOSFETs with the voltage divider network so that the gate voltage of each MOSFET is closer to the turn-on voltage. 12. Run the simulation. Note that the output (channel B) is much closer to the desired sine wave than the non-biased Circuit 2, but without including the MOSFETs in the feedback path the op-amp output is the desired 5 V output, but the zerocrossing errors produced by the MOSFETs are only partially corrected by the biasing network. Open the distortion analyzer tool, note the distortion, and enter your data in the Excel table. 13. Note the DC current flowing through the Vss (negative) supply. Enter the value in the Excel table. 7. Open the file E54wk5-3.ms10. One way to reduce distortion is to put the pushpull follower INSIDE the feedback loop of the op-amp. 8. Run the simulation. Note that the output (channel B) is much closer to the desired sine wave, but the op-amp output has changed significantly in order to compensate for the zero-crossing errors produced by the MOSFETs. Open the distortion analyzer tool, note the distortion, and enter your data in the Excel table. 9. Note the DC current flowing through the Vss (negative) supply. Enter the value in the Excel table. 10. Repeat steps 8 and 9 with a signal source voltage of 0.5 V. Note the effect on the distortion and the waveforms on the scope. Enter your values in the Excel table. LAB 11 – Diode Characteristics ENGR 43 5 © 2012 ENGR 43 Lab Activity Student Guide 14. Repeat steps 12 and 13 with R2 and R3 changed from 2 kΩ to 3 kΩ. Note the effect on the Vss current, the distortion and the waveforms on the scope. Enter your values in the Excel table. 15. Experiment with values of R2 and R3 (keep both the same value) to see the effects on distortion and Vss current. What can you conclude about the relationship between the two? Circuit 5 _________________________________ _________________________________ 16. Open the file E54wk5-5.ms10. This circuit uses MOSFET biasing and feedback. 17. Run the simulation. Open the distortion analyzer tool, note the distortion, and enter your data in the Excel table. 18. Note the DC current flowing through the Vss (negative) supply. Enter the value in the Excel table. 19. Repeat steps 17 and 18 with R2 and R3 changed from 2 kΩ to 3 kΩ. Note the effect on the Vss current, the distortion and the waveforms on the scope. Enter your values in the Excel table. 20. Experiment with values of R2 and R3 (keep both the same value) to see the effects on distortion and Vss current. How do the results differ from circuit 4? ________________________________ _________________________________ _________________________________ _________________________________ LAB 11 – Diode Characteristics ENGR 43 6 © 2012 ENGR 43 Lab Activity Student Guide Deliverable(s) Print your Excel workbook and save it with this activity guide in your Lab Activity Binder. Lab 12 Summary Questions Voltage Divider Bias What causes the voltage divider loading in the MOSFET and BJT class A circuits? How could you choose resistor values to minimize the loading effect in the BJT circuit? (Hint: the bias current needed for the base is the same regardless of the current through R2.) Where would you look to estimate the low-frequency cut-off point for a class A BJT or MOSFET amplifier circuit? Why do BJT transistors have a published specification for base-to collector current gain (beta), while MOSFET transistors have gate-to-drain transconductance (gm) specifications? LAB 11 – Diode Characteristics ENGR 43 7 © 2012 ENGR 43 Lab Activity Student Guide Class AB MOSFET Push-Pull Followers The complementary-symmetry output configuration used in Task 3 is commonly called a “follower.” Why? What is it following? What design goals for an amplifier would restrict the values you could specify for R2 and R3. The first goal would be a maximum allowed distortion value. What are some others? Review the data from Tasks 1, 2, and 3. List some examples of the necessity to specify the test parameters used to collect data to produce reliable and meaningful results. LAB 11 – Diode Characteristics ENGR 43 8 © 2012