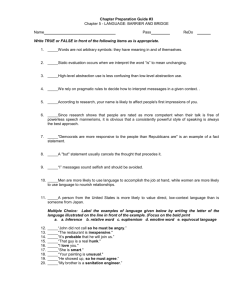

Review of Digital Logic Design - FAMU

advertisement

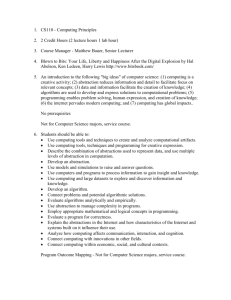

EEL-4746 Microprocessor-based System Design Fall 2004 Semester Dr. Michael P. Frank Announcements Announcements FSU First-Day Mandatory Attendance Policy ECE Course Prerequisite Policy ECE Academic Dishonesty Policy Today’s Agenda Today’s Agenda EEL-4746 Course Outline and Objectives EEL-4746 Best Practices EEL-4746 Software Distribution Design Methodology Design Abstraction EEL-4746 Microprocessor-based System Design Review of Digital Logic Design Course Outline and Objectives 4746 Best Practices Or, How do you get an A in this class? Definition: System Design Process Requirements Specification Conceptualization Analysis Iteration Synthesis Verification Documentation 4746: System Design Process Requirements Specification Given by me: HW, Project, Exam, etc. Conceptualization Developed by you and your group Iteration Design Cycle Write Program Compile Program Debug Compilation Errors Examine output results Debug Logical Errors Examine hardware results Debug Hardware Errors Iteration 4746: System Design Process Documentation “Digitally dropped” into Blackboard Site This could take one hour or thirty hours depending on your skills. I will help you avoid “landmines” Homework Assignments Two weeks to complete an assignment No excuse for: network down, printer out of toner, computer locks up, etc. HW assignments will “overlap” Average one assignment due every 1 ½ weeks. HW’s will build upon one another You may use solutions from previous HW’s Homework assignments will be customized Solutions will be given for a “general” problem You must have working program for full credit Homework Assignments HW’s are “self-correcting” for the “right answer”. I’ll check for the “correct” solution. HW must be on time Digital Drop Box (time stamped) Both you and your partner must digitally submit Only one copy of handwritten notes needed. Design Projects Design projects DO NOT replace regular homework assignments. You may have both due during the same week. Hardware MUST work for more than ½ credit Quizzes Designed to “keep you awake.” Mostly group quizzes Some individual quizzes No make-up quizzes will be given Used to monitor attendance I will drop the three lowest quiz grades Course Notes All slides will be available online Exam, HW, and Quiz solutions online EEL-4746 Best Practices Keep up with the course!!! Complete the Assignments!!! You will be allowed to work in groups, but EEL-4746 Best Practices The only way to learn to code in Assembly Language is to code in Assembly Language. EEL-4746 Best Practices In other words, practice makes perfect. 4746 Software Distribution THRSIM11 MS Windows based 68HC11 simulator Text Editor Cross Assembler Disassembler Software Simulator Simulate Hardware Target Board Downloader Target Board Terminal Interface THRSIM11 Site license for FAMU-FSU COE students Download program self-extracting archive from course webpage Under “Course Library” Request License File from ECE website Must make request from FAMU or FSU email domain. Cannot give license file to another student! Design Methodology Definition: Engineering Design Methodology A systematic approach to achieve the desired goal of a solution to the problem (i.e. a working design) using proven principles or practices. You must follow our 4746 design methodology to get full credit. Design Methodology “Right Answers” Violates “Best Practices” “Right answer” but not correct solution. “Best Practices Solution” Design Abstraction How do we “describe” a system? Design Abstraction Example: Design a “system” which will complement input A A F(x) Y=A where A and Y are single bit values We can “describe” this design using a logical Truth Table A Y 0 1 1 0 Levels of Design Abstraction Our goal in ECE is physical or hardware implementations of the design. 0 1 Design Specs Design Process 2 3 4 Vcc1 a1 a2 a3 a4 b1 Hardware b2 b3 b4 5 6 7 8 GND 0 In ECE, we “design” at several levels of “abstraction” Levels of Design Abstraction Example: Design a “system” which will complement input A System Level: EEL-4746 (M68HC11) A ASM Code Y=A M68HC11 Assembly Language: COMA ; Complement A STAA Y ; Store Accumulator A at Y Levels of Design Abstraction Example: Design a “system” which will complement input A Behavioral Level: EEL-4712 A Not A VHDL code: Y <= not A; Y=A Levels of Design Abstraction Example: Design a “system” which will complement input A Gate Level: EEL-3705 Digital Logic Design A Inverter Symbol Y=A Levels of Design Abstraction Example: Design a “system” which will complement input A Circuit Level: EEL-3300 Electronics I PFET Vdd A Y=A NFET CMOS Technology Levels of Design Abstraction Example: Design a “system” which will complement input A Digital IC Design: EEL-4313 Digital IC Design Y=A VDD GND A CMOS Technology Levels of Design Abstraction Fabrication Level: EEL-4330 Microelectronics Eng P+ P+ N+ NWELL PSUB N+ Summary of Levels “System”: Assembly Language Behavioral: VHDL Logical: Gates Electronic Circuit: Transistors Integrated Circuit: IC Layout Fabrication: IC Processing Summary All “levels” give you the same result. We will learn how to use the “system” level to its highest degree of effectiveness. EEL-4746 Microprocessor-based System Design Begin Actual Course Material Basic Computer System Memory CPU I/O Interface To I/O BUS CPU: I/O: Memory: Bus: Central Processor Unit Input/Output Program and Data Address signals, Control signals, and Data signals Microprocessor-Based System Memory CPU I/O Interface BUS CPU: Central Processor Unit Microprocessor I/O: Input/Output e.g. Pentium 4 Memory: Program and Data Bus: Address signals, Control signals, and Data signals To I/O Microcontroller-Based System Memory CPU I/O Interface To I/O BUS CPU: I/O: Memory: Bus: Central Processor Unit Microcontroller Input/Output e.g. M68HC11 Program and Data Address signals, Control signals, and Data signals (Although a microcontroller may access external memory as well.) EEL-4746 M68HC11 Micro-controller Design INPUT Devices We will learn to write M68HC11 Assembly Language Code M68HC11 Assembly Language Code Output Devices