Senior Design 2 Documentation

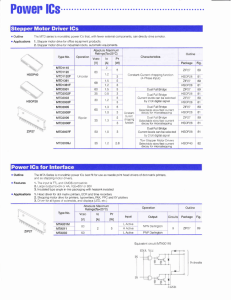

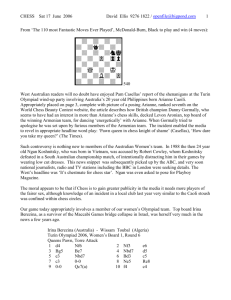

advertisement