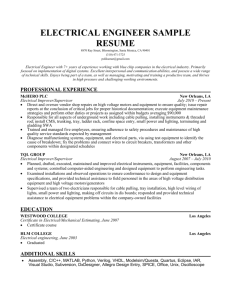

Undergraduate Admissions & College of Engineering

advertisement

Device Characterization ECE/ChE 4752: Microelectronics Processing Laboratory Gary S. May April 1, 2004 Outline NMOS Device Physics PMOS Device Physics CMOS Inverter MOSFET MOSFET = “Metal-Oxide-Semiconductor Field-Effect Transistor” IDn Terminals: G = gate D = drain S = source B = body (substrate) D + G B + VGS - + VB S S n-channel device VDS - MOSFET Key Quantities Currents: IG = 0 (due to insulating oxide layer) ID IS => since IG = 0, ID = IS (Kirchhoff’s Current Law) Voltages: VG VD VS = 0 (usually) VB = 0 (usually) Most important quantities: ID, VGS, VDS MOSFET Cross-Section S VG VD > 0 ID G oxide n+ ID n+ L D S p-type Si cross-sectional view (not to scale) top view (not to scale) Biasing 1) Source and substrate grounded (zero voltage) 2) (+) voltage on the gate Attracts e s to Si/SiO2 interface When threshold voltage (VGS = VTn) is reached, an inversion layer is formed 3) (+) voltage on the drain e-s in the channel drift from source to drain current flows from drain to source I-V Characteristics IDn vs. VGS: IDn VTn VGS VTn = “threshold voltage” Voltage where Si/SiO2 interface becomes strongly inverted with electrons Voltage were NMOS transistor “turns on” I-V Characteristics (cont.) IDn vs. VDS: IDn (1) (2) VGS increasing VGS = 0V VDS Linear Region Labeled “(1)” on previous plot IDn = f(VGS, VDS) and VDS < VGS – VTn, VGS ≥ VTn Equation: I Dn Wm nCox L 2 VDS (VGS VTn )VDS 2 where: mn = electron mobility in the channel, Cox = eox/tox, tox = oxide thickness, eox = oxide permittivity (3.9e0 for SiO2) Saturation Region Labeled “(2)” on the previous plot IDnsat = f(VGS) and VDS ≥ VGS – VTn, VGS ≥ VTn Equation: Wm nCox 2 VGS VTn I Dnsat 2L Transconductance In the saturation region: g mn iD vGS Q W W m nCox (VGS VTn ) 2 m nCox I Dn L L where: “Q” represents the quiescent operating point (i.e., fixed DC values of VGS, VDS) Outline NMOS Device Physics PMOS Device Physics CMOS Inverter Circuit Symbol + S + VSG VS B - - G B + VS D - -IDp D p-channel device Cross-Section S VS G VS D > 0 ID oxide p+ IDp p+ L n-type Si Appropriate I-V equations found by: 1) reversing the direction of ID 2) reversing the polarity of all bias voltages (VBS => VSB, VGS => VSG, VDS => VSD) Biasing 1) Source and substrate grounded (zero voltage) 2) (-) voltage on the gate + Attracts h s to Si/SiO2 interface When threshold voltage (VSG = -VTp) is reached, an inversion layer is formed 3) (-) voltage on the drain h+s in the channel drift from source to drain current flows from source to drain Currents Linear: VSD ≤ VSG + VTp, VSG ≥ -VTp I Dp 2 Wm pCox VSD (VSG VTp )VSD L 2 Saturation: VSD ≥ VSG + VTp, VSG ≥ -VTp I Dpsat Wm p Cox 2L V SG VTp 2 Transconductance In the saturation region: g mp iD vSG Q W W m pCox (VSG VTp ) 2 m pCox ( I Dp ) L L Outline NMOS Device Physics PMOS Device Physics CMOS Inverter Inverter Logic Logic symbol: A Y Function: YA Truth table: A 0 1 Y 1 0 Ideal Voltage Transfer Characteristic V+ = supply voltage VM = V+/2 = switching point of inverter (where input voltage = output voltage) Actual Transfer Characteristic Voltage Definitions VIL = input voltage where slope of transfer characteristic is -1 VIH = larger input voltage where slope of transfer characteristic is -1 VOH = output voltage at input voltage of VIL VOL = output voltage at input voltage of VIH VM = voltage where output voltage equals input voltage VMAX = output voltage when input voltage is zero (usually VMAX = V+) VMIN = output voltage when input voltage is V+ (usually VMIN ~ 0) Voltage Definitions (cont.) VOH = minimum output voltage for valid logic 1 VOL = maximum output voltage for valid logic 0 VIH = minimum input voltage for valid logic 0 VIL = maximum input voltage for valid logic 1 Noise Margins Noise = unwanted variations in voltage which, if too great, can cause logic errors Noise margin high (NMH): tolerable voltage range for which we interpret the inverter output as a logic 1 NMH = VOH – VIH Noise margin low (NML): tolerable voltage range for which we interpret the inverter output as a logic 0 NML = VIL - VOL Switch Representation Switching Dynamics Input high: turn on bottom switch and discharge capacitive load PMOS off NMOS on (linear) Input low: turn on the top switch and charge capacitive load PMOS on (linear) NMOS off VTC: Another Look (1) Input voltage = 0 V, output voltage = VDD (2) NMOS saturated, PMOS linear (3) Both transistors saturated (4) NMOS linear, PMOS saturated (5) Input voltage = VDD, output voltage = 0 V Approximate VTC VOH = VMAX; VOL = VMIN VM is input voltage where VOUT =VIN = VM Currents NMOS current at VIN = VM is: I Dn 1 W 2 m nCox VM VTn 2 L n PMOS current at VIN = VM is: I Dp 1 W 2 m p Cox VDD VM VTp 2 L p Deriving VM Define: W kn m nCox L n W k p m pCox L p and Setting IDn = -IDp gives: VTn VM kp kn 1 (VDD VTp ) kp kn Computing Noise Margins To compute noise margins, the next step is to calculate VIL and VIH Do so by determining the slope of the transfer characteristic at VIN = VM (i.e., voltage gain) Then: Project a line to intersect at VOUT = VMIN = 0 V to find VIH Project a line to intersect at VOUT = VMAX = VDD to find VIL Voltage Gain Voltage gain can be shown to be: vout Av ( g mn g mp )( ron || rop ) vin where: ron and rop are output resistances of the NMOS and PMOS transistors, respectively In general: ro 1 and g o iD vDS go Q We can find ro by inverting the slope of the ID vs. VDS characteristic Noise Margins We can find VIL and VIH using the slope (Av) of the VTC: (VDD VM ) VIL VM Av VIH VM VM / Av Noise margins: NM L VIL VOL VM (VDD VM ) / Av NM H VOH VIH VDD VM VM / Av