Agenda: 1- Introduction. 2

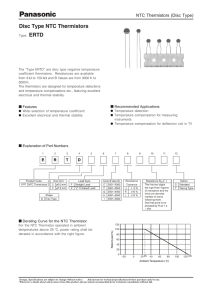

advertisement

“ Near-Threshold Computing: Reclaiming Moore’s Law Through Energy Efficient Integrated Circuits ” By Ronald G. Dreslinski, Michael Wieckowski, David Blaauw, Senior Member IEEE, Dennis Sylvester, Senior Member IEEE, and Trevor Mudge, Fellow IEEE Presented by: Abdullah Almohaimeed © Agenda: 1- introduction. 2- NTC Concept. 3- NTC analysis 4-Barriers of NTC. 5- Addressing NTC barriers. 6- future direction. 7- conclusion. Introduction: # Moore’s Law and its obstacles. # How to address this problem from different view designers. # The important of energy: • High-Performance Platforms. • Personal computing platforms. • Sensor-based platforms. # The desire of designers in this field. NTC Concept: Operating the devices near the threshold voltage (Vth). Result of energy consumption in modern CMOS. determine the optimal of Vdd: Vdd > Vth : energy is highly sensitive to Vdd. Vdd ≈ Vth : 10 times of energy reduction at the expense of 10 times degradation performance. Vdd< Vth: circuit delay increases exponentially with Vdd, causing leakage energy. Energy and Delay in different supply voltage operation NTC analysis: Example of precessors: Subliminal and Phoenix processors. only a modest increase in energy at the NTC region (around 0.5 V), while frequency characteristics at that point are significantly improved. NTC Barriers: A. Performance Loss: e.g. 45 nm technolgy the fanout of four inverter delay at NTC supply is 10x slower than at nominal supply. B. Increased Performance Variation: NTC designs display increase in performance uncertainty. heightens sensitivity to temperature and supply ripple C. Increased Functional Failure: In particular, the mismatch in device strength due to local process variations from such phenomena as random dopant fluctuations(RDF). Addressing NTC Barriers: Addressing performance loss: 1- Cluster-based Architecture: by using of NTC-based parallelism. This method will regain 10–50X of the performance, while remaining energy efficient. 2- Device Optimization: B. Addressing Performance Variation To address these problems by applying: 1) Soft Edge Clocking: Soft-edge flip-flop 2) Body Biasing: is a well known technique for adapting performance and leakage to global variation of process, voltage, and temperature. C. Addressing Functional Failure: The increased of sensitivity lead to a highly rise in functional failure. To address this problem by: 1- Alternative SRAM Cells: 2-SRAM Robustness Analysis Techniques 3-Reconfigurable Cache Designs: Future direction: Canary Circuits: predict the delay failure of a pipeline. The variation-constrained logic using in situ circuitry Conclusion: Moore’s law NTC principle Problems of NTC and their soultion Questions?! Thank you so much for attention