ENGIN341_Syllabus_20140406

advertisement

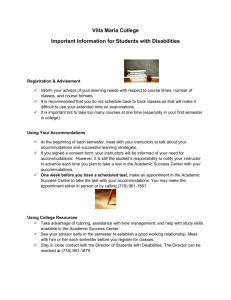

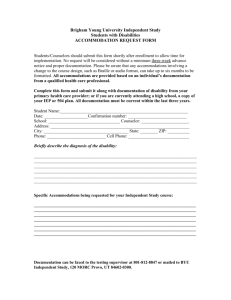

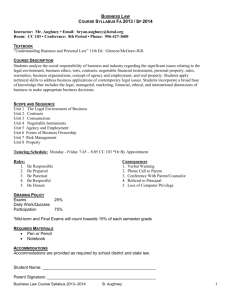

ENGIN 341 Advanced Digital Design (3 credits) Professor Filip Cuckov Office: S-3-111 Email: Filip.Cuckov@umb.edu Tel: 617-287-3539 Course Description This course teaches tools and methodologies for top-down design of complex digital systems. Important topics include minimization, mixed logic, algorithmic state machines, microprogrammed controllers, creating and using a gold model, data and control path design, and data movement and routing via buses. Design methodologies covered include managing the design process from concept to implementation, gold model validation, and introduction to design flow. A hardware description language is used extensively to demonstrate models and methodologies, and is also used in design exercises and projects. Course objectives This course introduces concepts of design and synthesis of digital systems of moderate to high-level of complexity. The objectives for this course are for the students to: Be able to use a hardware description programming language to develop, analyze, and verify all designs to ensure they meet functional requirements and performance specifications. Design and manipulate Product of Sums and Sum of Product forms and mixed-logic. Design and analyze sequencers constructed from SR, T, and JK flip-flops. Design and analyze custom, one-hot, and microcoded sequencers. Understand and apply basic datapath components. Understand what a bus is and how information is communicated on a bus. Be able to use Algorithmic State Machine (ASM) charts and Register Transfer Logic (RTL) to specify the sequencing in digital systems. Be able to design a digital system control path and datapath to solve a digital system design problem. Be able to design and implement a digital system from a given set of specifications. Offer Frequency Once a year, every Fall semester. Pre-Requisites: ENGIN 241 – Digital Systems with Lab. Textbook C. H. Roth, Jr., and L. K. John, Digital Systems Design Using VHDL, Second Edition. Toronto: Thompson Learning, 2008. References B. Mealy, F. Tappero, Free Range VDHL, freerangefactory.org, 2013. Organization: Website: Exams: Lecture notes will be provided on the class website and/or Black Board. Two midterm exams will be given during the semester and one final exam will be given during the final exam period. Homeworks: There will be weekly homework assignments. Solutions will be posted as well as discussed in class. Homework assignments will reinforce the topics introduced in class. Project: There will be project assigned mid semester, to be completed by the end of the semester. Students will be expected to apply their theoretical knowledge and demonstrate their engineering design abilities through the project. The final project will be a collection of several smaller “milestone” take-home projects. Each milestone will be a small standalone project. There will be four milestones, roughly one per month. All milestones will need to be combined together at the end of the semester to make sure that the final project works as modeled. Example projects: Audio encoder/decoder, Image compression and decompression via FPGAs, Edge detection and image processing, Digital signal processing applications. Grading The grade distribution is as follows: 30% Homework 30% exams (2 exams 15% each) 20% project (4 milestones, 5% each milestone) 20% final exam. Syllabus Week 1: • Overview of course and expectation • Review of digital design concepts Week 2: • Modeling digital systems with VHDL • Concurrent signal assignments Week 3: • Processes, sequential statements, and delay models • Introduction to design flow Week 4: • SOP and POS forms and design • Mixed logic design Week 5: • SR, T, and JK flip-flop design • State minimization Week 6: • State machine and controller design overview • State machine diagrams Week 7: • One-hot finite state machine design • Microcoded controller design Week 8: • System modeling with VHDL • Introduction to FPGA/CPLD design flow Week 9: • Modeling levels of abstraction • Gold model regression testing Week 10: • Components, registers, counters • Fast adders Week 11: • Multipliers • Buses and data movement Week 12: • VHDL Functions, procedures, and packages • Attributes, IEEE Standard Logic Week 13: • VHDL Named associations and generate statements • File input and output and automated testbenches Week 14: • Introduction to CPU design Week 15: • Summary Accommodations The University of Massachusetts Boston is committed to providing reasonable academic accommodations for all students with disabilities. This syllabus is available in alternate format upon request. If you have a disability and feel you will need accommodations in this course, please contact the Ross Center for Disability Services, Campus Center, Upper Level, Room 211 at 617.287.7430. http://www.umb.edu/academics/vpass/disability/ After registration with the Ross Center, a student should present and discuss the accommodations with the professor. Although a student can request accommodations at any time, we recommend that students inform the professor of the need for accommodations by the end of the Drop/Add period to ensure that accommodations are available for the entirety of the course. Code of Conduct and Academic Integrity It is the expressed policy of the University that every aspect of academic life--not only formal coursework situations, but all relationships and interactions connected to the educational process--shall be conducted in an absolutely and uncompromisingly honest manner. The University presupposes that any submission of work for academic credit is the student’s own and is in compliance with University policies, including its policies on appropriate citation and plagiarism. These policies are spelled out in the Code of Student Conduct. Students are required to adhere to the Code of Student Conduct, including requirements for academic honesty, as delineated in the University of Massachusetts Boston Graduate Catalogue and relevant program student handbook(s) http://www.umb.edu/life_on_campus/policies/code.