diffpair

advertisement

ECE3434

Simulation Exercise shw3

Differential pairs

Version 2.2

The differential pair is the principal subcircuit used to discriminate and amplify the difference between two signal

inputs.

The basic topology is represented by figure 3.1. This circuit is called an emitter-coupled pair since the emitters

of the two action transistors, Q1 and Q2 are connected . The current to the two transistors is supplied by a current

source with value Ix as shown. At quiescent, each transistors receives IEE/2, from which transconductance gm for

Q1 and Q2 is determined. An identical topology exists for FETs.

Figure 3.1 Emitter-Coupled Pair (ECP)

For this topology the differential transfer gain , Ad, is

AVS

vo 1

g m RC RL

vI 2

(3.1)

where the factor of ½ is a consequence of the fact that the input signal is split equally between Q1 and Q2. The

transconductance g m 40 I EE 2 and the input resistance is

Rin 2 F (1 g m )

(3.2)

Since the output is taken at the collector node of Q2, the output resistance is approximately

R0 RC

(3.3)

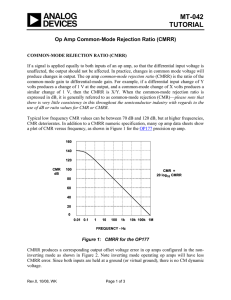

A further quantity of interest to differential amplifier circuits is their ability to reject signals common to the two

inputs. If a common signal is applied to the two inputs, a small (common-mode) transfer gain, Acm will result, due

primarily to the limitations of the current source I1. The ratio of the differential gain Ad to the common-mode

gain Acm, is known as the common-mode rejection ration (CMRR) and is given by

CMRR

Ad

g m ROC

Acm

(3.4)

where ROC is the output resistance for the current source. So the CMRR would be a finite factor for a more

realistic differential pair topology as represented by figure 3.2

Equation (3.4) is a consequence of equation (2.1) and common-mode gain Acm, which can be shown to be

Acm

RC || RL

2 ROC

(3.5)

Figure 3.2 Emitter-Coupled Pair (ECP)supplied by a simple current mirror as current source.

Since, for the simple current mirror, Rout = VAF /Ix = large, the CMRR is very large, and is often expressed in terms

of dB. VAF is the Early voltage for the drive transistor of the current source. For the simple current mirror as

current source it can be shown that

CMRR VAF 2VT

where VT is the thermal voltage (nominal value = .025V)

(3.6)

1. (a) (15 pts) Set up the ECP of figure 3.2. As a preliminary step create a semi-ideal transistor Qn from the

template QbreakN by use of Edit >Model >Edit Instance Model which will enable the transistor to be given

(excerpted) values as follows:

In your construct include the various input sources to include a VDC source VDiff between the inputs and the

VSIN sources V3 and Vicm as indicated. Toggle the Display associated with the specifications of each of these

sources so that the amplitude and frequency settings of these sources are visible on your circuit schematic, like

that of figure 3.2

Make a screen snapshot of your schematic (similar to that of figure 3.2 and identify it as your figure 3.1.

(b) (10 pts) With Rx = 100k and F = 100 (as designated) determine analytical values for Rin , Rout, Ad , Acm

and the CMRR, and enter these values in a short table as your table 3.1.

(c) (10 pts) Under the Analysis > setup menu set up the DC sweep for linear sweep of VDC source VDiff and

sweep it from –0.5 to 0.5V at a 0.001V increment.

Concurrently set up the transient sweep (Analysis >setup >Transient) for a sweep from 0 to 2ms at increment

0.2us. Toggle the ‘Enable Fourier’ flag and set center frequency= 2kHz, 8 harmonics, and V(VL) as the output

Execute the simulation. Select the Analysis Type = DC and make a screen snapshot (as your figure 32a) of a plot

of D(Vo)/D(VDiff). Include a cursor measurement (cursor coordinates) of the peak value. The result (and your

figure) should look something like that of figure 3.3 below.

Figure 3.3. Transfer slope for the ECP of figure 3.2. The magnitude at peak is the no-load (i.e. RL =

infinity) transfer gain of the differential pair. Note the symmetry of the transfer response.

Since we are using SPICE, and therefore measuring the transfer slope at Vo, load RL is blocked from the DC slope

measurement by capacitance C2. The dVo/dVi gain = essentially the no-load gain, for which

Ad'

v0 1

g m RC

vI 2

(3.7)

And from which we determine the transfer gain Ad

v L v0 v L

v I v I v0

Ad'

RL

RL RC

You may have wondered about the mysterious (and apparently useless) resistance R4 in the circuit of figure 2.2,

which has value {Rs} = .01. If Rs is changed to a value on the order of input resistance Rin , the amplitude peak

of figure 3.3 will drop by a factor defined by the input voltage divider. (If Rs accidentally = Rin, then the output

gain will drop by a factor of 2). Use this fact and selected values for Rs to find the (SPICE values of) Rin for this

circuit. Show the result as a snapshot of D(Vo)/D(VDiff) for Rs = .01 and Rs = <your selected value>. Identify as

your figure figure 3.2b.

It may be worthwhile to use the Analysis>Setup>Parametric option in conducting this assessment.

(d) (15 pts) Now return to the Probe menu and recall the files (via File > Recent files), and in this case call up

the Transient analysis (select the Analysis Type = Transient). Display the output at VL as your figure 3.2c. It

should look like a fairly tame sinusoidal output with little distortion.

However distortion indeed is afflicting this signal, as can be determined by the Fourier analysis table found under

Analysis >Examine Output and which should look something like that shown by figure 3.4.

Figure 3.4: Fourier analysis of the circuit of figure 3.2

The second column contains the amplitudes of the harmonics at the output. For example

v L 305mV

60.1V V

vI

5mV

=AVS

Take note of the fact that the 5th harmonic (corresponding to 10kHz) is a little larger than it should be. It

represents the amplitude that has been transferred to output from the common-mode input by the (small) transfer

gain Acm. From the output amplitudes indicated by the table and the input amplitudes (as applied by sources V3

and Vicm) you should be able to determine the CMRR. And it should compare favorably with the analytical

value. For the example shown above Vout(diff) = 0.3052V (corresponding to the 2kHz input) and Vout(commonmode) = 1.671 x10-3 V (corresponding to the 10kHz input).

for which we note that

Acm

1.67 mV

.034 V V

50mV

Undertake this assessment and take a snapshot of the Fourier table that you used as your figure 3.2d.

Enter all of the values (Ad, Rin , Acm , CMRR) thus obtained by simulation as a second (=comparison) line in your

table 3.1.

2.(20pts) As an extended test of the differential pair of figure 3.2, invoke the Analysis >Parametric option with

Rx set as a global parameter. Step Rx from 25k to 2.5Meg, one point per decade (be sure to set the decade

option). Then repeat the measurement sequence of part 1, (which you will probably have to do by selecting each

output one-by-one. Show results as a comprehensive table, your Table 3.2. It may be handy to just do a snapshot

of an Excel section (snapshot zoom to section of interest).

Rather than showing screen snapshots of all three cases, shown only your D(Vo)/D(VDiff) output as a curve

family as your figures 3.3. Include cursors.

3. (30pts) Construct an entirely new circuit using (real) 2N3904 and 2N3906 transistors as per figure 3.5. Make

this your figure 3.4a. This topology is called an active-load emitter-coupled pair. It has similarity to the test

topology of figure 3.2 except the bias load RC is replaced by a current source with output impedance that is very

high.

Figure 3.5 Active load ECP

Step Rx from 25k to 2.5Meg, one point per decade. Determine the transfer gain Ad and the CMRR for each of

these (three) cases. List in a table (as your Table 3.3). Use Excel to generate your table. Use the Fourier

analysis to determine CMRR in the same way as you did for part 1(d).

Include a figure (your figure 3.4b) that shows a snapshot of the complete family of DC sweep plots for the

differential transfer slope D(V(Vo)/D(VDiff) (and for which the sweep range has to be much smaller than that used

in part 1, on the order of –25mV to +25mV).

Include another figure (your figure 3.4c) with a snapshot of sweep plots of Vo(t). It should be fairly evident from

this output what is happening to the gain and to the CMRR.

And make a snapshot of the Excel ‘table’ as your report Table 3.3.

Notice that you have included an additional input source, VAC, with amplitude 1mV. This source should be

swept using the AC sweep, from 10Hz to 1MegHz (decade sweep). From the AC output sweep, determine the

input resistance = (V(Vp) – V(Vn))/I(VDiff) and enter this information into your table along with an analytical

prediction for Rin. Use value of Rin corresponding to the lower frequencies.

This is a high-gain topology and is used in many opamps and diffamps.

Ad g m g 02 g out 4 (the subscripts relate to transistors Q2 and Q4)

where g out 4

Vaf (Q4) F 1 g m R4

I C 4 F g m R4

In your table 3.3 include table entries that compare the extracted simulation values for Ad, CMRR, and Rin with the

analytical values. Do not expect good correlation, although they will be of similar magnitudes.

Note that you will have to make use of Edit >Model >Edit Instance Model to ascertain the values of Vaf for the

2n3904 and 2n3906 transistors.