drivers-jan-overview-v1

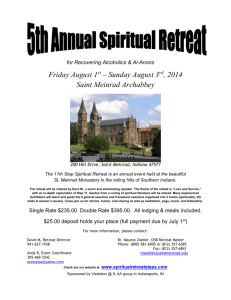

advertisement

Jan M. Rabaey

EECS Dept.

Univ. of California, Berkeley

BWRC 2003 Winter Retreat

PicoRadio’s ─ The Mission

Ubiquitous Sensor and Monitor Networks

Meso-scale low-cost radio’s for ubiquitous wireless

data acquisition that

• are fully integrated

–Size smaller than 1 cm3

• minimize power/energy dissipation

– Limiting power dissipation to 100 mW

enables energy scavenging

• and form self-configuring ad-hoc networks

containing 100’s to 1000’s of nodes

BWRC 2003 Winter Retreat

Wireless Sensor Networks

• Dominant trend in Wireless Industry:

More Bits/sec/(Hz)

• Wireless sensor networks offer interesting alternative:

More bits/$/nJ

Smart buildings

Traffic

management

Energy

BWRC 2003 Winter Retreat

management

Medical

Infrastructure

maintenance

PicoRadio Team

•

Faculty

–

–

–

–

–

•

•

•

Fred Burghardt

Sue Mellers

Jonathan Reason

Hugo Shi

Reto Stutz

Yuen Hu Chee

Richard Lu

Brian Otis

Nathan Pletcher

Uli Schuster

Energy Scavening and

Packaging

–

–

–

Mike Montero

Dan Odell

Shad Roundy

BWRC 2003 Winter Retreat

•

Marco Sgroi

Rong Zhong

Networking, MAC and

Locationing

–

–

–

–

–

–

–

–

–

RF

–

–

–

–

–

Design Tools

–

–

Testbed

–

–

–

–

–

•

Jan Rabaey

Paul Wright

Kannan Ramchandran

Ali Niknejad

Alberto Sangiovanni-Vincentelli

•

Chunlong Guo

Tufan Karalar

Enyi Lin

Nir Matalon

Dragan Petrovic

Rahul Shah

Jana Van Greunen

Mei Xu

Charlie Zhong

Digital Network Processor

–

–

–

–

–

–

–

–

–

Josie Ammer

Mika Kuulusa

SuetFei Li

Jacob Poppe

Huifang Qin

Mike Sheets

Jonathan Tsao

Ruth Wang

Janie Zhou

PN-IIIv1: The First Self-Contained Sensor Node

Solar Cell

(0.5 mm)

Battery (3.6

mm)

PCB (1

mm)

Chip encapsulation

(1.5 mm)

Version 1: Light Powered

Size determined by power

dissipation (< 0.5 mW avg)

BWRC 2003 Winter Retreat

Components and battery

mounted on back

Version 2: Vibration

Powered

PN-IIIv1 Architecture: The “Quark” ChipSet

Digital

Network

Processor

(“Charm”)

16kB

CODE

Flash

Storage

4kB

XDATA

256

DATA

Chip

Supervisor

DW8051

20MHz

Clock Source

Serial

Powertrain

sfrbus or membus?

FlashIF

Solar Cell

SIF

ADC

MAC

Voltage

Voltage

Supply

Voltage

Supply

Supply

SIF

LocalHW

Serial

GPIO

ADC

PHY

Sensor1

Sensor2

PrgThresh0 PrgThresh1

User

Interface

Microresonators

(“Up and Down”)

BWRC 2003 Winter Retreat

OOK

Receiver

Tx0

Tx2

OOK

Transmitter

RF Transceiver

(“Strange”)

SIF = sensor interface

“SmorgasBoard”

Prototyping All Components of PNv3

Solar-cell based

energy scavenging

Vibration-based

energy scavenging

Dynamic Memory

Power-down Test

BWRC 2003 Winter Retreat

FBAR based radio

“Strange”: Back to The Future

(Courtesy of Brian Otis)

© 2000 - Direct Conversion

fc= 2GHz

>10000 active devices

no off-chip components

© 1949 - superregenerative

fc= 500MHz

2 active devices

high

quality

passives - hand tuning

BWRC

2003 off-chip

Winter Retreat

D. Yee, UCB

Back to The Future

OSC1

MOD1

OSC2

Preamp

Matching

Network

PA

MOD2

FBAR-based

RF Filter

RF Filter

Env

Det

RF Filter

Env

Det

A

Simplicity Rules

•

•

•

•

•

Minimizes use of active components

Uses simple modulation scheme (OOK)

Allows efficient non-linear PA

Down-conversion through non-linearity (Envelope Detector)

Tx and Rx in 3-4 mW range (when on)

BWRC 2003 Winter Retreat

fclock

fclock

The “Strange” Components

OSC/PA

LNA

Testchip in 0.13 mm CMOS

Fully functional

PA

Test

300mm

OSC

ENV

2mm

Inductors

Agilent FBAR

Technology

Co

BWRC 2003 Winter Retreat

Rx

C x Lx

An Operational PicoRadio (RF) !!!

Built by chaining prototype-chip

components using

chip-on-board assembly.

Implements complete TX and RX

functionality

FBAR

300m

m

2mm

BWRC 2003 Winter Retreat

An Operational PicoRadio (RF)

Built by chaining prototype-chip

components using

chip-on-board assembly.

Implements complete TX and RX

functionality

FBAR

Out

300m

m

2mm

RF

In

BWRC 2003 Winter Retreat

“Strange”─The Integrated Version

OSC1

MOD1

OSC2

PA Test

MOD2

4 mm

LNA

Test

TX1

Passive

Test

Structures

Receiver

OSC1

Diff

Osc

MOD1

OSC2

Preamp

Matching

Network

PA

MOD2

Env Det

Test

TX

TX

On:

On:44mW

mW

Stby:

Stby:11mW

mW

Off:

Off:00mW

mW

TX2

Preamp

PA

Matching

Network

TX

TX

On:

On:44mW

mW

Stby:

Stby:11mW

mW

Off:

Off:00mW

mW

• Technology: 0.13 mm CMOS

combined with off-chip FBARs

• Carrier frequency: 1.9 GHz

• 0 dBm OOK

• Two Channels

• Channel Spacing ~ 50MHz

• 10-160 kbps/channel

RF Amp Test

fclock

RF Filter

RF Filter

Env

Det

RF Filter

Env

Det

LNA

fclock

BWRC 2003 Winter Retreat

RX

RX

On:

On:33mW

mW

Off:

Off:00mW

mW

In fab as of December 10

Pro’s or Con’s of Simple Radio’s

• Small Change in Path Loss

Has Dramatic Impact on

Transmission Quality

0

10

20 kbps, +1.5dBm

40 kbps, +3dBm

80 kbps, +4.5dBm

-1

10

– Channel is either “good” or

“bad”

-2

10

• Reducing Symbol Time (or

Increasing Data Rate)

Reduces Energy/bit for

same QOS

-3

BER

10

-4

10

-5

10

– Factor 2 reduction in symbol

time for 1.5 db in path gain

-6

10

-7

10

-36

-35

-34

-33

effective path loss

-32

Simulated response of PN3v1 radio

BWRC 2003 Winter Retreat

-31

-30

• Go for fastest possible

radio that simple scheme

allows (limited by ISI)

Integrated NanoMechanical Filter Technology

(In cooperation with R. Howe and BSAC)

Sense

Electrode

Drive

Electrode

RBAR: Radial

Bulk Annular

Resonator

B. Bircumshaw and

A. Pisano

g

ri

Substrate

BWRC 2003 Winter Retreat

ro

Integrated NanoMechanical Filter Technology

Shear Ring Resonator (SRR)

Differential drive and differential

sense electrodes are alternated

along the circumference:

+ 24 dB in Dynamic Range

(S. Bhave and R. Howe)

–Drive

SiC versions of RBAR

and SRR in fab

+Drive

–Sense

BWRC 2003 Winter Retreat

+Sense

Reactive Digital Network Processor (“charm”)

Sensor/actuator

interface

App/UI

User

interface

Sensor/

actuators

Prototyped on FPGA

In Fab March 03

Aggregation/

forwarding

Transport

16kB

CODE

Network

Energy

train

Chip

Supervisor

DLL (MAC)

Locationing

Interconnect network

RF (TX/RX)

Antenna

• Reactive inter- and intra-chip signaling

• Aggressive Use of Power-Domains

• Chip Supervisor Manages Activity

BWRC 2003 Winter Retreat

Chip

Supervisor

DW8051

Serial

Baseband

Reactive

radio

256

DATA

4kB

XDATA

FlashIF

SIF

MAC

ADC

SIF

LocalHW

PHY

Serial

GPIO

ADC

1 mW on

< 10 mW sleep

Size: 6 mm2

Synchronization Block Diagram

Synch Algorithm:

1.

Carrier Detect

•

•

2.

Symbol and Packet Timing

Estimation

•

3.

Indicates carrier detected to DLL

layer

Sets threshold for timing estimation

Sets timing and threshold for bit

decisions

?

Carrier

Sense

Carrier Detected

Threshold

Est.

Symbol and Packet

Timing Estimation

Bit Decisions

Timing

Threshold

Bits

ADC

Envelope

Detector

Analog

Filter

ADC

Matched

Filter

Slicer

Estimated Complexity: 65 kGates

BWRC 2003 Winter Retreat

Locationing Engine ─

Floor plan and Dataflow

Maintenance (11K μm2 )

LS Back

Substitute

Flooding Block

(36K μm2)

(76K μm2)

LS CORDIC

(67K μm2)

Receive

Packet

(21K μm2)

LS Matrix Memory

(111K μm2)

LS Setup(23K μm2)

Least Squares (LS) Solver

Received

Packet

Transmit

Packet

(17K μm2)

Update

selfposition

Broadcast

to

neighbors

Update neighbor-list

Performs first-order locationing based on hop-count

BWRC 2003 Winter Retreat

Prototyping Protocol Processor on FPGA

Area Percentage Breakdown

13.0%

0.3% 6.7%

10.9%

0.1%

2.0%

0.2%

0.8%

2.4%

63.6%

DLL_queue logic

SPI

DW8051 mem

Baseband

Commercial Vertex Board

DLL_queue mem

UART

supervisor

Locationing

DW8051 logic

DLL

Clock cycles

Software execution time by task

35000

30000

25000

20000

15000

10000

5000

0

Total: 150 kGates (not including memory)

FITS EASILY ON SINGLE VERTEX

Total estimated area: 3.5 mm2

Check Tables

Forwarding

With Hardware

Accel

pkt Interest pkt

BWRC 2003 Winter Data

Retreat

Send to app

Power Domains─

State-Preserving Power-Down

Switched-Capacitor Converter

M6

loss

forpower

Standby

*

Supply Voltage

Generation

CL

K

NMOS

0.75V/-0.25V

PMOS 0.25V/-0.5V

CL

K

1V => 200mV

1.3uA => 6.5uA

Output Power = 1.3uw

M

9M

*

CL

K

CL

K

8

M

7

CL

K

CL

K

CL

K

•

Vout = 190mv +/- 3mv

CL

K

Efficiency:

90% w/o clock power

80% w/ clock power

CL

K

CL

K_

1.3 mm2 SRAM Leakage Control Test Chip

BWRC 2003 Winter Retreat

(0.13um Process, with 4K bytes SRAM embedded )

Power Domains

State-Preserving Power-Down

Ramped Supply

Some interesting observations:

• measured retention voltage: 250 mV (100 mV

simulated)

• leakage power reduction larger than anticipated:

5.4 mW at 0.3 V versus 241 mW at 1V (factor 45)

1V

Standard

Vdd

300mV

Standby Vdd

Memory Data Bit 4 @

Address 0xFFh

BWRC 2003 Winter Retreat

Factor 12

1V

Measured leakage current

Of 4 KB SRAM

Inter-board connectors

Verifying the Overall System―

Emulating a PicoRadio Network

FPGA

FPGA

Xbar

FPGA

96 bit inter-Xbar buses

•

BEE (Berkeley Emulation Engine)

– An Hierarchical Mesh-Connected Array of 20 Xilinx Vertex-2000 FPGA’s

– High-level Mapping Software Support – Simulink/Stateflow as the Preferred Input Format

– Extensive Debugging/Monitoring Support

•

•

Easily Supports 16+ PicoNodes and Evolved Channel Models

A New and Exciting Trend in System Verification

BWRC 2003 Winter Retreat

The Bottom Line: Total PicoNode Power

Pave = 250 mW

Dominated by TX

(+RX) power

Parameters:

• 3 packets/sec

• 200 bits/packet

• 20 bit pre-amble

• 5 neighbors

• Synchronization using

serendipitous rendezvous (or cycled

receiver) with Ton/T = 0.1

Dominated by

channel monitoring

power

Increasing data rate of radio reduces total power dissipation of

PicoNode! (based on real traffic models and implementation parameters)

BWRC 2003 Winter Retreat

The Impact of The Wake-Up Radio

Factor 5 to 10

reduction over

cycled receiver

BWRC 2003 Winter Retreat

Why an FPGA Implementation First?

Some Important Lessons Learned

• Sensor networks (even when statically deployed) are very

dynamic

– Susceptible to rapid changes in the channel. This is especially the case

when using simple radio’s (with limited diversity)

– In low-data rate applications, anything learned about the channel is

irrelevant when the next packet arrives (coherence time is less than 1 sec)

• Solutions:

– Make data-link layer reliable

– Use diversity (time, frequency, space) ─

Only spatial diversity offered by redundancy in sensor networks meets the

cost and energy requirements as well as the constraints offered by ad-hoc

networks.

Bottom Lines:

– Extensive statistics gathering at all the levels of the stack an

absolute necessity

– Given these observations, committing to a fixed protocol stack is

premature

BWRC 2003 Winter Retreat

Lessons Learned: Extensive Statistics

Gathering a Necessity

User Interface

Programs

Environment

Statistics and Management Service

Application Layer

Sensor Board I

HW

Temp.

Sensor

Sensor Board II

HW

Light

Sensor

HW

HW

Humidity

Sensor

HW

Accelerometer

SW

HW

Magnetometer

Monitor

Application Packet Drivers

SW

SW

parameter configuration

Manager

SMS Packet Drivers

SW

Network Layer

SW

Energy-Aware

Routing

Algorithm

SW

Neighbor List

Service

Queuing Service

SW

SW

Location

Service

Recorder

SW

Counter Control Service

SW

Datalink Layer

HW

Transmit

Controller

& Datapath

HW

Media Access

Controller

HW

Receive

Controller

& Datapath

Physical Layer

Bluetooth Radio

BWRC 2003 Winter Retreat

HW

CRC

Counters

HW

Session

Counters

Added “statistics and

management server” to

PicoNodeI Protocol stack

Measurements: Link Reliability

(narrow band Bluetooth channel)

BER: Flipped Bits: 20 Byte Packet

1400

79%

1200

Lesson Learned:

1000

• With 2 bits of ECC, we can recover

approximately 18% more data packets.

• Or …

800

# Packets

600

400

13%

5%

200

2%

1%

3

4

0%

0

0

% total returned

packets

1

2

# Flipped bits in a packet

BWRC 2003 Winter Retreat

5

Extend correlator from 4 to 10 taps

100.0

100.0

90.0

90.0

80.0

80.0

70.0

70.0

60.0

60.0

50.0

50.0

40.0

40.0

30.0

30.0

4 tap

BWRC 2003 Winter Retreat

0.0

5 RTS

10 tap

7 DTX

7 RTS

6 DTX

5 DTX

7 DTX

7 RTS

6 DTX

5 DTX

4 DTX

3 DTX

2 DTX

1 DTX

5 RTS

10.0

4 DTX

0.0

1 RTS

3 RTS

3 DTX

10.0

20.0

2 DTX

1 RTS

3 RTS

1 DTX

20.0

The Variability of Link Quality

Broadcast quality over time as measured at the

BWRC round-table on a Friday

Broadcast quality over time

60

Broadcast Success Rate [%]

50

40

30

20

10

0

10/19 h

12/43 h

11/31 h

13/55 h

15/07 h

16/19 h

Time

PicoRadio Meeting

BWRC 2003 Winter Retreat

NAMP Meeting

17/31 h

The Impact of Spatial Diversity

100.00

3 nodes

90.00

Broadcast success rate [%]

80.00

70.00

60.00

50.00

2 nodes

40.00

30.00

Deep

fade due to

multipath

20.00

10.00

0.00

0

10

20

30

40

50

60

70

80

Data gathered using

PicoNodeI testbed

90

100

110

120

130

140

150

160

170

180

190

200

distance [cm]

Adding a single node already changes broadcast reliability

dramatically – spacial diversity is the preferred way to

provide robustness in sensor networks

BWRC 2003 Winter Retreat

210

Making The Data Link More Reliable

MPMsg == UpdateLinkMetric/

UpdateNbList(UpdateLinkMetric)

Conditional

Add

Timeout == TRUE &&

LinkMetric >= ThresholdAdd/

SendLinkTestReq()

UpdateNbList(LinkTest)

MPMsg == CondAdd/

UpdateNbList(CondAdd)

Timeout == TRUE &&

LinkMetric < ThresholdAdd/

UpdateNbList(Clear)

Link Test

MPMsg == Success &&

Timeout == FALSE/

UpdateNbList(Active)

Timeout == TRUE /

UpdateNbList(Inactive)

Startup == TRUE

Inactive

Timeout == TRUE &&

LinkMetric < ThresholdRmv/

SendLinkTestReq()

UpdateNbList(LinkTest)

Active

Timeout == TRUE &&

LinkMetric >= ThresholdRmv/

UpdateNbList(Active)

Revised link layer keeps track of reliability of

channel

BWRC 2003 Winter Retreat

• Use only links that

prove to be reliable

over the long term

• Use RTS/CTS scheme

before transmission to

perform instantaneous

“channel estimation”

Energy Scavenging - Solar

Wires to load

Regulator and battery

Battery charging from solar cells

2.5

3 cm

volts

2

1.5

1

0.5

Lamp 12 inches from cells

Load disconnected

0

0

50

100

minutes

BWRC 2003 Winter Retreat

150

200

Energy Scavenging - Vibration

Super

Capacitor

Simulated Load

Power circuit

Piezo

Generator

Vibrometer

1 mA load

BWRC 2003 Winter Retreat

100 mA load

Energy Scavenging - Vibration

Piezo-bender

prototyped for

“in-tire” sensor network

BWRC 2003 Winter Retreat

Status/Summary

PicoNodes becoming a reality!

PicoNode IIIv1

• First integrated sub-mW node, combining custom

components with some of the shelf elements – Average

Power dissipation estimated around 400 mW

• Operation of FBAR radio demonstrated; Integration

version (2 channel) in fab

• Full functionality of protocol processor demonstrated on

FPGA – system level verification under progress;

processor chip in fab in March

• Concepts of power-domains and voltage-down retention

demonstrated

• Energy scavenging sub-system implemented and

functionality demonstrated

BWRC 2003 Winter Retreat

Perspectives: Beyond PN III

• Extending the Lifetime of Sensor

Networks

• Wake-up Radio

• Localization

• Design Methodology (with GSRC)

– “Ambient Intelligence one of main GSRC drivers”

• Bringing Power even Lower!

– Reliable computation on unreliable platforms

Computation in the ultra low-voltage space

• Exploring New Application Spaces

BWRC 2003 Winter Retreat

Lifetime of Sensor Networks

The hot-spot problem

D. Petrovic, R. Shah, K. Ramchandran

Project funded by NSF

BWRC 2003 Winter Retreat

How to mitigate hot-spots in

sensor networks?

• Intelligent routing

• Data aggregation

• Distributed coding

• Topology planning

• Altruistic nodes

• Dynamic relocation of

functionality

Established strict upper-bounds

on lifetime!

Combining Aggregation and Coding

Coding by Ordering

Store information in data order

Unique

ID {1,2,3,4} Payload {1,..., 6}

1

2

3

4

Controller

Sensors

Border

Node

Packet aggregation suppresses

header overhead

BWRC 2003 Winter Retreat

2

4

0

2

2

1

3

Ordering corresponds to

integer 2 = payload of packet 4

Computation in the Ultra-Low Voltage Space

• Power dissipation becoming the

main roadblock towards further

integration!

• Aggressive voltage scaling seems to

be the only plausible answer

• Offers the opportunity for reducing

power dissipation of mobile sensor

nodes by other major fraction

BWRC 2003 Winter Retreat

4.5

4

Supply Voltage (V)

– Intel Processor Integration is “power

constrained”

– Drain-source leakage a major fraction

of power dissipation – direct function of

supply voltage

– Gate leakage one of the main emerging

challenges – again, a very strong

function of supply voltage

5

3.5

3

2.5

2

1.5

1

0.5

1

-1

10

Minimum Feature Size (micron)

SIA Roadmap not

aggressive enough?

Computation in the Ultra-Low Voltage Space

How low can we go?

• Gain limitations but lower bound on supply voltage on a

couple of kT/q

• While many noise sources scale, some do not!

– Thermal noise

– Soft errors

Circuits are bound to start producing errors when supply voltages are

aggressively scaled!

• Variability of threshold voltage remains approximately

constant, causing gate performance to vary widely

Explore circuit and architecture techniques that deal with

performance variations (e.g., self-timed) and are

(somewhat) resilient to errors!

BWRC 2003 Winter Retreat

Some First-Order Results

• Studied distribution of

delay over wide range

of process parameters

(simple inverter chain)

using Monte Carlo

Analysis

• PDF shows lognormal

distribution – this is,

Gaussian is not a

good model

BWRC 2003 Winter Retreat

Some Intriguing New Applications

Everyday Computing

Addressing the “everyday

problem”

(e.g. Where are my keys?)

Courtesy of Mik Lamming and Jim Rowson,

HP Labs

BWRC 2003 Winter Retreat

ISSCC 2002 Jack Raper Award for

Outstanding Technology Directions Paper

“PicoRadios for Wireless Sensor

Networks: The Next Challenge in

Ultra-Low Power Design”

J. M. Rabaey, J. Ammer, T. Karalar,

S. Li, B. Otis, M. Sheets, T. Tuan

BWRC 2003 Winter Retreat