T.Nathiya Lect/EEE QUESTION BANK EE 2255

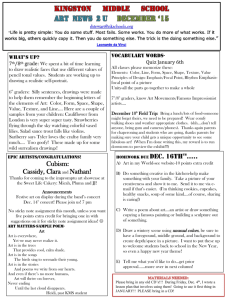

advertisement

T.Nathiya Lect/EEE QUESTION BANK EE 2255 - DIGITAL LOGIC CIRCUITS PART-B UNIT-I: BOOLEAN ALGEBRA AND COMBINATIONAL CIRCUITS 1. 2. 3. Reduce the function using Karnaugh mapping technique. F(w,x,y,z) = ∑ (0,7,8,9,10,12) + d(2,5,13) (16 Marks) (JUNE 2011) (OR) Using K Map Simplifying the following 5 variables function and draw the logic diagram for the minimized function. F= ∑ (2, 4, 10, 12, 19, 21, 27, 29) (16 Marks) (DEC’2011) (OR) (a) Design a full adder circuit using multiplexer (8) (JUNE 2011) (b) Simply the Boolean function F(w,x,y,z) = ∑ (1,3,7,11,15) and the don’t care conditions d(w,x,y,z) = ∑ (0,2,5) (8) (JUNE 2011) (OR) (a) Implement the following Boolean function with NAND – NAND logic. Y = AC + ABC + 𝐴BC + AB + D (6) (JUNE 2012) (b) Simplify and implement the following sop function using NOR gates. F(A,B,C,D) = ∑ (0,1,4,5,10,11,14,15) (10) (JUNE 2012) (OR) (a) Obtain the minimal SOP form for the following five variable switching function using K-map. F = ∑ m (2,3,6,7,11,12,13,14,15,23,28,29,30,31) + ∑ (16,27) (10) (MAY 2010) (b) An example that AND-OR operation can be replaced by NAND-NAND operation. (6) (MAY 2010) (OR) (a) Reduce the following K-map. F = m2+m3+m4+m6+m7+m9+m11 +m13. (6) (DEC’2009) (b) State and prove the De Margan’s theorem. (10) (DEC’2009) Simplify the following 5 variable Boolean expression using Queen Mc Cluskey method. F = ∑ m (0, 1, 9, 15, 24, 29, 30) + d (8, 11, 31) (16) (JUNE 2011) (OR) Obtain the minimum SOP using Quine Mecluskey’s method and verify using K-map. F = m0+m2+m4+m8+m9+m10+m11+m12+m13 (16) (DEC’2006, 2010, JUNE 2009, 2007) (Pg: SQ.19) (OR) Reduce the following using Tabulation method. F = m2+m3+m4+m6+m7+m9+m11+ m13 (16) (DEC’2006) (OR) Reduce the following using Tabulation method and verify with K maps. F = ∑ (0, 1, 2,3,4,6, 8, 10, 12, 14) (16) (DEC’2010) (Pg: SQ.16) (OR) Obtain the minimum SOP using Quine Meclusky’s method and verify using K map. (16) (MAY 2010) F = m0+m1+m2+m3+m6+m7+m8+m9+m14+m15 (OR) (i) Simplify the following Boolean function by using tabulation method. (12) (JUNE 2011) F = ∑ (0, 1, 2, 8,10,11,14, 15) (ii) Explain Demargon’s law with suitable diagram. (4) (JUNE 2011) (OR) Find the minimal-sum-of-product expression for the following switching function using Quine- Mc Clusky method. F = ∑ m (1, 2, 3, 6, 8, 9, 14, 17, 24, 25, 26, 27, 30, 31) + d (4, 5) (16) (MAY 2010) (OR) Determine the prime implicants of the following function and verify using K map. (16) (JUNE 2009) F (A, B, C, D) = ∑ (3, 4, 5, 7, 9, 13, 14, 15) (OR) Determine the prime implicants of the following function and verify using K map. (16) (JUNE 2007) F (A, B, C, D) = ∑ (0, 1, 2, 3, 4, 7, 9, 10) (i) Using 8 to 1 multiplexer realize the Boolean function. (8) (JUNE 2011) T= f (w,x,y,z) = ∑ (0, 1,2,4,5,7,8,9,12,13) (ii) Realize the function given in (i) using decoder and external gates. (8) (JUNE 2011) (OR) Implement the function. F = ∑ (0, 1, 3, 4, 12, 14, 15) using an 8×1 multiplexer. (16) (DEC 2010) (OR) T.Nathiya Lect/EEE 4. (i) Implement the given function using multiplexer. F (x, y, z) = ∑ (0, 2, 6, 7) (8) (JUNE 2012) (ii) Implement the full subtractor using demultiplexer. (8) (JUNE 2012) (OR) (i)Implement the given function using multiplexer. F (x, y, z) = ∑ (0, 2, 6, 7) (10) (JUNE 2007) (ii)Explain the concept and working of quadruple 2 to 1 line multiplexer. (6) (JUNE 2007) (OR) (i) Use a multiplexer having three data select inputs to implement the logic for the function f= ∑ m (0, 1, 2, 3, 4, 10, 11, 14, 15) (10) (MAY 2010) (ii) Design an Octal –to- Binary encoder. (6) (MAY 2010) (i) Design and implement a full adder circuit using NOR gates. (10) (MAY 2010) (Pg: SQ.5) (ii) Design a 2 × 4 demultiplexer. (6) (MAY 2010) (OR) Design a circuit that converts 8421 BCD to Excess -3 codes. (16) (DEC’2006, 2010, 2009, JUNE 2009) (OR) (i)Design an 8421 to gray code converter. (8) (DEC’2006) (Pg: SQ.8) (ii)Implement a full adder using half adders. (8) (DEC’2009) (OR) Design a 4-bit Binary to Gray code converter. (16) (DEC’2011, MAY 2010) (Pg: SQ.8) UNIT-II: SYNCHRONOUS SEQUENTIAL CIRCUITS 1. 2. (i) Describe the ripple counter with a neat diagram. (8) (JUNE 2011) (ii) Explain the operation of Master/Slave JK flip-flop with a diagram. (8) (JUNE 2011) (OR) (i) Design a 4-bit decade counter. (10) (DEC’2012) (ii) Sketch the state diagram and the state table for ‘D’ and ‘JK’ flip-flops. (6) (JUNE 2012) (OR) (i) Differentiate between analysis and design of sequential logic circuits. (4) (JUNE 2012) (ii) Design a sequential logic circuit for 3-bit binary counter. (12) (JUNE 2012) (OR) (i) Realize SR flip-flop using NOR gates and explain its operation. (8) (JUNE 2012) (ii) Convert a SR flip-flop into JK flip-flop. (8) (JUNE 2012) (OR) Explain the operation of Clocked JK-FF with suitable diagrams. (16) (JUNE 2011) (OR) (i) Explain the working of a master-slave JK flip-flop. (8) (MAY 2010) (ii) Design a mod-10 counter and explain its working. (8) (MAY 2010) (OR) Design a circuit to convert SR-FF to JK-FF and T-FF. (16) (DEC’2010) (OR) Design a mod-6 counter using FFS. Draw the state transition diagram of the same. (16) (JUNE 2007) A sequential circuit with 2D FFS A and B and input X and output Y is specified by the following next state and output equations. A (t + 1) = AX + BX; B (t + 1) = A’X; Y = (A + B) X' Draw the logic diagram of the circuit, state table and state diagram. (16) (JUNE 2012, DEC’2006) (OR) A sequential circuit has two JK flip-flops A and B, two inputs x,y and one output z. The flip-flop input equations and circuit equations are: JA = Bx + B'y; KA = B'xy; JB = A'x; KB = A + xy; Z = Ax'y' + Bxy Draw the logic diagram of the circuit, state table and state diagram. (16) (MAY 2010 (OR) Derive the state table and state diagram of the sequential circuit shown in figure. (16) (MAY 2010) T.Nathiya Lect/EEE (OR) For the given Moore model sequential circuit, find the state table, state diagram, flips flop input and output equations. (16) 3. Give the reduced state diagram for the following figure. Design the sequential circuit using D flip flops. (16) (JUNE 2011) (OR) Design the clocked sequential circuit using D flip-flops whose state diagram is given below. (16) (OR) Design the clocked sequential circuit using JK flip-flops whose state diagram is given below. (16) (OR) Design a synchronous counter using JK FF to count the following sequence. 7, 4, 3, 1, 5, 0, 7….. UNIT-III: ASYNCHROUNOUS SEQUENTIAL CIRCUIT 1. Design an asynchronous sequential circuit that has two inputs X2 and X1 and one output z. When X1 = 0, the output z is 0. The first change in X2 that occurs while X1 is ‘1’ will cause output z to be ‘1’. The output z will remain 1 until X1 returns to ‘0’. (16) (JUNE 2011, DEC’2009, DEC’2006, DEC’2011, JUNE 2009) (OR) Develop the state diagram and primitive flow table for a logic system that has two inputs, X and Y, and a single output Z, which is to behave in the following manner. Initially both inputs and output are equal to 0. Whenever X = 1 and Y = 0, the Z becomes 1 and whenever X = 0 and Y =1, the Z becomes 0. When the inputs are zero, i.e. X =Y = 0 or inputs are one i.e. X = Y= 1, the output Z does not change; it remains in the previous state. (16) (DEC’2011) (OR) Design an asynchronous sequential circuit with two inputs x, y and one output z. initially both inputs are equal to zero. When x or y becomes ‘1’, the output z becomes 1. When the second input also becomes 1, the output changes to 0. The output stays at 0 until the circuit goes back to the initial state. (16) (JUNE 2011) T.Nathiya Lect/EEE 2. 3. (OR) Design an asynchronous sequential circuit with two inputs x, y and one output z. the output z = 1 if x changes from 0 to 1, z = 0 if y changes from 0 to 1 and z = 0 otherwise. Realize the circuit using JK flipflops. (16) (DEC’2010) (OR) Obtain the primitive flow table for an asynchronous circuit that has 2 inputs x, y and one output z. An output z = 1 is to occur only during the input state xy = 01 and then if the only if the input state xy = 01 is preceded by the input sequence xy = 01, 00, 10,00,10,00. (16) (JUNE 2011) (OR) Draw the state diagram and obtain the primitive flow table for a circuit with two inputs x 1 and x2 and two outputs z1 and z2 that satisfies the following conditions. When x1 x2 = 00 output z1 z2 = 00, when x1= 1 and x2 changes from 0 to 1 the output z1 z2 = 01, when x2= 1and x1 changes from 0 to 1 the output z1 z2 = 10 otherwise output does not change. (16) (OR) An asynchronous sequential circuit is described by the excitation and output fonctions. Y = X1X2 + (X1+X2) Y Z=Y Draw the logic diagram of the circuit, Derive the transition table and output map and describe the behavior of the circuit. (16) (MAY 2010) (OR) An asynchronous sequential circuit has two internal states and one output. The excitation and output functions describing the circuit are Y1 = X1X2 + X1Y2 + X2Y1 Y2 = X2 + X1Y1 Y2 + X1Y1 Z = X2 + Y1 Draw the logic diagram of the circuit, Derive the transition table and output map And Obtain a flow table for the circuit. (16) (MAY 2010) Explain the steps for the design of asynchronous sequential circuits. (16) (DEC’2010,JUNE 2011, JUNE 2012, MAY 2011) UNIT-IV: PROGRAMMABLE LOGIC DEVICES, MEMORY AND LOGIC FAMILIES 1. 2. 3. 4. 5. Discuss the concept of working and applications of the following memories: ROM, EPROM, PLA (16) (DEC’2006) (OR) Discuss the concept of working and applications of the following memories: EPROM, PLA, FPGA (16) (MAY 2010, DEC’2009) (OR) Discuss the concept of working and applications of the following memories: EPROM, PLD, FPGA (16) (JUNE 2009, JUNE 2007) Draw a neat sketch showing the implementation of Z1 = ab’d’e + a’b’c’d’e’ + bc + de; Z2 = a’c’e; Z3 = bc + de + c’d’e’ + bd & Z4 = a’c’e + ce using a 5 x 8 x 4 PLA. (16) (DEC’2010) (OR) (i)Design an AND-OR-PLA that implements the functions F1 (A, B, C) =m (0, 2, 4, 6), F2 (A, B, C) = m (1, 3, 5, 7). (10) (DEC’2012) (ii)Compare the characteristics of TTL, ECL and CMOS logic families. (6) (DEC’2010) (OR) (i)Combinational circuit is defined by the functions F1 (A, B, C) =m (0, 1, 6, 7), F2 (A, B, C) = m (2, 3, 5, 7). Implement the circuit with a PLA having 3 inputs, 3 product terms and 2outputs. (10) (JUNE 2012) (ii)Describe the concept and working of FPGA. (6) (JUNE 2012) (OR) Design a BCD to Excess- 3 code converter and implement using suitable PLA. (16) (JUNE 2011) Write notes on ROM and its types. (16) (JUNE 2012, DEC’2007) With neat circuit, explain the working principle of ECL. (16) (DEC’2011) (i)Explain the working of a 2 inputs CMOS NOR gate. (8) (MAY 2010) (ii)Compare the TTL, ECL and CMOS digital logic families. (8) (MAY 2010) T.Nathiya Lect/EEE 6. 7. 1. 2. 3. 4. 5. 6. 7. (i) Explain the working of a 3 inputs TTL NAND gate. (10) (MAY 2010) (ii) Write notes on FPGA. (6) (MAY 2010) Write notes on the characteristics and implementation of the following digital logic families. ECL, TTL. (16) (MAY 2010) (OR) Write notes on the characteristics and implementation of the following digital logic families. ECL, CMOS. (16) (DEC’2009, JUNE 2007, DEC’2006) (OR) Write notes on the characteristics and implementation of the following digital logic families. TTL, ECL, CMOS. (16) (DEC’2007) UNIT-V: VHDL Write VHDL code to model JK flip-flop. (a) Use conditional assignment statement.(8) (b) Use the characteristic equation. (8) (MAY 2010) Write VHDL code for 8 × 1 Multiplexer. (16) (DEC’2011) (OR) (i)Briefly discuss the use of ‘Packages’ in VHDL. (6) (DEC’2012) (ii)Write an HDL code that implements an 8:1 multiplexer. (10) (DEC’2012) Construct a VHDL module listing for a 16:1 MUX that is based on the assign statement. Use a 4-bit select word S3 S2 S1 S0 to map the selected input Pi = (i = 0 …15) to the output. (16) (DEC’2010) Describe the RTL design using VHDL with the help of example. (16) (MAY 2011) (OR) (i) Explain the design procedure of RTL using VHDL. (10) (JUNE 2012, DEC’2010) (ii) Write a note on VHDL test benches. (6) (DEC’2010) (a) Write VHDL code for a full adder using equation. (6) (MAY 2010) (b)Write VHDL code for a 4-bit full adder using the module define in (a) as a component. (10) (DEC’2011) Write the VHDL code for mod 6 counter. (16) (JUNE 2012, MAY 2011) Write VHDL code for BCD to 7 segment decoder. (16) (DEC’2011) PART – A UNIT-I: BOOLEAN ALGEBRA AND COMBINATIONAL CIRCUITS 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. Implement the switching function Y = BC + AB + D. (JUNE 2011) State De-Morgan’s laws. (DEC’2010, DEC’2011, DEC’2012, MAY 2010, MAY 2011) Why NAND and NOR gates are called as universal gates? Simplify: F= xyz + xy + xyz’. (MAY 2010) Realize the function F (A, B) = A’B + AB’ using NAND gates only. Name two canonical forms of Boolean algebra. (MAY 2010, JUNE 2007) What is a prime implicant? (MAY 2010, JUNE 2009) Express the function f(x,y,z) = x + yz as a sum of minterms. Plot the expression in K-map F (w, x, y) = Σ (0, 1, 3, 5, 6) + d (2, 4) Minimize the expression XY + X’YZ’ + YZ using Boolean theorem. Simplify: x + x’y (DEC’2007) What happens when all the gates in a two level AND – OR gate network are replaced by NOR gates? What is the value of b if √ 41b = 5? (DEC’2006) Why digital circuits are more frequently constructed with NAND and NOR gates than with AND and OR gates? (DEC’2006, JUNE 2009) Distinguish between completely specified function and incompletely specified function. (DEC’2009, JUNE 2009) List out the differences between half adder and full adder. (DEC’2007) Write down the truth table of a full adder. Implement half adder circuit using logic gates. (DEC’2012, DEC’2007) Implement half subtractor circuit using logic gates. (MAY 2010) Implement the full adder circuit with a 3 × 8 decoder. (MAY 2010) Write down the truth table of a full subtractor. (JUNE 2011) What will be the maximum number of outputs for a decoder with a 6 bit data word? (JUNE 2009) List out the differences between decoder and encoder. What is a multiplexer? Give its applications. T.Nathiya Lect/EEE 25. 26. 27. 28. 29. 30. 31. 32. 33. 34. 35. What is a demultiplexer? Give its applications. Mention the differences between Decoder and DMUX. (DEC’2010) Mention the differences between DMUX and MUX. (JUNE 2009, JUNE 2007) Implement the function f = Σm (0, 1, 4, 5, 7) using 8 to 1 multiplexer. Draw the 4 x 16 decoder constructed with two 3 x 8 decoders. (JUNE 2007, DEC’2009) Design a half subtractor using 2 to 4 decoder. Draw a 1 to 2 demultiplexer and 2 to1 multiplexer. Implement a NAND gate using 4:1 Multiplexer. (DEC’2011) Give the circuit of a half adder – subtractor. What is data selector? (DEC’2006, MAY 2011) Mention the use of decoders. (DEC’2006) UNIT-II: SYNCHRONOUS SEQUENTIAL CIRCUITS 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. How flip-flops differ from a Latch? (MAY 2010, DEC’2009) Write the excitation tables of JK and D flip-flops. (JUNE 2011, JUNE 2009, MAY 2011) Write the characteristic equation of JK and D flip-flop. (JUNE 2011) Convert an SR flip-flop to D flip-flop. (DEC’2011, MAY 2010) Draw the state diagram of a JK-FF. (DEC’2010, DEC’2009, JUNE 2007) The JK-FF is an universal flip-flop. Justify. (DEC’2012) Draw the state diagram of SR Flip flop and give its truth table. (DEC’2010) List out the limitations and drawbacks of SR flip-flop. (MAY 2010) Convert a JK flip – flop into a T flip – flop. (JUNE 2007) Convert JK to D flip-flop. (JUNE 2007) Derive the characteristic equation of T flip-flop. Realize the T flip-flop using a JK flip-flop. (MAY 2010) What is meaning for edge triggering in Flip-Flops? (DEC’2006, DEC’2011, DEC’2007) Describe the behavior of SR flip-flop by means of a table. Define equivalent circuit? (MAY 2010) Distinguish between combinational and sequential circuits. What is a Mealy machine? Give an example. (JUNE 2011) Differentiate between Moore and Mealey type sequential circuits. (DEC’2010, JUNE 2009) What is a state?(DEC’2006, JUNE 2009) What are state diagrams and state table? (DEC’2010, DEC’2012) When is a counter said to suffer from Lockout? (JUNE 2011) What is lockout? How it is avoided? (JUNE 2012) Draw the logic diagram of 3 bit ring counter. Why is state reduction necessary? (JUNE 2009, DEC’2006, DEC’2011) If the input frequency of a T flip – flop is 1600 KHz, what will be the output frequency? Give reason for your answer. (DEC’2006) UNIT-III: ASYNCHROUNOUS SEQUENTIAL CIRCUIT 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. What is mean by critical race? (JUNE 2011) What is a race condition? (DEC’2012) Define asynchronous sequential machine. (DEC’2010) Sketch the block diagram of Asynchronous sequential circuits? (DEC’ 2012) Define flow table of Asynchronous sequential circuits? (JUNE 2012) What is the significance of state assignment? (JUNE 2011, DEC’2010) Difference between Asynchronous and synchronous sequential circuits. (MAY 2011, JUNE 2009) When a sequential machine is said to be trivial? What are the two types of Asynchronous sequential circuits? (MAY 2010) Why a serial counter is referred to as asynchronous. Why parallel counter is faster than ripple counter? Define fundamental-mode operation. Define Hazard.(MAY 2011) Why critical race is said to be harmful and how it is avoided in asynchronous sequential Circuits? T.Nathiya Lect/EEE 15. 16. 17. 18. What are cycles in asynchronous sequential circuits? What are races? How can it be avoided? (MAY 2010) What is dynamic hazard? (MAY 2010) What is static hazard? (JUNE 2011) UNIT-IV: PROGRAMMABLE LOGIC DEVICES, MEMORY AND LOGIC FAMILIES 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. Write the steps to perform memory read operation. (JUNE 2011) What is FPGA? (DEC’2011) List the configurable elements of FPGA architecture. (JUNE 2012) Define Noise margin. (MAY 2010, JUNE 2007) Define Fan-in and Fan out? (MAY 2011, JUNE 2011) Why CMOS is preferred to TTL? Compare PLA and PAL. (JUNE 2009, MAY 2010, DEC’2010) What are the advantages of PLA? (DEC’2012) What is the block diagram of PLA? (DEC’2011) Compare ROM, PROM and EPROM memory devices. (DEC’2012) How does the architecture of PLA different from PROM? What is volatile memory? Give example. Which is faster TTL or ECL? Which requires more power to operate? (DEC’2007) What is the advantage of Schottky TTL family? State the important characteristics of TTL family. (DEC’2010) What are the types of ROM. (MAY 2011) State two advantage of CMOS logic. (JUNE 2011) Differentiate EPROM and EEPROM. (JUNE 2009) Difference between ECL and TTL. (DEC’2006) What is PLA? (JUNE 2012) Differentiate PLA, and PROM. (JUNE 2009) What is the major difference between TTL and ECL? List the two advantages of ECL? (MAY 2010) Why does the propagation delay occur in logic circuits? Draw NAND and NOR gates in CMOS logic. UNIT-V: VHDL 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. Give the different operators used in VHDL. (DEC’2010) What are the various modeling techniques in VHDL? (JUNE 2012) What are the different types of operators? What is an RTL level notation? When can RTL be used to represent digital systems? (MAY 2011) What is an ASM? (MAY 2011) What is a test bench? (DEC’2010, DEC’2011) What are packages and libraries? Write the VHDL code for AND gate. (DEC’2010) Write HDL code for half adder. (JUNE 2012) What is the need of sub program? (DEC’2011) …ALL THE BEST…