Instruction cycle - Computational Science

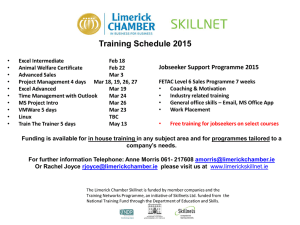

advertisement

CPS 101 Introduction to Computational Science Wensheng Shen Department of Computational Science SUNY Brockport Computer Instruction Sets Binary numbers Hexadecimal numbers Octal numbers Machine instructions Binary numbers Base-2 number system, represents numeric values using two symbols, 0 and 1. 100 = 26 + 25 + 22 Hexadecimal numbers Base-16 number system, represents numeric values using 16 symbols, 0, 1, 3, 4, 5, 6, 7, 8, 9, a, b, c, d, e, and f 100 = 6×161 + 4 Octal numbers Base-8 number system, represents numeric values using 16 symbols, 0, 1, 3, 4, 5, 6, and 7 100 = 82 + 4×81 + 4 Place-value system 908,305,688 = Number conversion 010111101011010100102 5EB5216 13655228 38792210 The memory of the IAS consist of 1000 storage locations, call words, of 40 binary digits (bit) each. Both data and instructions are stored there. Hence, numbers must be represented in binary form, and each instruction also has to be a binary code. Each number is represented by a sign bit and a 39-bit value. A word may also contain two 20-bit instructions, with each instruction consisting of an 8-bit operation code (Op code) specifying the operation to be performed, and a 12-bit address designating one of the words in memory, number from 0 to 999 39 0 1 (a) Number word Sign bit Right instruction Left instruction 0 Op code 8 19 20 Address 39 28 Opcode Address IAS - details Set of registers (storage in CPU) Memory Buffer Register (MBR) Memory Address Register (MAR) Instruction Register (IR) Instruction Buffer Register (IBR) Program Counter (PC) Accumulator (AC) Multiplier Quotient (MQ) Structure of IAS – detail Fetch cycle and Execution cycle, which taken together is the Instruction cycle. Program control unit (PCU) IAS Instruction Set How IAS Computer Adds Two Numbers Suppose the numbers are stored in memory locations 200 and 201, and The sum is to be saved in memory location 202 Instruction Opcode Description LOAD M(200)00000001 ADD M(201) 00000101 STOR M(202)00100001 AC←M(200) AC←AC+M(201) M(202)←AC IAS Computer Instruction Code 00000001 000011001000 00000101 000011001001 Load 200 Add 201 00100001 000011001010 00000000 000000000000 Stor 202 Storage in Memory Address 0 Address Program Counter, PC Word 200 Word 201 Word 202 Memory First program word Second program word Address max IAS Instruction Cycles Place the starting address in program counter (PC). Start program: MAR ← PC Read memory: IBR ← MBR ← M(MAR), fetch cycle Place left instruction in IR and address 200 in MAR Read memory: AC ← M(200), fetch cycle Place right instruction in IR and address 201 in MAR Read memory and add: AC ← AC + M(201), execution cycle PC ← PC + 1 IAS Instruction Cycles (Cont.) MAR ← PC Read memory: IBR ← MBR ← M(MAR), fetch cycle Place left instruction in IR and address 202 in MAR MBR ← AC Write memory