Lecture11 - University of California, Berkeley

advertisement

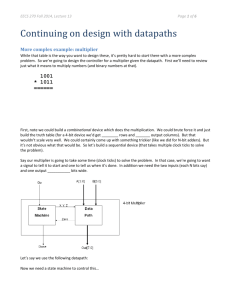

EECS 105 Fall 2003, Lecture 11 Lecture 11: MOS Transistor Prof. Niknejad Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Lecture Outline Review: MOS Capacitors Regions MOS Capacitors (3.8 − 3.9) – – MOS Transistors (4.1 − 4.3): – – – Department of EECS CV Curve Threshold Voltage Overview Cross-section and layout I-V Curve University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOS Capacitor Oxide (SiO2) ox 3.9 0 Gate (n+ poly) 0 Very Thin! tox ~ 1nm Body (p-type substrate) x s 11.7 0 MOS = Metal Oxide Silicon Sandwich of conductors separated by an insulator “Metal” is more commonly a heavily doped polysilicon layer n+ or p+ layer NMOS p-type substrate, PMOS n-type substrate Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Accumulation: VGB < VFB QG Cox (VGB VFB ) VGB VFB − + QB QG −−−−−−−−−−−−−−−−−− ++++++++++++++++++ Body (p-type substrate) ( x) ( x) Essentially a parallel plate capacitor Capacitance is determined by oxide thickness: Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Depletion: VFB<VGB < VT QG (VGB ) QB VGB VFB +− ( x) tox ++ + + + + + + ++ − − − − − − − − − − − − − − − − − Body (p-type substrate) ( x) QB qN a X d (VGB ) Positive charge on gate terminates on negative charges in depletion region Potential drop across the oxide and depletion region Charge has a square-root dependence on applied bias Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Inversion s ( x) tox VGB VT + − ++ + + + + + + ++ − − − − − − − − − − − − − − − − − Body (p-type substrate) ns ni e xdep qs kT ( x) Na The surface potential increases to a point where the electron density at the surface equals the background ion density At this point, the depletion region stops growing and the extra charge is provided by the inversion charge at surface Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Threshold Voltage The threshold voltage is defined as the gate-body voltage that causes the surface to change from p-type to n-type For this condition, the surface potential has to equal the negative of the p-type potential Apply KCL around loop: Gate (n poly) + VGS VFB Vox VBS VGB VT − + VBS −−−−−− s VBS 2 p s Vox Eoxtox tox Es ox qN a xdep qN a 2 s 2qN a (2 p ) Es s s s qN a s 1 VTn VFB 2 p 2q s N a (2 p ) Cox Department of EECS Vox University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Inversion Stops Depletion A simple approximation is to assume that once inversion happens, the depletion region stops growing This is a good assumption since the inversion charge is an exponential function of the surface potential Under this condition: QG (VTn ) QB ,max QG (VGB ) Cox (VGB VTn ) QB ,max Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Q-V Curve for MOS Capacitor QG QN (VGB ) QB ,max VFB VTn VGB (V ) In accumulation, the charge is simply proportional to the applies gate-body bias In inversion, the same is true In depletion, the charge grows slower since the voltage is applied over a depletion region Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Numerical Example MOS Capacitor with p-type substrate: tox 20nm N a 5 1016 cm 3 Calculate flat-band: VFB (n p ) (550 (402)) 0.95V Calculate threshold voltage: ox 3.45 1013 F/cm Cox tox 2 10-6cm 1 VTn VFB 2 p 2q s N a (2 p ) Cox 2 1.6 1019 1.04 1012 5 1016 2 0.4 VTn .95 2(0.4) 0.52V Cox Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Num Example: Electric Field in Oxide Apply a gate-to-body voltage: VGB 2.5 VFB Device is in accumulation The entire voltage drop is across the oxide: Vox VGB n p 2.5 0.55 (0.4) 5 V Eox 8 10 tox tox 2 106 cm The charge in the substrate (body) consist of holes: QB Cox (VGB VFB ) 2.67 107 C/cm 2 Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Numerical Example: Depletion Region In inversion, what’s the depletion region width and charge? VB ,max s p p p 2 p 0.8V VB ,max X d ,max 1 qNa 2 s 2 X d ,max 2 sVB ,max qN a 144nm QB,max qNa X d ,max 1.15 107 C/cm2 Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOS CV Curve C QG Cox Cox QN (VGB ) QB ,max VFB VTn VGB (V ) VFB VTn VGB Small-signal capacitance is slope of Q-V curve Capacitance is linear in accumulation and inversion Capacitance is depletion region is smallest Capacitance is non-linear in depletion Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad C-V Curve Equivalent Circuits Cox Cox Cox Cdep Cdep Cox Cox Cox Ctot Cdep s tox xdep Cdep Cox 1 1 ox xdep Cox In accumulation mode the capacitance is just due to the voltage drop across tox In inversion the incremental charge comes from the inversion layer (depletion region stops growing). In depletion region, the voltage drop is across the oxide and the depletion region Cdep s Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOSFET Cross Section gate body source drain diffusion regions p+ n+ L n+ p-type substrate Add two junctions around MOS capacitor The regions forms PN junctions with substrate MOSFET is a four terminal device The body is usually grounded (or at a DC potential) For ICs, the body contact is at surface Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOSFET Layout poly gate contact G B S p+ n+ B S G D D L n+ xj W p-type substrate L Planar process: complete structure can be specified by a 2D layout Design engineer can control the transistor width W and L Process engineer controls tox, Na, xj, etc. Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad PMOS & NMOS G B S p+ n+ G D L n+ xj B S n+ p+ p-type substrate NMOS L p+ xj n-type substrate PMOS A MOSFET by any other name is still a MOSFET: – – – – D NMOS, PMOS, nMOS, pMOS NFET, PFET IGFET Other flavors: JFET, MESFET CMOS technology: The ability to fabricated NMOS and PMOS devices simultaneously Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad CMOS G G B S D p+ n+ n+ L xj B S D n+ p+ p+ L xj n-type well PMOS NMOS p-type substrate Complementary MOS: Both P and N type devices Create a n-type body in a p-type substrate through compensation. This new region is called a “well”. To isolate the PMOS from the NMOS, the well must be reverse biased (pn junction) Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Circuit Symbols The symbols with the arrows are typically used in analog applications The body contact is often not shown The source/drain can switch depending on how the device is biased (the device has inherent symmetry) Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Observed Behavior: ID-VGS I DS I DS VDS VGS VT VGS Current zero for negative gate voltage Current in transistor is very low until the gate voltage crosses the threshold voltage of device (same threshold voltage as MOS capacitor) Current increases rapidly at first and then it finally reaches a point where it simply increases linearly Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad Observed Behavior: ID-VDS VGS 4V I DS / k non-linear resistor region resistor region I DS “constant” current VDS VGS 3V VGS VGS 2V VDS For low values of drain voltage, the device is like a resistor As the voltage is increases, the resistance behaves non-linearly and the rate of increase of current slows Eventually the current stops growing and remains essentially constant (current source) Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad “Linear” Region Current VGS VTn S p+ G D n+ y n+ p-type NMOS VDS 100mV x Inversion layer “channel” If the gate is biased above threshold, the surface is inverted This inverted region forms a channel that connects the drain and gate If a drain voltage is applied positive, electrons will flow from source to drain Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOSFET “Linear” Region The current in this channel is given by I DS Wv y QN The charge proportional to the voltage applied across the oxide over threshold QN Cox (VGS VTn ) I DS Wv y Cox (VGS VTn ) If the channel is uniform density, only drift current flows V v y n E y I DS Department of EECS W nCox (VGS VTn )VDS L Ey DS L VGS VTn VDS 100mV University of California, Berkeley EECS 105 Fall 2003, Lecture 11 Prof. A. Niknejad MOSFET: Variable Resistor Notice that in the linear region, the current is proportional to the voltage I DS W nCox (VGS VTn )VDS L Can define a voltage-dependent resistor VDS 1 L Req I DS nCox (VGS VTn ) W L R (VGS ) W This is a nice variable resistor, electronically tunable! Department of EECS University of California, Berkeley