Counters

advertisement

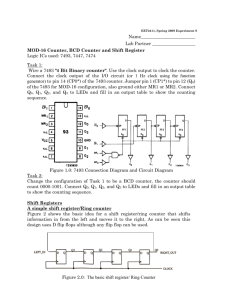

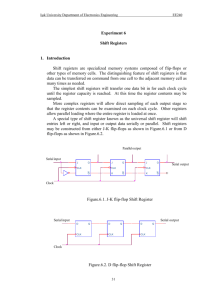

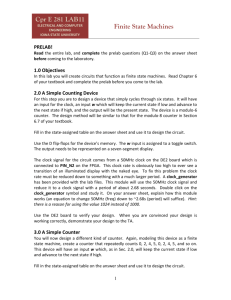

Işık University Department of Electronics Engineering EE240 Experiment 5 Counters 1. Introduction The input pulses, called count pulses, may be clock pulses or they may originate from an external source and may occur at prescribed intervals of time or at random. The sequence of states may follow a binary count or other sequence states in a counter. Counters found in almost all equipment containing digital logic are used for counting the number of occurrences of an event and are useful for generating timing sequences to control operations in a digital systems. Counters come in two categories : Asynchronous counters ( Ripple Counters ) and Synchronous counters. A asynchronous counter is formed with a series cascaded flip-flops. In a asynchronous counters, the flip-flop output transition serves as a source for triggering other flip-flops. The first flip-flop is triggered by the input pulses. The output of the flip-flops are trigger the clock of the next flip-flop. The circuit diagram and timing diagram of a simple asynchronous counter is shown in Figure.5.1. Q1 (20) Vcc Q2 (21) Vcc J CLK outputs Q J CLK K Q CLK Q K Q (a) Circuit diagram Clock Pulses Q1 0 1 0 1 0 Q2 0 0 1 1 0 1 (b) Timing diagram Figure.5.1. An example of asynchoronous counter 25 0 0 1 Işık University Department of Electronics Engineering EE240 The asynchronous counter is an up counter. A down counter can be implemented with the same circuitry used for the counter. By connecting the complement output instead of true output to the clock input of the next flip-flop will form down counter. In a synchoronous counter, the clock pulses are applied to clock inputs of all flip-flops. Therefore each flip-flop of the counter changes state at the same time. This advantage of this configuration is that only one gate delay is required for the counter stages to change state. The circuit diagram and timing diagram of a simple synchronous counter is shown in Figure.5.2. outputs Q1 (20) Q2 (21) Vcc J Q J CLK K Q CLK Q K Q CLK (a) Circuit diagram Clock Pulses Q1 0 1 0 1 0 Q2 0 0 1 1 0 1 0 0 1 (b) Timing diagram Figure.5.2. An example of synchoronous counter This counter is an up counter. A down counter can be implemented with the same circuitry used for the counter. By connecting the complement output instead of true output to the J-K inputs of the next flip-flop will form down counter. 26 Işık University Department of Electronics Engineering 2. EE240 Exercises 2.1. Objective The purpose of this experiment is to investigate asynchronous counters and synchronous counters. We will implement up and down counter using discrete flip-flop ICs 2.2. Material C.A.D.E.T. Breadbord 1x74LS74 Dual D Type Positive Edge-Triggered Flip-Flop 1x74LS76 Dual J-K Flip-Flops with Set(Preset) and Reset(Clear) 1x74LS86 Quad 2-Input XOR Gate 1x74LS90 Decade Counter Jumper Wire 2.3. Procedure 1. Set up the circuit shown in Figure.5.3. Use extra caution wiring the power and ground connections. outputs Led1 Led2 switch1 Vcc=+5v K 9 6 Q 14 12 J Q CL 15 CLK CL 16 Q PR 1 J PR PB2 4 7 2 Vcc=+5v Q 11 CLK K 10 8 3 switch2 Figure.5.3. Asynchronous up counter 2. Turn on power to the circuit. 3. Turn the switch1 and switch2 to logic-1 position. 4. Apply clock pulses to the clock input(PB2) by using pushbutton on the 5. 6. 7. 8. C.A.D.E.T. Record your observations of this circuit operation. Use PB2 to place a count of two on Led1 and Led2. Turn the switch1 and switch2 to logic-1 and logic-0 position, respectively. Record your observation. Turn the switch1 and switch2 to logic-0 and logic-1 position, respectively. Record your observation. Turn off power. This counter is an up- counter. Convert the counter to the down counter.. Repeat 2-6 for the down counter. 27 Işık University Department of Electronics Engineering EE240 9. Remove the wire from PB2 to clock input. Connect the clock input to pulse generator on the C.A.D.E.T. Apply a square wave of 10 kHz. Observe the clock input, led1, and led2 outputs by using an oscilloscope. Record your observation. 10. Set up the circuit shown in Figure.5.4. Use extra caution wiring the power and ground connections. outputs Led1 Led2 Switch1 5 12 2 11 D CL Q 9 CLK CLK Q Q CL 3 Q PR 3 D PR 2 10 4 1 6 8 13 1 Switch2 PB2 Figure.5.4.Synchronous up counter 11. Turn on power to the circuit. 12. Turn the switch1 and switch2 to logic-1 position. 13. Apply clock pulses to the clock input(PB2) by using pushbutton on the C.A.D.E.T. Record your observations of this circuit operation. 14. Use PB2 to place a count of two on Led1 and Led2. Turn the switch1 and switch2 to logic-1 and logic-0 position, respectively. Record your observation. 15. Turn the switch1 and switch2 to logic-0 and logic-1 position, respectively. Record your observation. 16. Turn off power. This counter is an up-counter. Convert the counter to the down counter.. 17. Repeat 11-16 for the down counter. 18. Remove the wire from PB2 to clock input. Connect the clock input to pulse generator on the C.A.D.E.T. Apply a square wave of 10 kHz. Observe the clock input, led1, and led2 outputs by using an oscilloscope. Record your observation 19. Set up the circuit shown in Figure.5.5. Notice the unconventional arrangment of the power pins 20. Turn on power to this circuit. Turn the switch1 to logic-1. The LED should display a zero. 28 Işık University Department of Electronics Engineering EE240 21. Turn switch1 to logic-0. Use PB2 as the count input and the seven segment display on the C.A.D.E.T. as the output. Record your observations of the operation of this circuit. U? PB2 Vcc=+5v switch1 14 1 2 3 6 7 A B QA QB QC QD 12 9 8 11 A B C D R0(1) R0(2) R9(1) R9(2) 74LS90 Figure.5.5 Decade counter 22. Set the counter to some non-zero count and turn switch1 to logic-1. Record your observations. 23. Turn off power and remove the 74LS90 and it’s circuitry. 29 Işık University Department of Electronics Engineering 30 EE240