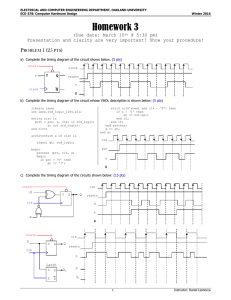

Syllabus: CPE 626 - Advanced VLSI Systems, Spring 2002

advertisement

Department of Electrical and Computer Engineering

University of Alabama in Huntsville

CPE 626 – Advanced VLSI Design

Fall 2004

Midterm Exam Solutions

Instructor: Dr. Aleksandar Milenkovic

Date: October 25, 2004

Place: EB 217

Time: 5:30 PM – 6:50 PM

Note: Work should be performed systematically and neatly. Part I of the exam is closed

book, closed notes, closed neighbour(s). Allowable items include exam, pencils, straight

edge, and calculator. Best wishes.

Question

1

2

3

4

5

Points

25

25

20

20

20

Score

Sum

Please print in capitals:

Last name:____________________________

First name: ___________________________

CPE 626 Midterm Exam

Page 1 of 11

1. (25 points) VHDL

a. (5) For the following VHDL module give the full name of the network modelled with full

description of control signals and draw an RTL schematic of the synthesized module.

library ieee;

use ieee.std_logic_1164.all;

entity mistery1 is

port( D : in std_logic_vector(3 downto 0);

Gn, Cl : in std_logic;

Q : out std_logic_vector(3 downto 0));

end mistery1;

architecture arch1 of mistery1 is

begin

process(Gn, D)

begin

if(Clr=’1’) then Q <= “0000”;

elsif(Gn=’0’) then Q <= D;

end process;

end architecture arch1;

Solution:

This is a 4-bit latch register with inverted gate (if Gn=‘0’ the output Q follows the changes on the

input D) and asynchronous clear active in logic ‘1’.

CPE 626 Midterm Exam

Page 2 of 11

b. (5) For the following VHDL module give the full name of the network modelled with full

description of control signals and draw an RTL schematic of the synthesized module.

library ieee;

use ieee.std_logic_1164.all;

entity mistery2 is

port(Clk, CLRb, SDR, SDL : in std_logic;

S : in std_logic_vector(1 downto 0);

D : in std_logic_vector(3 downto 0);

Q : buffer std_logic_vector(3 downto 0));

end mistery2;

architecture arch1 of mistery2

begin

process (Clk, CLRb)

begin

if (CLRb = '0')then

myS <= “0000”;

elsif (C'event and C='0')then

case S is

when “11” => Q <= D;

when “10” => Q <= SDR & Q(3 downto 1); -- shift right

when “01” => Q <= Q(2 downto 0) & SDL; -- shift left

when “00” => null;

end case;

end if;

end process;

end arch1;

Solution:

This is a description of a 4-bit bidirectional shift register is as follows:

- CLRb is asynchronous active low and overrides all other control signals;

- all other changes occur on the rising edge of the clock;

- if S1=S0=1, the register is loaded in parallel (inputs are D3...D0);

- if S1=1 and S0=0, the register is shifted right; SDR (serial data right) is shifted into Q3

- if S1=0 and S0=1, the register is shifted left; SDL (serial data left) is shifted into Q0;

- if S1=S0=0, no action occurs.

CPE 626 Midterm Exam

Page 3 of 11

c. (5 points) Consider the following fragment of a VHDL code.

type My4 is (‘a’, ‘b’, ‘c’, ‘d’);

type My4_vector is array(natural range <>) of My4;

function myresolve(s: My4_vector) return My4;

subtype My4R is myresolve My4;

...

signal R : My4R := ‘d’;

The resolution function myresolve realizes the signal resolution using the following table.

‘a’ ‘b’ ‘c’ ‘d’

‘a’ ‘a’ ‘a’ ‘a’ ‘a’

‘b’ ‘a’ ‘b’ ‘b’ ‘b’

‘c’ ‘a’ ‘b’ ‘c’ ‘c’

‘d’ ‘a’ ‘b’ ‘c’ ‘d’

Give values of the signal R in time interval from 0 ns to 20 ns assuming that it’s driven by the

following concurrent signal assignment statements.

R <= transport ‘c’ after 2 ns, ‘b’ after 4 ns, ‘b’ after 7 ns;

R <= transport ‘c’ after 2 ns, ‘d’ after 6 ns;

R <= transport ‘d’ after 1 ns, ‘c’ after 5 ns;

Solution:

Time

0

1

2

3

4

5

6

7

...

CPE 626 Midterm Exam

Driver 1

d

d

c

c

b

b

b

b

b

Driver 2

d

d

c

c

c

c

d

d

d

Driver 3

d

d

d

d

d

c

c

c

c

Page 4 of 11

R (resolved)

d

d

c

c

b

b

b

b

b

d. (10 points) For the following VHDL code, assume the D changes to 2 at 5 ns. Give the values

of A, B, C, D, and E each time a change occurs. That is, give the values at time 5 ns, 5 + , 5 +

2, etc. Carry this out until no further changes occur.

entity prob4 is

port(D: inout integer)

end prob4;

architecture q1 of prob4 is

signal A, B, C, E : integer := 0;

begin

E <= A;

P1: process (C, D)

begin

D <= 3;

A <= B;

B <= C;

C <= D;

end process P1;

end architecture q1;

Fill the table below (Note: the number of rows in the table does not correspond to the number of

rows in the correct solution).

Solution:

Time Delta A

0

0

5

+0d

0

+1d

0

+2d

0

+3d

2

+4d

2

CPE 626 Midterm Exam

Page 5 of 11

B

0

0

0

2

3

3

C

0

0

2

3

3

3

D

0

2

3

3

3

3

E

0

0

0

0

0

2

2. (25 points) VHDL

Write a VHDL model for a circular FIFO (First In First Out) memory or queue described by the

following entity:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity FIFOSYN is

generic(n: NATURAL := 16); -- FIFO size

generic(bsize : NATURAL := 16); -- bit vector size

port (

RSTn, CLK, Rn, Wn : in std_logic;

EMPTY, FULL : out std_logic;

FIFOin : in std_logic_vector(bsize - 1 downto 0);

FIFOout : out std_logic_vector(bsize - 1 downto 0));

end FIFOSYN;

Solution:

architecture RTL of FIFOSYN is

type pointer : NATURAL range 0 to n-1;

signal RCNTR, WCNTR : pointer;

subtype wrdtype is std_logic_vector(bsize-1 downto 0);

type regtype is array(0 to n-1) of wrdtype;

signal REG : regtype;

signal RW : std_logic_vector(1 downto 0);

signal FULL_F, EMPTY_F : std_logic;

begin

RW <= Rn & Wn;

seq : process (RSTn, CLK)

begin

if (RSTn = '0') then

RCNTR <= (RCNTR'range => '0');

WCNTR <= (RCNTR'range => '0');

EMPTY_F <= '1';

FULL_F <= '0';

for j in 0 to n-1 loop

REG(j) <= (REG(j)'range => '0');

end loop;

elsif (CLK'event and CLK = '1') then

case RW is

when "00" => -- read and write at the same time

RCNTR <= RCNTR + 1;

WCNTR <= WCNTR + 1;

REG(conv_integer(WCNTR)) <= FIFOin;

when "01" => -- only read

if (EMPTY_F = '0') then -- not empty

if (RCNTR+1) = WCNTR then

EMPTY_F <= '1';

end if;

RCNTR <= RCNTR + 1;

end if;

FULL_F <= '0';

when "10" => -- only write

EMPTY_F <= '0';

if (FULL_F = '0') then -- not full

REG(conv_integer(WCNTR)) <= D;

if (WCNTR+1) = RCNTR then

FULL_F <= '1';

end if;

WCNTR <= WCNTR + 1;

end if;

when others => null;

end case;

CPE 626 Midterm Exam

Page 6 of 11

end if;

end process;

FIFO_out <= REG(conv_integer(RCNTR));

FULL <= FULL_F;

EMPTYn <= EMPTY_F;

end RTL;

3. (25 points) Misc

a. (5 points) What is resource sharing in HDL synthesis? When would you use it?

Solution:

An optimization technique that allows that multiple HDL operations can be performed using a

single resource (multiplier, adder, shifter, ...).

The synthesizer can be directed whether to perform this optimization or not using a dedicated

switch (turn-on or –off).

Pros: reduces on-chip area (resource utilization)

Cons: adds extra logic levels (usually mulitplexers) increasing path delay. Should be avoided for

signals on the critical path.

b. (5 points) What does the following code sequence represent?

architecture beh of mistery4 is

signal a_in, b_in : unsigned (A_port_size-1 downto 0);

signal x_res : unsigned ((A_port_size+B_port_size-1) downto 0);

signal pipe_2,

pipe_3 : unsigned ((A_port_size+B_port_size-1) downto 0);

begin

process (clk)

begin

if (clk’event and clk=’1’) then

a_in <= A; b_in <= B;

x_res <= a_in * b_in;

pipe_2 <= x_res;

pipe_3 <= pipe_2;

y <= pipe_3;

end if;

end process;

end beh;

Solution:

A pipelined multiplier with 4 stages.

CPE 626 Midterm Exam

Page 7 of 11

c. (5 points) What does the following code sequence represent?

entity mistery5 is

port (c : in std_logic;

w

: in std_logic;

a

: in std_logic_vector(4 downto 0);

dpa : in std_logic_vector(4 downto 0);

di

: in std_logic_vector(3 downto 0);

spo : out std_logic_vector(3 downto 0);

dpo : out std_logic_vector(3 downto 0));

end mistery5;

architecture syn of mistery5 is

type x_type is array (31 downto 0) of std_logic_vector (3 downto 0);

signal x : x_type;

signal sa : std_logic_vector(4 downto 0);

signal sb : std_logic_vector(4 downto 0);

begin

process (clk)

begin

if (clk'event and clk = '1') then

if (w = '1') then

x(conv_integer(a)) <= di;

end if;

sa <= a;

sb <= dpra;

end if;

end process;

spo <= x(conv_integer(sa));

dpo <= x(conv_integer(sb));

end syn;

Solution:

ISE will infer a Block RAM component with 2 read ports and one write port; the capacity is 32

locations, each 4 bits wide.

CPE 626 Midterm Exam

Page 8 of 11

d. (5 points) For the following SystemC module give the full name of the network modeled with

full description of control signals and draw an RTL schematic of the synthesized module.

//// file mis3.h

#include <systemc.h>

const NBITS = 4;

const UPL = 11;

const LOL = 3;

SC_MODULE(mis3)

sc_in<bool> clk, clear;

sc_out<sc_uint<NBITS> > q;

sc_signal sc_uint<NBITS> > whoknows;

void prc_x1();

void prc_x2();

SC_CTOR(mis3) {

SC_METHOD(prc_x1);

sensitive_pos << clk << clear;

SC_METHOD(prc_x2);

sensitive << whoknows;

}

};

// file mis3.cpp

#include “mis3.h”

void fsm::prc_x1() {

if(clear)

whoknows = LOL;

else

whoknows = (whoknows + 1)% UPL;

}

void fsm::prc_x2() {

q = whoknows;

}

Solution:

This is a 4-bit up counter that counts 0 -> 1 ->2 ... -> 11 -> 0 ->1 .... (modulus 12); an

asynchronous clear initializes the counter to 3;

4. (20 points) SystemC

Write a SystemC RTL model for the following state machine. Asynchronous reset active low

brings the state machine to S0.

1/Z3

S0/-

S1/Z2

0/Z3

0/-

1/Z3

1/Z3

S2/Z1

0/-

Solution:

CPE 626 Midterm Exam

Page 9 of 11

// file fsm.h

#include <systemc.h>

SC_MODULE(fsm)

sc_in<bool> x, clk, reset;

sc_out<sc_uint<3> > z;

enum state_type {s0, s1, s2};

sc_signal<state_type> fsmstate;

sc_signal<state_type> nextfsmstate;

void prc_fsmcnet();

void prc_fsmsnet();

SC_CTOR(fsm) {

SC_METHOD(prc_fsmcnet);

sensitive << fsmstate << x;

SC_METHOD(prc_fsmsnet);

sensitive_pos << clk;

sensitive_neg << reset;

}

};

// file fsm.cpp

#include “fsm.h”

void fsm::prc_fsmsnet() {

if(!reset)

d

fsmstate = s0;

else

fsmstate = nfsmstate;

}

void fsm::prc_fsmcnet() {

switch(fsmstate) {

case s0:

if(x=0) { z=”000”; nfsmstate =

else {z=”100”; nfsmstate = s1;

break;

case s1:

if(x=0) { z=”110”; nfsmstate =

else {z=”110”; nfsmstate = s2;

break;

case s2:

if(x=0) { z=”001”; nfsmstate =

else {z=”101”; nfsmstate = s0;

break;

}

}

CPE 626 Midterm Exam

Page 10 of 11

s0; }

}

s0; }

}

s2; }

}

5. (20 points) Misc

a. (5 points) What is MAC unit? Draw an RTL schematic of the MAC.

Multiplier --> Adder --> Accumulator

b. (10 points) Give power equations for CMOS devices. How dynamic power can be reduced

(refer to the papers assigned for reading).

c. (5 points) List and explain types of simulation available in Xilinx ISE and ModelSim.

CPE 626 Midterm Exam

Page 11 of 11