SpeedWay Design Workshops™

advertisement

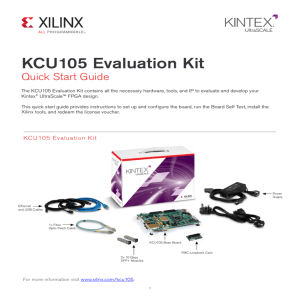

Developing on Xilinx Zynq using C to RTL automatic conversion Objectives ● Introduce Avnet Silica ● Understand the Zynq-7000 All Programmable SoC architecture ● Introduce the Vivado High Level Synthesis o Automatic conversion from C/C++ to VHDL/Verilog Objectives ● Introduce Avnet Silica ● Understand the Zynq-7000 All Programmable SoC architecture ● Introduce the Vivado High Level Synthesis o Automatic conversion from C/C++ to VHDL/Verilog Objectives ● Introduce Avnet Silica ● Understand the Zynq-7000 All Programmable SoC architecture ● Introduce the Vivado High Level Synthesis o Automatic conversion from C/C++ to VHDL/Verilog System Bottlenecked? ● Profiling indicates processor activity o Is processor utilization exceeding 90%? o Processor Queue Length > 2? o If multiprocessor system, processor time > 50%? o Intensive reoccurring tasks? ● Effects of overburdened Processors include: o Increased Data Latency o Delayed Interrupt Handling o Lowered Data Throughput Software Engineers: Stuck in a Sequential World 2 Function Execute Function 1 Fetch & Decode 3 Memory/ Writeback Function 3 to 5 stage pipeline Function Sequential Processing limits performance Parallel Processing is Efficient… ● For critical systems and performance, Engineers utilize Parallel Processing with an FPGA Function ● Needs a Central Controller and Memory Management 2 Execute Function 1 Fetch & Decode 3 Memory/ Writeback Function 3 to 5 stage pipeline Function Memory No Longer are we Limited to Sequential Processing! The First All Programmable SoC Significant Customer Adoption and Momentum In full production since March 2013, ES since 2012 500+ unique customers actively designing 100+ Zynq specific partners All major OSs supported and in use 20+ different development boards and SOMs Performance Xilinx Processing Heritage Dual Cortex-A9 MPCore 1 GHz 5000 DMIPS Dual 440 Cores 550+ MHz 28nm 1100+ DMIPS Dual 405 Cores 450+ MHz 700+ DMIPS 405 Core 300+ MHz 450+ DMIPS 65nm 90nm 130nm 2001 2003 2005 2007 2012 10+ years, 4 Generations …. Zynq-7000 AP SoC Basic Architecture Processing System Memory Interfaces Xilinx Soft Accelerators Built-in Peripherals ARM® Custom Accelerators Dual Cortex-A9 MPCore™ System Xilinx Soft Peripherals Custom Peripherals 7 Series Programmable Logic Zynq-7000 AP SoC Block Diagram 1 1 2 37926**slid e .x17 Connecting HW and SW DDR Memory ARM Cortex-A9 MPCore PL Peripheral 1 PL Peripheral 2 Hardware Designer Perspective Peripheral blocks can be standard core offerings or custom logic cores Logic controls exposed to Processor System via register interface PL Peripheral 3 Fixed I/O Peripherals 256KB OCM Programmable Logic 0x00000000 Software Developer Perspective Processor System controls Programmable Logic blocks via exposed register interface Standard address-mapped architecture similar to any other ASSP Processor Address Space DDR Memory PL Peripheral 1 PL Peripheral 2 PL Peripheral 3 Fixed I/O Peripherals 256KB OCM 0x40000000 0x60000000 0x80000000 0xE0000000 0xFC000000 Parallel Developments of your AP SoC Based Application Software Development ● Processor boots first like any ARM based SoC. ● SW developers can use their favorite SW tool to load / debug SW code over JTAG ● Programmable Logic can be left unconfigured while developing on real hardware SW developments like any other ARM based SoC Hardware Development ● ● ● Reference SW boots processor first leaving PL up and ready to be programmed through JTAG Vivado Probe connects to Programmable Logic like to any other FPGA FPGA developer can start loading / debug like for any FPGA HW developments like any other Xilinx FPGA Extensive OS, Middleware & Stack Ecosystem Middleware and Stacks Operating Systems Linux and OSE Linux and VxWorks Open Source Linux & Commercial Linux Hypervisors Zynq-7000 Device Portfolio Summary Scalable platform offers easy migration between devices MicroZed ZedBoard Zynq Prototyping and Production Solutions We’ve got you covered! ● ZedBoard ● ZC702 ● ZC706 ● MicroZed ● Zynq MMP ● Zynq Mini-ITX ● IVK ● SDR Xilinx Embedded Tool Flow ● Vivado Design Suite WebPACK Edition o FREE! o Supports four Zynq devices: 7010, 7015, 7020 and 7030 Pillars of Productivity Features IP Integration and Implementation Verification and Debug Design Exploration and IP ●Generation WebPACK Design Edition System Edition Free 30-day Eval Integrated Design Environment √ √ √ √ Software Development Kit (SDK) √ √ √ √ Vivado Simulator √ √ √ √ Vivado Logic Analyzer √ √ √ Vivado Serial Analyzer √ √ √ High-Level Synthesis √ √ System Generator for DSP √ √ ● MicroZed and ZedBoard include license for Vivado Analyzer Objectives ● Introduce Avnet Silica ● Understand the Zynq-7000 All Programmable SoC architecture ● Introduce the Vivado High Level Synthesis o Automatic conversion from C/C++ to VHDL/Verilog Increased System Performance ● Increasing SW Processing Performance with: o Programmable Logic o Massive DSP processing o High throughput AXI Over 3000 PS to PL direct connections o High performance I/Os o Gigabit transceivers Elements Performance (up to) Processors (each) 1 GHz PL Fabric/ DSP Fmax 741 MHz DSP (aggregate) 1080 GMACs Transceivers (each) 12.5Gbps Increased System Performance ● Optimized & Simplified HW/SW Partitioning o HW acceleration enables scaling SW performance to address many applications o Low latency interfacing for efficient co-processor implementation and high throughput data transfers C C HDL