Output Termination Options for the Si500S and Si500D Silicon

advertisement

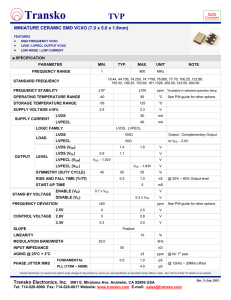

AN409 O UTPUT TERMINATION O PTIONS FOR TH E Si500S AND Si500D S I L I C O N O SC ILLA TORS 1. Introduction The Si500D Silicon Oscillator can be ordered with one of five different output buffer types: CMOS, SSTL, LVPECL, LVDS, or HCSL. Each output type has its own particular benefits and limitations. This document describes each buffer type, proper biasing and termination schemes, and related technical trade-offs. 2. CMOS Complementary metal-oxide semiconductor (CMOS) totem pole output buffers are used to drive capacitive loads to CMOS logic levels. The Si500 CMOS driver output impedance is a nominal 36 . An external series resistor can be added to provide optimum impedance matching with higher impedance traces as shown in Figure 1. Unlike most CMOS output drivers, the Si500 provides two outputs which can be ordered as complementary or inphase. When in-phase, the two outputs may be shorted together to produce a single nominal 18 driver to drive large capacitive loads. The CMOS option can be ordered for all three of the supported supply levels (1.8, 2.5, and 3.3 V). Figure 1. Example of External Source Termination Resistors to Improve Trace Impedance Matching Rev. 0.2 5/10 Copyright © 2010 by Silicon Laboratories AN409 AN409 3. SSTL SSTL (Stub Series Terminated Logic) is an electrical interface commonly used with DDR (Double Data Rate) DRAM memory ICs and memory modules. The Si500 support 3.3, 2.5, and 1.8 V SSTL outputs which can be single-ended, differential, or in-phase. The termination scheme for SSTL is shown in Figure 2. VTT VTT 50 50 VDD VDD 2.43 k 2 k 0.50*VDD VTT 2 k 0.45*VDD VTT 2 k 0.1 uF Practical VTT for SSTL-2, SSTL-18 Practical VTT for SSTL-3 Figure 2. SSTL Termination Schemes 2 0.1 uF Rev. 0.2 AN409 4. LVPECL Low-voltage positive emitter-coupled logic (LVPECL) differential outputs are typically chosen for their superior jitter performance. The Si500 devices offer two LVPECL options: a standard LVPECL option and a low-power LVPECL output option for ac coupling only. LVPECL is offered with both 3.3 V and 2.5 V supplies. The standard LVPECL output option requires external biasing and proper termination of 50 to VDD-2 V for each side of the differential output. Many well-known LVPECL biasing and termination schemes are supported by the Si500 devices. The most common are shown in Figures 3, 4, and 5. The primary disadvantages of this output format are increased power consumption (due to dc biasing) and incompatibility with 1.8 V supplies. The primary advantage of the LVPECL signal format is jitter performance. LVPECL provides the best jitter performance because of its large swing and fast edge rates. 50 50 50 50 VDD-2V Figure 3. Traditional Biasing and Termination for Standard LVPECL Output Option R1 R1 3.3V LVPECL R1 = 130 , R2 = 82 2.5V LVPECL R1 = 250 , R2 = 62.5 R2 R2 Figure 4. Alternative Biasing and Termination for Standard LVPECL Output Option Rev. 0.2 3 AN409 0.1 µF 130 100 130 Figure 5. Alternative Biasing and Termination for Standard LVPECL Output Option (100 Line Termination May Be Internal to the Receiving IC) The low-power LVPECL option eliminates the need for external dc biasing, which reduces overall power consumption without sacrificing jitter performance. 100 0.1 µF Figure 6. Termination for Low-Power LVPECL Option (100 Line Termination May be Internal to the Receiving IC) 4 Rev. 0.2 AN409 5. LVDS Low-voltage differential signaling (LVDS) differential outputs are typically chosen for their ease of use. LVDS is a common input and output type used with FPGAs. LVDS outputs require no external biasing or termination when connected to LVDS inputs and are very power-efficient. Also, the LVDS specification allows for significant dc biasing drift from transmitter to receiver, further simplifying system-level design. LVDS outputs are connected as shown in Figure 7. 100 Figure 7. Typical Transmission Line Connection for LVDS (100 Line Termination May Be Internal to the Receiving IC) 6. HCSL High-Speed Current Steering Logic (HCSL) outputs are commonly used for PCI Express applications. The Si500D integrates the 50 termination resistors to ground, simplifying the connection to an HCSL receiver. 50 50 50 50 Internal To HCSL Output Driver Figure 8. HCSL Connection Using Internal Termination Resistors Rev. 0.2 5 ClockBuilder Pro One-click access to Timing tools, documentation, software, source code libraries & more. Available for Windows and iOS (CBGo only). www.silabs.com/CBPro Timing Portfolio www.silabs.com/timing SW/HW Quality Support and Community www.silabs.com/CBPro www.silabs.com/quality community.silabs.com Disclaimer Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Trademark Information Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders. Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA http://www.silabs.com