Metal Oxide Semiconductor (MOS) Capacitor

advertisement

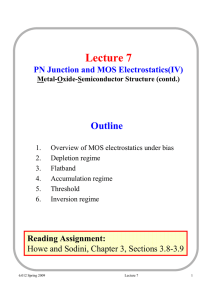

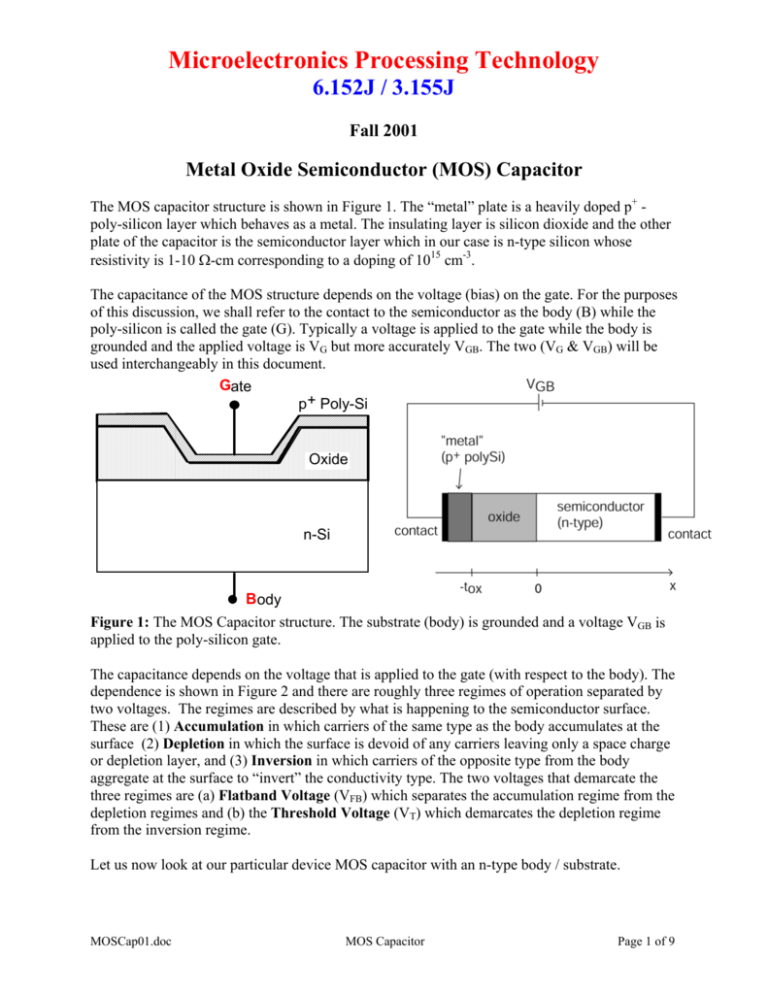

Microelectronics Processing Technology 6.152J / 3.155J Fall 2001 Metal Oxide Semiconductor (MOS) Capacitor The MOS capacitor structure is shown in Figure 1. The “metal” plate is a heavily doped p+ poly-silicon layer which behaves as a metal. The insulating layer is silicon dioxide and the other plate of the capacitor is the semiconductor layer which in our case is n-type silicon whose resistivity is 1-10 Ω-cm corresponding to a doping of 1015 cm-3. The capacitance of the MOS structure depends on the voltage (bias) on the gate. For the purposes of this discussion, we shall refer to the contact to the semiconductor as the body (B) while the poly-silicon is called the gate (G). Typically a voltage is applied to the gate while the body is grounded and the applied voltage is VG but more accurately VGB. The two (VG & VGB) will be used interchangeably in this document. Gate p+ Poly-Si Oxide n-Si Body Figure 1: The MOS Capacitor structure. The substrate (body) is grounded and a voltage VGB is applied to the poly-silicon gate. The capacitance depends on the voltage that is applied to the gate (with respect to the body). The dependence is shown in Figure 2 and there are roughly three regimes of operation separated by two voltages. The regimes are described by what is happening to the semiconductor surface. These are (1) Accumulation in which carriers of the same type as the body accumulates at the surface (2) Depletion in which the surface is devoid of any carriers leaving only a space charge or depletion layer, and (3) Inversion in which carriers of the opposite type from the body aggregate at the surface to “invert” the conductivity type. The two voltages that demarcate the three regimes are (a) Flatband Voltage (VFB) which separates the accumulation regime from the depletion regimes and (b) the Threshold Voltage (VT) which demarcates the depletion regime from the inversion regime. Let us now look at our particular device MOS capacitor with an n-type body / substrate. MOSCap01.doc MOS Capacitor Page 1 of 9 C MOS Cmax CQS C HF Cmax=Cox C min C MOS(VT)=Cmin VFB VT Inversion Depletion VGB Accumulation Figure 2: Capacitance per unit area vs. Gate Voltage (CV) diagram of a MOS Capacitor. The flatband voltage (VFB) separates the Accumulation region from the Depletion regime. The threshold voltage (VT) separates the depletion regime from the inversion regime. CHF is high frequency capacitance while CQS is quasi-static or low frequency capacitance. Surface Accumulation (VGB > VFB) An applied positive gate voltage larger than the flatband voltage (which will be defined shortly) (VGB > VFB) induces positive charge on the “metal” gate and negative charge in the semiconductor. The only negative charges available are electrons and they accumulate at the surface. The electron concentration at the surface is above the bulk value, thus leading to a condition that is called surface accumulation. The charge distribution and equivalent circuit is shown in Figure 3. The flatband voltage (VFB) is the voltage at which there is no charge on the plates of the capacitor and hence there is no electric field across the oxide. It’s numerical value depends on the doping of the semiconductor and on any residual interface charge that may exist at the interface between the semiconductor and the insulator. When the surface of the semiconductor is accumulated, a plot of the charge per unit area (QN) at the semiconductor / oxide interface versus the applied voltage (VGB) is linear and the slope is the oxide capacitance per unit area., Cox., which is given by ε C MOS ,accumulation = C max = C ox = ox t ox where εox is the permittivity of the oxide and it is 3.9εo. εo is the permittivity of free space or air. εo = 8.854x10-14 Fcm-1. The unit for Cox is Fcm-2. Figure 4 is a plot of the charge per unit area (QN) as a function of the applied voltage (VGB). MOSCap01.doc MOS Capacitor Page 2 of 9 charge density ρ + + + + + - - - - - Oxide Silicon Oxide 0 - - - - - G + + + + + Poly-Si -tox B x Cox Figure 3: Charge distribution in a MOS Capacitor biased into accumulation. The electron distribution at the Si/SiO2 interface could be approximated as a δ-distribution. Figure 4: Accumulation charge density as a function of the applied voltage. The slope of the line is the oxide capacitance per unit area, Cox. Surface Depletion (VT < VGB < VFB) If the applied gate voltage is brought below the flat band voltage (remember the flat band voltage is the gate voltage at which there is no charge in the MOS capacitor), a negative charge is induced at the interface between the poly-silicon gate and the oxide. This leads to a positive charge being induced at the other interface i.e. the oxide / semiconductor interface. This could only be accomplished by “pushing” all the mobile negative carriers (electrons) away and exposing the fixed positive charge from the donors. Hence the surface of the semiconductor is depleted of mobile carriers leaving behind a positive space charge. Figure 5 shows the charge distribution under these circumstances. The space charge layer resulting behaves also like a capacitor having a capacitance per unit area (CD), which depends on VGB and is given by MOSCap01.doc MOS Capacitor Page 3 of 9 C D (VGB ) = ε Si x d (VGB ) where εSi is the permittivity of the silicon and it is 11.7εo. εo is the permittivity of free space or air. εo = 8.854x10-14 Fcm-2. xd is the depleted silicon layer thickness. The unit of CD is Fcm-2. From Figure 5, we observe that the oxide capacitance per unit area (Cox) and depleted silicon capacitance per unit area (CD) are connected in series. Thus the capacitance of the MOS structure when it is in the surface depletion regime is given by 1 1 1 = + C depletion C ox C D ⇒ C MOS ,depletion = C depletion = C ox C D C ox + C D The unit for Cdepletion is Fcm-2. The silicon depletion layer thickness increases as the gate voltage is decreased because more electrons are pushed away exposing more fixed positive ionized dopants leading to thicker space charge layer. The capacitance of the depleted silicon decreases and hence the MOS capacitance decreases as the gate voltage is decreased. charge density Poly-Si Mobile electrons Ionized Donors G Oxide - - - - + + + + + Ionized Donors n-Si B Oxide Mobile Electrons - - - - - p+-poly ρ -tox + + + + + xd 0 x Silicon Cox CD Figure 5: Charge distribution in a MOS Capacitor biased into depletion and the equivalent circuit diagram. xd is the depleted silicon layer thickness. MOSCap01.doc MOS Capacitor Page 4 of 9 Surface Inversion (VGB < VT) If the applied gate voltage is lowered below the threshold voltage (VT), the semiconductor surface inverts its conduction type from n-type to p-type in our particular situation. It is natural to ask why such a thing would occur? Before answer the question let us define the threshold voltage (VT) as the gate voltage at which the conductivity type of the surface layer changes from n-type to p-type because more holes have been attracted to the surface that the number of electrons that existed at the surface at flatband. It demarcates the depletion region from the inversion region. We shall now proceed to answer the question about why the surface inverts. Starting from flatband, as the gate voltage is lowered negative mobile carriers (electrons) are “pushed away” from the Si/SiO2 interface, a positive space charge is exposed. We approximate this as a depletion layer in which we make the assumption that the layer is devoid of all mobile carriers. However, this is only an approximation. What happens in reality is that the density of electrons decreases exponentially from the surface going into the bulk. An important fact pertinent to this discussion is that we assumed that system is in quasi-equilibrium, hence the law of mass action p o n o = n i2 is still valid. Thus at the surface, the number of electrons decreases as the applied voltage decreases. Correspondingly, the number of holes at the surface increases as the applied gate voltage decreases. This is depicted in Figure 6. At a particular voltage called the threshold voltage (VT) the concentration of holes at the surface exceeds the concentration of electrons in the bulk. The conductivity type of the silicon surface is inverted. Figure 7 shows the charge distribution of the MOS capacitor in inversion. There is a mobile charge delta-distribution at the silicon / silicon dioxide interface. Additional increases in the applied gate voltage only leads to a linear increase in the charge per unit area of the inversion layer. Figure 8 shows the dependence of the charge density on the applied gate voltage. The inversion layer charge density is given by Q P = −C ox [VGB − VT ] (Ccm −2 ) The above expression for the hole density in the inversion layer will be used when considering the p-MOSFET. An important fact we need to state is that once the inversion layer forms, the depletion layer thickness reaches a maximum. The total voltage drop across the semiconductor is “pinned” at a maximum value. Increases in the gate voltage applied to the structure is dropped mostly across the oxide layer as reflected by the expression for inversion layer charge. Thus when the gate voltage is equal to the threshold voltage, the depleted layer capacitance per unit area reaches a minimum CDmin and likewise the MOS capacitance. This capacitance is Cmin and it is given by C MOS (VT ) = C min = C depletion,min = C ox C D min C ox + C D min where C D min = MOSCap01.doc ε Si x d max MOS Capacitor Page 5 of 9 Figure 6: Semilog plots of the carrier concentration distribution for the MOS capacitor in (a) accumulation, (b) flatband, (c) depletion and (d) inversion. MOSCap01.doc MOS Capacitor Page 6 of 9 charge density ρ p+-poly G - - - - + + + + + + + + + + Ionized Donors n-Si Poly-Si Oxide Oxide Holes Mobile Electrons B - - - - - Mobile electrons -tox Holes at interface + + + + + Poly-Si 0 Ionized Donors + + + + + xdmax x Silicon Cox CDmin Figure 7: Charge distribution in a MOS Capacitor biased into inversion. The hole distribution at the Si/SiO2 interface could be approximated as a δ-distribution. Figure 8: Inversion layer hole charge density as a function of the applied voltage (low frequency & quasi-static situation). The slope of the line is the oxide capacitance per unit area, Cox. Where do the holes that form the inversion layer come from? In a MOS capacitor in depletion or inversion, the holes and electrons are generated in the depleted silicon surface region. The holes are attracted to the Si/SiO2 interface while the electrons are “pushed” into the substrate. However the holes could also come from a p-doped region that is in close proximity to the MOS capacitor such as the source/drain region of a p-MOSFET. What are the expressions for xd and xdmax? I will not try to derive the equations that give you xd and xdmax because they are rather involved, but I will have give you the expressions. If you will like to derive it, I will refer you to 6.012 Text. Microelectronics: An Integrated Approach, Howe and Sodini. MOSCap01.doc MOS Capacitor Page 7 of 9 x d (VGB ) = ε Si C ox 2 (φ B + VGB ) 2C ox − 1 1+ ε Si qN D where φ B = (φ m − φ n ) = φ p + − φ n φ p + = −0.55 V φn = N kT • ln D q ni x d (VT ) = x d max = 2ε Si • 2φ n qN D The next question to be asked is that why are there two values of capacitance at any voltage in the inversion regime? The capacitance of the structure is usually measured by imposing a DC bias voltage which in our case will be VGB superposed on the DC bias is a small signal which is an alternating current (ac). This could be a high frequency ac signal (f=1 MHz) or low frequency signal (f<1 kHz). The frequency of the signal affects the capacitance versus voltage (CV) curve for an MOS capacitor. The capacitance depends on the measurement frequency and what other structures are connected to the basic MOS capacitor. At very low frequencies (sometimes referred to as quasi-static conditions), the generation rate of holes (and electrons) in the depleted silicon surface layer is fast enough and hence holes are swept to the Si/SiO2 interface where the thin layer holes forms a sheet of charge. Thus the inversion layer capacitance per unit area under quasi-static conditions is given C MOS ,inversion,QS = ε ox = C max t ox At high frequencies, the generation rate is not fast enough to allow the formation of a hole charge density at the Si/SiO2 interface. In this case the silicon surface depletion layer thickness is still at it’s maximum value xdmax and the corresponding inversion layer capacitance per unit area at high frequency is Cmin and it is given by C MOS ,inversion,HF = C min = C depletion,min = C ox C D min C ox + C D min The inversion layer capacitance of a p-MOSFET even at high frequencies has the same value as the quasi-static MOS capacitor (Cmax) because there is a ready supply of holes coming from the p-type source/drain regions that are in close proximity. MOSCap01.doc MOS Capacitor Page 8 of 9 What are the flatband and threshold voltages? Flatband Voltage In theory, the flatband voltage should be ( VFB =− φ B = −(φ m − φ n ) = − φ p + − φ n ) φ p + = −0.55 V φn = N kT • ln D q ni In real devices, there is a positive charge located at the Si/SiO2 interface and it modifies the equation thus VFB =− (φ m − φ n ) − Q I t ox ε ox where QI is the Si/SiO2 interface charge density (# cm-2) Threshold Voltage VT =VFB − 2φ n − t ox ε ox 2ε Si qN D (2φ n ) φm = φp+ is the gate (metal) potential φn is the potential of n-Si substrate ni is the intrinsic carrier concentration of Si tox is oxide thickness εox , εSi the oxide & Si dielectric constants ND is the substrate doping QI is the oxide charge density at the interface MOSCap01.doc MOS Capacitor Page 9 of 9