AC701 Ethernet Design

Creation

November 2014

XTP223

Revision History

Date

Version Description

11/24/14

10.0

Regenerated for 2014.4.

10/08/14

9.0

Regenerated for 2014.3.

06/09/14

8.0

Regenerated for 2014.2.

04/16/14

6.0

Regenerated for 2014.1.

12/18/13

5.0

Regenerated for 2013.4.

10/23/13

4.0

Regenerated for 2013.3.

06/19/13

3.0

Regenerated for 2013.2. AR55738 fixed.

04/03/13

2.0

Regenerated for 2013.1. AR54163 and AR54165 fixed. Added AR55738.

02/04/13

1.1

As per AR54044, added 2012.4 device pack. Added AR54163, AR54165, and AR54223.

12/18/12

1.0

Initial version.

© Copyright 2014 Xilinx, Inc. All Rights Reserved.

XILINX, the Xilinx logo, the Brand Window and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of

their respective owners.

NOTICE OF DISCLAIMER: The information disclosed to you hereunder (the “Information”) is provided “AS-IS” with no warranty of any kind, express or implied.

Xilinx does not assume any liability arising from your use of the Information. You are responsible for obtaining any rights you may require for your use of this

Information. Xilinx reserves the right to make changes, at any time, to the Information without notice and at its sole discretion. Xilinx assumes no obligation to

correct any errors contained in the Information or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical

support or assistance that may be provided to you in connection with the Information. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS,

IMPLIED, OR STATUTORY, REGARDING THE INFORMATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR

PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

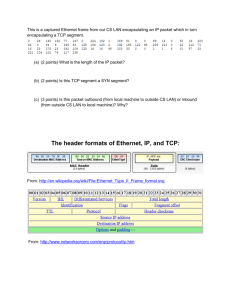

Overview

AC701 Board

AC701 Setup

Generate RGMII Ethernet Example Design

Modifications to Example Design

Compile Example Design

Run RGMII Ethernet Example Design

References

Note: This presentation applies to the AC701

Artix-7 Ethernet Capability

AC701 Supports RGMII Capability

– RGMII demonstrated in this tutorial

– Board TX to Host

LogiCORE Ethernet Example Design

– AC701 Ethernet Design Files (2014.4 C) ZIP file

– Available through http://www.xilinx.com/ac701

LogiCORE IP Tri-Mode Ethernet MAC

– See PG051 for details

Note: Presentation applies to the AC701

Xilinx AC701 Board

Vivado Software Requirements

Xilinx Vivado Design Suite 2014.4, Design Edition

Note: Presentation applies to the AC701

IP License Requirements

IP licenses are needed to compile the design in this tutorial:

– LogiCORE, Ethernet AVB Endpoint, Evaluation License

– LogiCORE, Tri-Mode Ethernet MAC, Evaluation License

– LogiCORE, Tri-Mode Ethernet Media Access Controller, Evaluation License

– Available free of charge at http://www.xilinx.com/getlicense

Wireshark Software Requirement

Wireshark Protocol Analyzer available at http://www.wireshark.org/

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Open Vivado

Start → All Programs → Xilinx Design Tools → Vivado 2014.4 → Vivado

Select Create New Project

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Click Next

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Set the Project name and location to ac701_ethernet and C:/

– Check Create Project Subdirectory

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Select RTL Project

– Select Do not specify sources at this time

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Select the AC701 Board

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Click Finish

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Click on IP Catalog

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Select Tri Mode Ethernet MAC v8.3 under Communication &

Networking

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Right click on Tri Mode Ethernet MAC

– Select Customize IP

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Make the following

settings

– Set Component

Name:

ac701_ethernet_rg

mii

– Set the Board

Interfaces:

– ETHERNET: rgmii

– MDIO: mdio io

– Click Interface Tab

Generate Ethernet Example Design

Make the following

settings

– Select Tri speed

– Click Features Tab

Generate Ethernet Example Design

Make the following

settings

– De-select Half

Duplex, AVB,

Frame Filter, and

Statistics Counters

– Click OK

Generate Ethernet Example Design

Click Generate

Note: Presentation applies to the AC701

Generate Ethernet Example Design

Ethernet design appears in Design Sources

– Wait until checkmark appears on ac701_ethernet_rgmii_synth_1

Note: Presentation applies to the AC701

Compile Example Design

Right click on ac701_ethernet_rgmii and Open IP Example Design…

Note: Presentation applies to the AC701

Compile Example Design

Set the location to C:/ac701_ethernet and click OK

Note: Presentation applies to the AC701

Compile Example Design

A new project is created

Click on Generate Bitstream

Note: The original project window can be closed

Compile Example Design

Open and view Implemented Design

Note: Presentation applies to the AC701

Setup for the AC701 Designs

Connect a USB Type-A to Micro-B cable to the USB JTAG (Digilent)

connector on the AC701 board

– Connect this cable to your PC

– Power on the AC701 board

Setup for the AC701 Designs

Connect a Ethernet cable to the AC701

– Connect this cable to your PC

AC701 Setup

Set S2 to 1100 (1 = on,

Position 1 → Position 4)

This selects Gigabit

Ethernet, with the packet

generator off

Run Ethernet Example Design

Click Open Hardware Manager

Note: Presentation applies to the AC701

Run Ethernet Example Design

Click Open target and select Auto Connect

Note: Presentation applies to the AC701

Run Ethernet Example Design

Select Program device → xc7a200t_0

Note: Presentation applies to the AC701

Run Ethernet Example Design

The newly created bitstream is default

Click Program

Note: Presentation applies to the AC701

Run Ethernet Example Design

Open Wireshark

– Set the Filter to: eth.addr == da:01:02:03:04:05; click Apply

– Select the Ethernet NIC and click Start

Run Ethernet Example Design

Open your Network and Sharing Center control panel

Click on Change adapter settings

Note: Presentation applies to the AC701

Run Ethernet Example Design

Right click on the Gigabit network connection and select Status

The status dialog will show you the speed and number of packets

Note: Presentation applies to the AC701

Run Ethernet Example Design

Wireshark should show no packets

Run Ethernet Example Design

Set S2 to 1110 (1 = on,

Position 1 → Position 4) for

a moment to run the packet

generator

Set S2 back to 1100

Run Ethernet Example Design

The status dialog shows a few packets received

Note: Presentation applies to the AC701

Run Ethernet Example Design

Wireshark captures and displays the actual packets

Run Ethernet Example Design

Use the arrow keys to move to the next packet

Run Ethernet Example Design

Viewing several packets, you can see a simple changing pattern

References

References

Tri-Mode Ethernet Media Access Controller

– Tri-Mode Ethernet MAC Product Overview

• http://www.xilinx.com/products/intellectual-property/TEMAC.htm

– LogiCORE IP Tri-Mode Ethernet MAC Product Guide – PG051

• http://www.xilinx.com/support/documentation/ip_documentation/

tri_mode_ethernet_mac/v8_3/pg051-tri-mode-eth-mac.pdf

Documentation

Documentation

Artix-7

– Artix-7 FPGA Family

• http://www.xilinx.com/products/silicon-devices/fpga/artix-7/index.htm

– Design Advisory Master Answer Record for Artix-7 FPGAs

• http://www.xilinx.com/support/answers/51456.htm

AC701 Documentation

– Artix-7 FPGA AC701 Evaluation Kit

• http://www.xilinx.com/products/boards-and-kits/EK-A7-AC701-G.htm

– AC701 Getting Started Guide

• http://www.xilinx.com/support/documentation/boards_and_kits/ac701/2014_1/

ug967-ac701-eval-kit-getting-started.pdf

– AC701 User Guide

• http://www.xilinx.com/support/documentation/boards_and_kits/

ac701/ug952-ac701-a7-eval-bd.pdf