1 DEVELOPMENT OF THE INTEL X86 FAMILY MICROPROCESSOR

advertisement

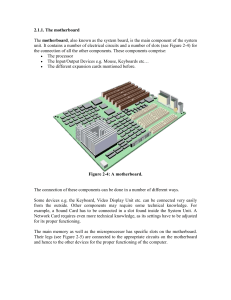

DEVELOPMENT OF THE INTEL X86 FAMILY MICROPROCESSOR DEVELOPMENT OF THE INTEL X86 FAMILY MICROPROCESSOR 13.1 13.2 13.3 13.4 13.5 13.6 Introduction Programming Model Addressing Modes Instruction Set The X86 Hardware PC Motherboard Architecture 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-2 13.1 Introduction 13.1 Introduction The 8088 and 8086 evolved into faster versions, The 486 is basically a large integrated circuit which versions with greater memory addressing space, versions which process 32-bit data words. IBM introduced the PC/AT using the 80286 in 1984. One of the features introduced with the 80286 was real and protected modes of operation, and yet another feature added hardware multitasking. The 80386 has a 32-bit data bus and a 32-bit address bus, and it uses 32-bit internal registers. The 386 microprocessors offered advance virtual memory, advanced protected mode, and higher speeds. contains a fast 386 processor, a math coprocessor, a memory management unit (MMU), and an 8-Kbyte cache memory. The 486 achieves its high-speed operation from faster clock speeds, an internal pipelined architecture, and the use of reduced instruction set computing (RISC) to speed up the internal microcode. Intel elected to name the 586 device Pentium. The Pentium uses superscalar architecture incorporating a dual-pipelined processor which lets the Pentium process more than one instruction per clock cycle. 611 37100 微處理機原理與應用 Lecture 13-3 國立台灣大學 生物機電系 林達德 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-4 13.1 Introduction 13.1 Introduction The Pentium are implemented with 8-Kbyte data and Major attributes of the X86 processors 8-Kbyte code caches on chip that is also a feature designed to improve processing speed. The Pentium has a 64-bit data bus. This means that it can perform data transfers with an external device twice as fast as a processor with a 32-bit data bus. A new advanced computing technique used in the Pentium is called branch prediction. Using branch prediction, the Pentium makes an educated guess where the next instruction following a conditional instruction will be. 611 37100 微處理機原理與應用 Lecture 13-5 國立台灣大學 生物機電系 林達德 Attribute 8088 8086 80286 611 37100 微處理機原理與應用 Lecture 13-6 386SX 386DX 486SX 486DX Pentium 國立台灣大學 生物機電系 林達德 1 13.2 Programming Model 13.2 Programming Model The 8088 and 8086 define the base programming model for the entire X86 family of microprocessors. The 386, 486, and Pentium uses 32-bit registers. The 8 general-purpose registers are called the EAX, EBX, ECX, EDX, ESI, EDI, ESP, EBP registers. Each register can be addressed in 1-, 8-, 16-, or 32-bit modes. The first five bits of the X86 flag register are identical to the flag bits in the 8085 8-bit microprocessor. To give the X86 processors even greater speed, the processors include various levels of instruction prefetching and data caching. 611 37100 微處理機原理與應用 Lecture 13-7 國立台灣大學 生物機電系 林達德 13.2 Programming Model base register set 611 37100 微處理機原理與應用 Lecture 13-8 國立台灣大學 生物機電系 林達德 13.3 Addressing Modes The X86 flag (status) register 8086 611 37100 微處理機原理與應用 Lecture 13-9 The X86 programming model as described by the 8085 國立台灣大學 生物機電系 林達德 The X86 processors can address immediate data, I/O ports, registers, and memory locations using different addressing modes. The 8088/8086 addresses 1 Mbyte (220). The 286 addresses 16 Mbytes (224), and members after the 386 can address 4 Gbytes (232). The X86 processors have a separate ALU to perform calculation of memory address, so the main ALU is free to perform data calculation. Each of the newer X86 processors has two fundamental modes of operation. They are called the real mode and protected mode. 611 37100 微處理機原理與應用 Lecture 13-10 國立台灣大學 生物機電系 林達德 13.3 Addressing Modes 13.3 Addressing Modes In the real mode, all processors are limited to In the protected mode, the address in the segment addressing 1 Mbyte of memory. In this mode they work just like the 8086. In the protected mode, they are able to address many more memory locations. To put an X86 processor in the protected mode, the protection enable bit (bit 0) in the machine status register must be set to logic 1. Once the protection enable bit is set, it can be cleared only by resetting the processor. This makes entering the protected mode a one-way street. In the protected mode, the X86’s MMU is used to allow the processor to address physical memory greater than 1 Mbyte and to allow the programmer to use virtual memory. 611 37100 微處理機原理與應用 Lecture 13-11 國立台灣大學 生物機電系 林達德 register points to a memory location called a segment descriptor table. Data in this table is used in place of the segment base address data to build the memory address. The segment descriptor table gives the X86 programmer one more way to keep different addressing for different kinds of use and therefore to protect the data. 611 37100 微處理機原理與應用 Lecture 13-12 國立台灣大學 生物機電系 林達德 2 13.3 Addressing Modes 13.3 Addressing Modes The upper 13 bits of the segment register data are Each segment descriptor table contains 8 bytes. The used to select a particular segment descriptor. The first three bits request a priority level (RPL0, RPL1) and select either a global descriptor table or a local descriptor table. 3 2 1 8 bytes provide a 24-bit (286) or 32-bit (386 and higher) segment base address plus additional information. 0 13-bit segment description address RPL0 RPL1 GDT or LDT The structure of the segment descriptor table 611 37100 微處理機原理與應用 Lecture 13-13 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-14 國立台灣大學 生物機電系 林達德 13.3 Addressing Modes 13.3 Addressing Modes Addressing memory using the segment descriptor There is one segment descriptor register for each tables segment register. If the memory does not really exist, then a subprogram is used to load the needed information from mass storage into the appropriate section of physical memory. Segments for the 286 are limited to 64 Kbytes. Segments for the 386 and newer processors can be either up to 1 Mbyte or up to 4 Gbytes long. The X86 processors offer four levels of privilege for any form of memory access. This is used to help the programmer when writing operation system software and software for a multi-user or multitasking environment. 611 37100 微處理機原理與應用 Lecture 13-15 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-16 國立台灣大學 生物機電系 林達德 13.3 Addressing Modes 13.3 Addressing Modes The X86 privilege levels. PL0 is the highest privilege; Different privilege layers for a multi-user or PL3 is the lowest privilege. multitasking operating system. PL3 Applications PL2 Operating systems PL1 System PL0 Kernel – most privilege Services Extensions Software 611 37100 微處理機原理與應用 Lecture 13-17 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-18 國立台灣大學 生物機電系 林達德 3 13.4 Instruction Set 13.4 Instruction Set The X86 processors are upwardly compatible; that Evolution of the X86 family instruction set Protected mode is, software written for an earlier version will always run on a later version. The newer processors have a special mode (the real mode) which allows them to operate as though they were an 8086. There are eight major types of X86 instructions: Real mode Base Instruction set 國立台灣大學 生物機電系 林達德 13.4 Instruction Set 611 37100 微處理機原理與應用 Lecture 13-21 80386 80286 8086 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-20 386 486 The X86 data transfer instructions Instruction Subtype 國立台灣大學 生物機電系 林達德 Mnemonic Description 8088/ 8086 286 386 486 國立台灣大學 生物機電系 林達德 13.4 Instruction Set The X86 data transfer instructions – some The X86 arithmetic instructions new instructions Mnemonic Description POPA, PUSHA – Exchange all register data with the stack. BSWP – Byte swap, reorder the 4 bytes in a 32bit word. LAR – Load the access rights from a segment descriptor table into a general-purpose register. LGDT, LIDT, LLDT, SGDT, SIGT, SLGT – Transfer the contents of a segment descriptor table (Global, Interrupt, Local). LMSW – Load machine status word. 國立台灣大學 生物機電系 林達德 Instruction Subtype 611 37100 微處理機原理與應用 Lecture 13-22 13.4 Instruction Set 611 37100 微處理機原理與應用 Lecture 13-23 80486 13.4 Instruction Set The X86 data transfer instructions 286 Base Base ++ extended Extended + 80386 Specific Instruction Instruction set set System control Instruction set Base Base ++ extended extended Instruction Instruction set set 611 37100 微處理機原理與應用 Lecture 13-19 8088/ 8086 System control Instruction set Real mode System control Instruction set + BaseBase + Extended extended + 80386 + 80486 Specific Instruction Instruction set set Protected mode Protected mode Data transfer Arithmetic Logical and shift-rotate String manipulation Bit manipulation Control transfer High-level language support Processor control Mnemonic Description Real mode 8088/ 8086 611 37100 微處理機原理與應用 Lecture 13-24 286 386 486 Instruction Subtype 國立台灣大學 生物機電系 林達德 4 13.4 Instruction Set 13.4 Instruction Set The X86 arithmetic instructions The X86 logical instructions Mnemonic Description 8088/ 8086 286 386 486 Instruction Subtype Mnemonic 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-25 Description 8088/ 8086 286 386 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-26 13.4 Instruction Set 13.4 Instruction Set The X86 shift and rotate instructions The X86 string manipulation instructions Mnemonic Mnemonic Description 8088/ 8086 286 386 8088/ 8086 286 13.4 Instruction Set The X86 bit manipulation instructions The X86 control transfer instructions Mnemonic Description 611 37100 微處理機原理與應用 Lecture 13-29 8088/ 8086 286 386 國立台灣大學 生物機電系 林達德 486 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-28 13.4 Instruction Set Mnemonic 386 486 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-27 Description 486 Description 8088/ 8086 286 386 486 Instruction Subtype 486 611 37100 微處理機原理與應用 Lecture 13-30 國立台灣大學 生物機電系 林達德 5 13.4 Instruction Set 13.4 Instruction Set The X86 control transfer instructions – Five The X86 control transfer instructions – Five unconditional jumps unconditional jumps 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-31 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-32 13.4 Instruction Set 13.4 Instruction Set The X86 control transfer instructions – Four iteration The X86 control transfer instructions – Interrupt vector control instructions Interrupt Vector Number Interrupt Type 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-33 Instruction or Condition Which Can Cause Interrupt First Processor to Use This Interrupt 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-34 13.4 Instruction Set 13.4 Instruction Set The X86 high-level language support instructions The X86 processor control instructions Mnemonic Mnemonic Description 611 37100 微處理機原理與應用 Lecture 13-35 8088/ 8086 286 386 國立台灣大學 生物機電系 林達德 Description 8088/ 8086 286 386 486 Instruction Subtype 486 611 37100 微處理機原理與應用 Lecture 13-36 國立台灣大學 生物機電系 林達德 6 13.5 The X86 Hardware 13.5 The X86 Hardware The maximum and minimum mode of the 8088/8086 Typical packages of newer X86 processors was dropped from the 286 and from later versions of the X86 processor family. The 286 and newer processors do not use a multiplexed address-data bus. The newer microprocessors in the X86 family are usually packaged as: Pin grid array (PGA) Quad flat pack (QFP) Plastic leadless chip carrier (PLCC) A 114-pin pin grid array package A 132-pin quad flat pack A 132-pin plastic leadless chip carrier 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-37 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-38 13.5 The X86 Hardware 13.5 The X86 Hardware Typical packages of newer X86 processors Typical packages of newer X86 processors Attribute PGA QFP 8088 8086 286 386SX 386DX 486DX Pentium The X86 processor packages and pin count PLCC 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-39 13.5 The X86 Hardware 13.5 The X86 Hardware The X86 processor pin assignment Processor Signal Function Input or Output 8086 (Max Mode) 611 37100 微處理機原理與應用 Lecture 13-41 286 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-40 386 The X86 processor pin assignment 486 國立台灣大學 生物機電系 林達德 Processor Signal Function Input or Output 8086 (Max Mode) 611 37100 微處理機原理與應用 Lecture 13-42 286 386 486 國立台灣大學 生物機電系 林達德 7 13.5 The X86 Hardware 13.5 The X86 Hardware The 80486SX processor pin layout The 80486SX processor pin numbering 611 37100 微處理機原理與應用 Lecture 13-43 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-44 國立台灣大學 生物機電系 林達德 13.5 The X86 Hardware 13.5 The X86 Hardware The 80486SX processor block diagram Block diagram of a maximum mode 8086 system 611 37100 微處理機原理與應用 Lecture 13-45 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-46 13.5 The X86 Hardware 13.5 The X86 Hardware Implementing the 486DX-based PC with VLSI parts 80286 processor summary 國立台灣大學 生物機電系 林達德 2nd generation processor Introduced in 1981 CPU behind IBM AT Throughput of original IBM AT (6MHz) was about 500% of IBM PC (4.77MHz) Level of integration: 134k transistors (29k in 8086) 16-bit processor, available in higher clock frequencies: 25MHz Fully backwards compatible to 8086 Improved instruction set and execution Real mode and protected mode 16MB addressable physical memory On-chip MMU (1GB virtual memory) Non-multiplexed address-bus and data-bus 611 37100 微處理機原理與應用 Lecture 13-47 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-48 國立台灣大學 生物機電系 林達德 8 13.5 The X86 Hardware 13.5 The X86 Hardware 80386 processor summary 80486 processor summary 3rd generation processor Introduced in 10/1985 Full 32-bit processor 275k transistors. CMOS. 132-pin PGA package Clock speeds: 16-33MHz Protected Mode for Multitasking support Real mode (native 8086 mode) • Processor powers up in real mode System management mode • Power management or system security • Processor switches to separate address space, while saving the entire context of the currently running program or task 611 37100 微處理機原理與應用 Lecture 13-49 國立台灣大學 生物機電系 林達德 Introduced in 1989 High integration • On-chip 8K Code and Data cache • Floating Point Unit • Paged, Virtual Memory Management Multiprocessor support • Multiprocessor Instructions • Cache Consistency Protocols Longer prefetch queue (32-bytes as opposed to 16 on the 80386) Higher frequency operation: up to 120MHz >1.2M transistors, 0.8μm CMOS. 168-pin PGA. 611 37100 微處理機原理與應用 Lecture 13-50 國立台灣大學 生物機電系 林達德 13.5 The X86 Hardware 13.6 PC Motherboard Architecture Pentium processor summary Top level PC system architecture 32-bit Microprocessor • 32-bit addressing • 64-bit data bus Superscalar architecture • Two pipelined integer units • Capable of under one clock per instruction • Pipelined floating point unit Separate code and data caches • 8K code, 8K write back data • 2-way 32-byte line size • MESI cache consistency protocol Advance design features • Branch prediction 237-pin PGA 611 37100 微處理機原理與應用 Lecture 13-51 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-52 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture Top level PC system architecture The integration of chipset has reduced a chipset to just 2 main components--the North Bridge (NB) and the South Bridge (SB). In the case of the North Bridge, the chip connects the front side bus [FSB] of the CPU to the DRAM bus, the AGP graphics bus, and the South Bridge. The South Bridge is intended as the place to integrate all the (slower) peripherals like IDE, ISA, USB, etc. The North Bridge is also called the Memory Controller Hub, and the South Bridge has become the I/O Controller Hub. 國立台灣大學 The North Bridge Four interface buses 611 37100 微處理機原理與應用 Lecture 13-53 生物機電系 林達德 • • • • CPU interface The South Bridge interface The DRAM system memory interface The Accelerated Graphics Port interface The function of the chip is to serve as a traffic cop for data moving between the four buses. With enough buffering and some complex arbitration circuitry, a good North Bridge can provide enough concurrency to insure that the DRAM is used efficiently. 611 37100 微處理機原理與應用 Lecture 13-54 國立台灣大學 生物機電系 林達德 9 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture The North Bridge North Bridge is interfaced to the South Bridge with PCI interface. New interfaces include INTEL’s SB interface which is an 8-bit port, running at 66 MHz and transferring 4 bytes per clock, and AMD’s HyperTransport Technology that provides 2 channels for full-duplex operation. VIA has defined their own South Bridge interface that they call "V-Link". Very similar to Intel's approach, this interface provides 266 MBs/sec of bandwidth. The North Bridge Right now, the Pentium 4 chipsets only support RDRAM, though Intel is working on a SDRAM version (code-named "Brookdale"). For now, most chipsets support PC133 SDRAM's and provide 1.064 GB/sec of memory bandwidth from the 64-bit, 133MHz memory interface. Support for DDR DRAM doubles this to 2.1 GB/sec. INTEL developed the AGP interface as a way to help control the system partitioning for graphics. AGP would allow a graphics controller to use system memory for storing graphics texture information. 611 37100 微處理機原理與應用 Lecture 13-55 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-56 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture The North Bridge Originally designed as a 66 MHz interconnect, architecturally similar to a dedicated PCI bus, AGP performance soon scaled to allow 2 samples/clock (AGP 2X) and then 4 samples/clock (AGP 4X). With a 32-bit (4 byte) data path running at 66MHz and capable of 4 transfers per clock, the 4X interface yields 1.056 GBs/sec). Some low-cost motherboard implementations remove the graphics memory entirely and run with a "Unified Memory Architecture (UMA)". The South Bridge While the North Bridge handles high-speed memory arbitration, the South Bridge connects with all the disparate peripherals. Many new motherboards have dropped the ISA bus entirely, but a lot of South Bridge chips still provide the bus as an option for the motherboard designer. The PCI devices are integrated into the South Bridge of many chipsets, including the IDE controller, USB controller, SMBus controller, etc. Most chipsets create an internal PCI-to-PCI bridge, so that these devices don't take up resources from the main PCI bus. 611 37100 微處理機原理與應用 Lecture 13-57 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-58 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture The South Bridge INTEL invented the Low Pin Count Interface (LPC) for the South Bridge that is a simple 4-bit interface and is mainly used for connecting to the Super I/O chip. The Super I/O is where the really old legacy devices live, including the serial ports, parallel port, game port, PS/2 mouse/keyboard, infrared interface, and floppy disk controller. The South Bridge The BIOS is low-level software that controls devices on the motherboard. The processor executes the BIOS code when the PC is first booted, allowing memory testing and configuration of peripherals. INTEL calls their BIOS chip the Firmware Hub (FWH), but it is basically the BIOS running in FLASH (reprogrammable) memory. On an INTEL chipset, the FWH shares pins with the LPC interface. 611 37100 微處理機原理與應用 Lecture 13-59 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-60 國立台灣大學 生物機電系 林達德 10 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture The South Bridge The South Bridge chip usually have one or two USB controllers, each able to manage 2 motherboard connectors. USB is designed to daisy-chain through external hubs to minimize the number of wires that must be connected to the PC. The term Integrated Drive Electronics (IDE) means that most of the control for disk drive has been integrated onto the drive's circuitry, instead of being part of the motherboard or add-in card. The South Bridge The Audio Codec (AC) Link chipset is designed to allow a digital connection to simple off-chip mixed signal (analog/digital) electronics for audio and telephony (modem/networking). The current version is AC'97 2.2, and it provides a 5-signal interface to an external codec (compression/decompression). In the case of audio, the AC Link would connect to a chip that includes a codec and digital-to-analog (D/A) converters for driving audio speakers and analogto-digital (A/D) converters for sampling a microphone or other audio analog inputs. 611 37100 微處理機原理與應用 Lecture 13-61 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-62 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture The South Bridge Integrated internet controller Other motherboard features VRM (Voltage Regulator Module) • The VRM is a programmable voltage regulator, taking a set of 5 VID (voltage identification) signals that are coded to generate a precise voltage. Clocks Connectors Jumpers • Most new motherboards now offer a "jumper-less" mode where all functions are controlled through the BIOS. Riser cards • Low-cost cards that provide external connectors to audio devices, modems or networking. 611 37100 微處理機原理與應用 Lecture 13-63 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-64 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture 13.6 PC Motherboard Architecture Motherboard case study: Motherboard case study: Intel D815EEA Intel D815EEA 611 37100 微處理機原理與應用 Lecture 13-65 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-66 國立台灣大學 生物機電系 林達德 11 13.6 PC Motherboard Architecture Motherboard case study: 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture Motherboard case study: 611 37100 微處理機原理與應用 Lecture 13-68 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture Support for AMD Socket A Processor, 266 MHz FSB and a Big Heatsink Special ASUS Chip for Hardware Monitoring AMD 760 North Bridge with a VIA VT82C686B South Bridge BIOS Allows 1 MHz Frequency Increments Audio Modem Riser (AMR) Allows Low-Cost Audio or Modem 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture Motherboard case study: (2007) 611 37100 微處理機原理與應用 Lecture 13-70 國立台灣大學 生物機電系 林達德 13.6 PC Motherboard Architecture Motherboard case study: ASUS M2N32-SLI Deluxe ASUS M2N32-SLI Deluxe 611 37100 微處理機原理與應用 Lecture 13-71 Processor Socket 82815E Graphics and Memory Controller Hub (GMCH) 82801BA I/O Controller Hub (ICH2) 82802AB Firmware Hub (FWH) SMSC LPC47M102 I/O Controller PCI and CNR Slots Memory Sockets AGP Connector Optional Audio Chips Digital Video Out (DVO) Connector IDE and Floppy Connectors Onboard Speaker and Battery Front Panel Connectors Rear Panel Connectors Jumpers Power Supply Motherboard case study: ASUS A7M266 ASUS A7M266 611 37100 微處理機原理與應用 Lecture 13-69 Motherboard case study: Intel D815EEA Intel D815EEA 611 37100 微處理機原理與應用 Lecture 13-67 13.6 PC Motherboard Architecture Based on the NVIDIA nFOrce 590 MCP Northbridge chipset. With support for 32 and 64-bit computing. Supports dual PCI Express x16 slots running at full speed to liberate graphics cards from the narrow bandwidth platform of x8 speed only 4 DIMM sockets using Dual Channel 240-pin DDR2 with a total capacity of up to 4GB Built in IDE facilities that support Ultra DMA 33/66/100/133 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 13-72 國立台灣大學 生物機電系 林達德 12 13.6 PC Motherboard Architecture Features of modern motherboards System on a chip (SOC) A sealed-box PC with “Device Bay” to allow peripheral connections. Quad-Rate DRAM USB 2.0 PCI-X for 1 GB/sec of bandwidth Multiple processors Reference: http://www.extremetech.com/ PC Motherboard Technology by J. Scott Gardner 611 37100 微處理機原理與應用 Lecture 13-73 國立台灣大學 生物機電系 林達德 13