CSCI-375 Operating Systems

advertisement

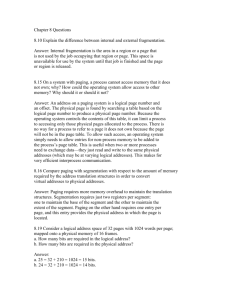

CSCI-375 Operating Systems Lecture 22 Note: Many slides and/or pictures in the following are adapted from: slides ©2005 Silberschatz, Galvin, and Gagne Some slides and/or pictures in the following are adapted from: slides ©2007 UCB by Kubiatowicz Paging • Problem: Run multiple applications in such a way that they are protected from one another • Goals: – Isolate processes and kernel from one another – Allow flexible translation that: • Doesn’t lead to fragmentation • Allows easy sharing between processes • Allows only part of process to be resident in physical memory Paging • Logical address space of a process can be noncontiguous; process is allocated physical memory wherever the latter is available • Divide physical memory into fixed-sized blocks called frames (size is power of 2, between 512 and 8192 bytes) • Divide logical memory into blocks of same size called pages • Keep track of all free frames • To run a program of size n pages, need to find n free frames and load program Paging Operating Systems, 4th Edition, by William Stallings Paging • Set up a page table to translate logical to physical addresses • Internal fragmentation? Address Translation Scheme • Address generated by CPU is divided into: – Page number (p) – used as an index into a page table which contains base address of each page in physical memory – Page offset (d) – combined with base address to define the physical memory address that is sent to the memory unit Address Translation Architecture Paging Example Paging Example Free Frames Before allocation After allocation Implementation of Page Table • Where to keep the page table? – Page table is kept in main memory – Page-table base register (PTBR) points to the page table – Page-table length register (PTLR) indicates size of the page table – In this scheme, every data/instruction access requires two memory accesses. One for the page table and one for the data/instruction – The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation look-aside buffers (TLBs) Associative Memory • Associative memory – parallel search Page # Frame # • Address translation (Page #, Frame #) – If Page # is in associative register, get Frame # out – Otherwise get Frame # from page table in memory Paging Hardware With TLB Effective Access Time • Associative Lookup = ε << 1 time units – Assume memory access time is 1 time unit • Hit ratio – percentage of times that a page number is found in the associative registers; ratio related to number of associative registers – Hit ratio = α • Effective Access Time (EAT) EAT = (1 + ε) α + (2 + ε)(1 - α) =2+ε-α Effective Access Time • Example – α = 0.8 – ε = 20 ns – Memory access time = 100 ns – EAT = (120)0.8 + (220)0.2 = 140 ns Memory Protection • Memory protection implemented by associating protection bit with each frame • Valid-invalid bit attached to each entry in the page table: – “valid” indicates that the associated page is in the process’ logical address space, and is thus a legal page – “invalid” indicates that the page is not in the process’ logical address space Memory Protection A system with a 14-bit address space (0 to 16383) Most processes use only a fraction of address space available to them. Should we create page table with entries for every page in address range? No, use PTLR Memory Protection • Can process modify its own page table? – If it could, could get access to all of physical memory – Has to be restricted • Dual mode operation • Mode set with bits in special control register only accessible in kernel-mode Shared Pages • Shared code – One copy of read-only (reentrant) code shared among processes (i.e., text editors, compilers, window systems) • Private code and data – Each process keeps a separate copy of the code and data Page Table Structure • Hierarchical Paging • Hashed Page Tables • Inverted Page Tables Hierarchical Page Tables • Most modern computer systems support a large logical address space (232 to 264) • Consider a system with a 32-bit logical address space. If the page size is 4KB (212), then a page table may consist of up to 1 million entries (232/212). Assuming each entry consists of 4 bytes, each process may need up to 4MB of physical-address space for the page table alone. Clearly, we would not want to allocate the page table contiguously. What should we do? – Page the page table! Duh… • Break up the logical address space into multiple page tables • A simple technique is a two-level page table Two-Level Page-Table Scheme Two-Level Page-Table Scheme Hashed Page Tables • Hash functions anyone? Hashing (DS course) • Suppose we are writing a compiler and need to maintain a symbol table, in which the keys of elements are arbitrary character strings that correspond to identifiers in the language • We need to search for an element in the symbol table. How long will it take? – It depends on the data structure – (unsorted) linked list? – (balanced) binary search tree (e.g., AVL tree)? • Can we do even better than O(log n) (e.g., O(1))? – Yes, we can use “hash” functions Hashing (DS course) • The general idea behind hashing is to directly map each data item into a position in a table (e.g., an array) using some function h – Complex data items must have a “key” in order to perform the hashing. Then, position = h(key) Hashing (DS course) • What happens if more than one key hash to the same position? • The problem is called a “collision” – With the “separate chaining” collision resolution approach, all data items that hash to the same position are kept in a linked list. So, to find the item that we are looking for, we have to search the linked list • Hash functions should try to achieve uniform coverage of the hash table, while minimizing collisions Hashed Page Tables • Common in address spaces > 32 bits • The virtual page number is hashed into a page table. This page table contains a chain of elements hashing to the same location • Virtual page numbers are compared in this chain searching for a match. If a match is found, the corresponding physical frame is extracted Hashed Page Table Inverted Page Table • One entry for each real page (or frame) of memory • Entry consists of the virtual address of the page stored in that real memory location, with information about the process that owns that page • Decreases memory needed to store each page table, but increases time needed to search the table when a page reference occurs Inverted Page Table