Vishwani D. Agrawal

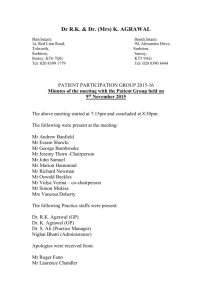

advertisement