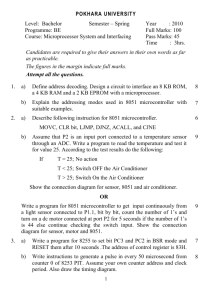

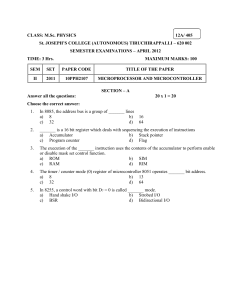

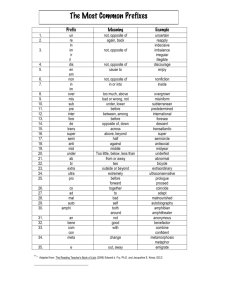

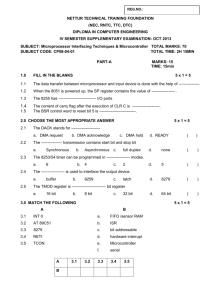

Application of Microcontrollers Manual Part II

advertisement