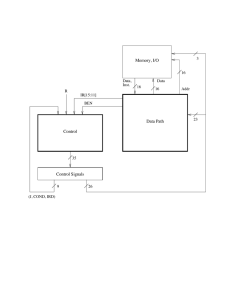

176 Lab 8 that changing the switches will have no effect, unless you

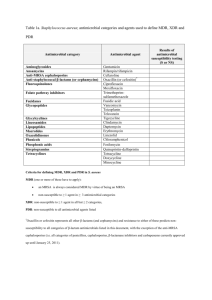

advertisement

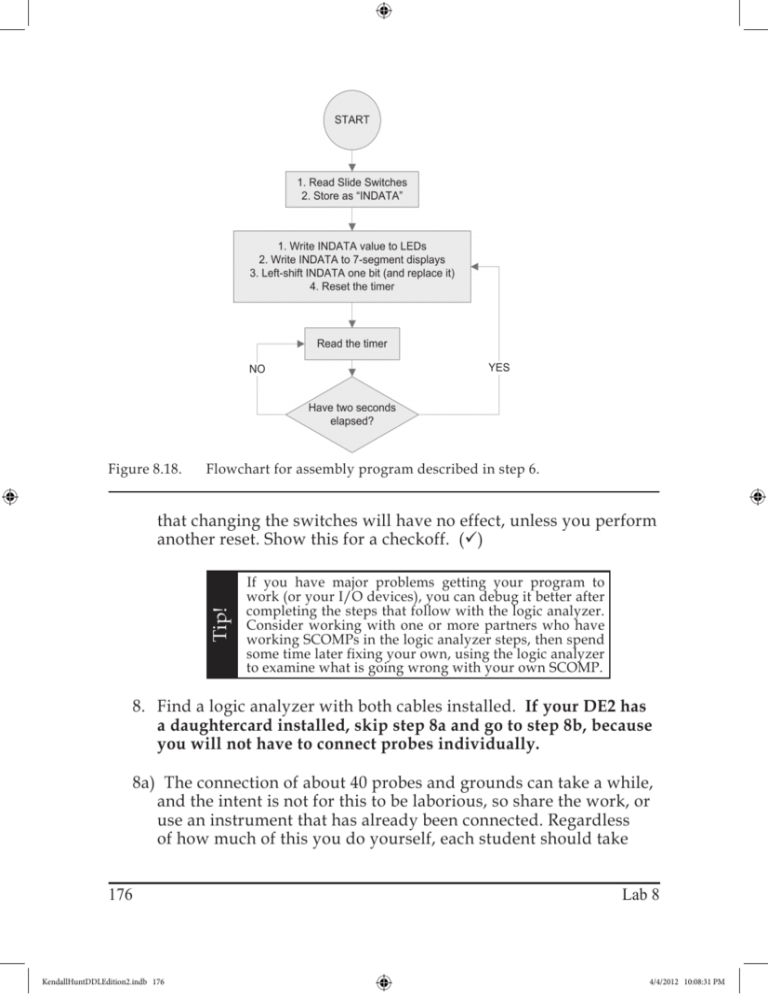

Figure 8.18. Flowchart for assembly program described in step 6. Tip! that changing the switches will have no effect, unless you perform another reset. Show this for a checkoff. () If you have major problems getting your program to work (or your I/O devices), you can debug it better after completing the steps that follow with the logic analyzer. Consider working with one or more partners who have working SCOMPs in the logic analyzer steps, then spend some time later fixing your own, using the logic analyzer to examine what is going wrong with your own SCOMP. 8. Find a logic analyzer with both cables installed. If your DE2 has a daughtercard installed, skip step 8a and go to step 8b, because you will not have to connect probes individually. 8a) The connection of about 40 probes and grounds can take a while, and the intent is not for this to be laborious, so share the work, or use an instrument that has already been connected. Regardless of how much of this you do yourself, each student should take 176 KendallHuntDDLEdition2.indb 176 Lab 8 4/4/2012 10:08:31 PM JP1 header Pin 1 → Logic Probes Color codes Left Right MDR[0] MDR[1] A2-0 A2-1 black brown MDR[2] MDR[3] A2-2 A2-3 red orange MDR[4] MDR[5] A2-4 A2-5 yellow green MDR[6] MDR[7] A2-6 A2-7 blue violet MDR[8] MDR[9] A3-0 A3-1 black brown not used ground MDR[10] MDR[11] A3-2 A3-3 red orange MDR[12] MDR[13] A3-4 A3-5 yellow green MDR[14] MDR[15] A3-6 A3-7 blue violet MAR[0] MAR[1] C2-0 C2-1 black brown MAR[2] MAR[3] C2-2 C2-3 red orange MAR[4] MAR[5] C2-4 C2-5 yellow green MAR[6] MAR[7] C2-6 C2-7 blue violet MAR[8] MAR[9] C3-0 C3-1 black brown A3-gnd sol. blk not used ground MW FETCH C3-2 C3-gnd C3-3 red sol. blk orange IO_WRITE IO_CYCLE C3-4 C3-5 yellow green not used not used not used not used CLK_SCOMP not used CLK0 Figure 8.19. Mapping of logic probe connections to JP1 header pins, where both tables above directly overlay the physical footprint of JP1. For example, logic probe A2-0 (black band) should be connected to JP1, pin 1, which the design file uses for MDR[0]. a few minutes to verify the connections. Do not assume that the previous users got every connection correct. There are a total of 5 ground connections (A2, A3, C2, C3, and CK0). These can be connected to pins 12 and 30 on both headers, with the fifth ground connected to one of the DE2 board mounting screws (since those screws are grounded). If no wire is present on the DE2 screws, use a wire connected to the CADET ground, but a shorter ground would be better. Now, skip step 8b and continue with 8c. Lab 8 KendallHuntDDLEdition2.indb 177 177 4/4/2012 10:08:31 PM 8b) There are four 16-pin headers on the left side of the DE2 daughterboard, labelled as LA_A2, LA_A3, etc. Simply connect the four logic analyzer signal pods to those headers (A2 to LA_A2, etc.), Also connect the one Clock signal (CK0) to the header labelled LA_CLK. In all cases, note that ground is to the left! The result will resemble Figure 8.20, and will implement the correct connections of Figure 8.19. 8c) Get a checkoff here, with all probes connected. () 9. On the computer at the same workstation, open your working project file. In order to have the signals present at the proper locations of Figure 8.19, it is necessary to have all of the pin assignments that were included in the project that you downloaded in step 3. This is easy to check — you should see a location assignment for every pin in the Pin Planner. If you lost (or changed) any pin assignments, you can download the zip file again, unzip it to a temporary folder, and copy the TOP_SCOMP.QSF file over your existing one, but always do that sort of thing while your project is closed (not open in Quartus). Figure 8.20. Completed logic analyzer connections, viewed from above, with a total of five probe heads being used (including the two-position clock probe, CK0). 178 KendallHuntDDLEdition2.indb 178 Lab 8 4/4/2012 10:08:32 PM