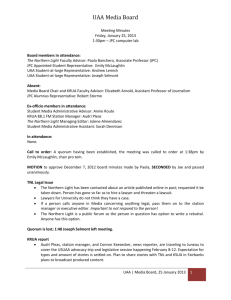

Jaeger CH 7

advertisement

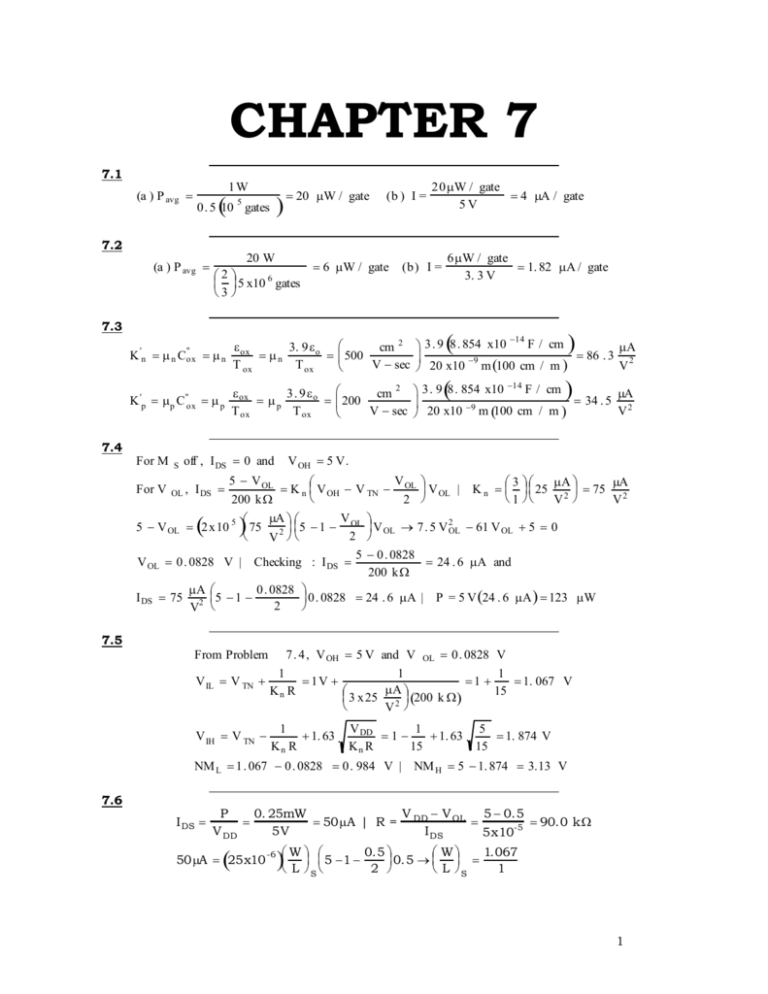

CHAPTER 7 7.1 (a ) P avg 1W 5 0. 5 10 gates 20 W / gate (b ) I = 20W / gate 4 A / gate 5V 7.2 (a ) P avg 20 W 2 6 5 x10 gates 3 6 W / gate (b) I = 7.3 6W / gate 1. 82 A / gate 3. 3 V 14 K n n Cox n F / cm ox 3. 9 o cm 2 3. 9 8. 854 x10 A n 500 86 . 3 2 9 T ox T ox V sec 20 x10 m 100 cm / m V K 'p p C"ox p 2 3. 9 8. 854 x10 14 F / cm ox 3. 9 o cm A p 200 34 . 5 2 9 T ox T ox V sec 20 x10 m 100 cm / m V ' " 7.4 off , I DS 0 and For M S For V OL , I DS V OH 5 V. 5 V OL 5 V OL 2x10 V K n V OH V TN OL V OL | 200 k 2 5 75 5 0. 0828 24 . 6 A and 200 k A 0. 0828 0. 0828 24 . 6 A | 2 5 1 2 V 7.5 3 A A K n 25 2 75 2 1 V V A V OL 2 V OL 7. 5 V OL 61 V OL 5 0 2 5 1 2 V V OL 0. 0828 V | Checking : I DS I DS 75 P = 5 V 24 . 6 A 123 W 7. 4, V OH 5 V and V OL 0. 0828 V 1 1 1 1V 1 1. 067 V A Kn R 15 3 x25 2 200 k V From Problem V IL V TN V IH V TN 1 1. 63 Kn R V DD 1 5 1 1. 63 1. 874 V Kn R 15 15 NM L 1. 067 0. 0828 0. 984 V | NM H 5 1. 874 3.13 V 7.6 I DS P 0. 25mW V V OL 5 0.5 50A | R = DD 90.0 k V DD 5V I DS 5x10-5 50A 25x10 -6 W 0.5 WL 5 1 0.5 2 L S S 1.067 1 1 V OH 5V | V OL = 0.5V 1 1 1 V IL V TN 1V 1 1.417 V A Kn R 2. 401 1.067 x25 2 90k V V IH V TN 1 V DD 1 5 1.63 1 1.63 2.936 V Kn R K nR 2. 401 2.401 NM L 1.417 0.5 0.917 V | NM H 5 2.936 2. 064 V 7.7 P 0. 25mW V V OL 3.3 0.25 75.76A | R = DD 40.3 k a I DS -6 V DD 75.76x10 -6 3. 3V -6 25 x10 I DS W 75.76x10 0.25 4.90 W 3.3 0.7 0.25 2 L 1 S S L b V OH 3. 3V | V OL = 0. 25V V IL V TN 1 0.7V Kn R 1 1 0.7 0.903 V A 4. 937 4.90 25 2 40.3k V V IH V TN 1 V DD 1 3. 3 1.63 0.7 1.63 1.83V Kn R K nR 4.937 4. 937 NM L 0.903 0.25 0.653 V | NM H 3.3 1.83 1.47 V 7.8 R= V DD V OL 3. 3 0.2 93.94 k IDS 33x10-6 33A 60x10 7.9 -6 W 0. 2 WL 3.3 0.75 0.2 2 L S S 1.122 1 1 1 1000 W K 'n V GS V TN 25x10 6 10 5 1 L 1 1 1 (b) R on 2500 W K 'p V SG V TP 10 x10 6 10 5 1 L 1 (c) A resistive connection exists between the source and drain . (a ) R on (d) W 1 1 20 ' 6 L 1 K n V GS V TN R on 25x10 3 11000 W 1 1 20 ' 6 L K p V SG V TP R on 10x10 3 12500 1 7.10 V OH V DD V TO V SB 2 F 2F V OH V OH 4. 882 0.5625 V OH 0.7 V 2OH 10.3V OH 23. 4 0 V OH 6.92V, 3.38 V V OH 3.38 V 2 5 0.75 0.75 V OH 0.7 0.7 3.38 0.75 Checking: V TH 0.75 0.75 7.11 V OH V DD V TO V OH 3.158 2 V SB 2 F 2F V 0.75 1.63 V | 5 1.63 3.37V OH 3 0.5 0.85 V OH 0.6 0.6 0.7225 VOH 0. 6 V 2OH 7.038 V OH 9.539 0 V OH 1. 832V, 5.206 V V OH 1.832 V Checking: V TH 0.5 0.85 1.832 0.6 0.6 1.167 V | 3 1.167 1.833 V 7.12 For = 0, V OH V DD V TN 3.3 1 2.3V | For V OL : I DSL I DSS ' V Kn 1 2 3. 3 V OL 12 K 'n 4 2.3 1 OL V OL 9V OL 25V OL 5.29 0 2 2 1 2 25x106 1 3.3 0.2264 12 26. 87A 2 2 P 3.3V 26.87A 88.68 W V OL 0.2264 V | I DD 0.2264 4 Checking: I DD 25x10 6 2. 3 1 0. 2264 26.87A 1 2 7.13 V IL V TNS 1V | At V IH Eq . 7.25 V O 3.3 1 0. 46V 4 1 3 0.5 0. 46 0.5 1 2 3.3 0.46 1 1.69V 2 2 4 0.46 2. 3 1. 69 0. 610 V | NM L 1 0.226 0.774 V V IH 1 NM H 7.14 3 (a ) V OH V DD V TO V OH 2.987 2 V SB 2F 2 F OH V 3.3 0.7 0.5 OH 0.6 0.6 0.25 V OH 0. 6 V 2OH 6.225 V OH 8. 772 0 V OH 2.156 V V OL = 0. 25V | I DS 0.25mW 0.25 W 75.76A | 75.76 = 25 2.156 0.7 0.25 L S 3. 3V 2 W 9.107 | V TNL 0.7 0.5 L S 1 75.76 = V 0. 25 0. 6 0. 6 0.7737 V 25 W 1.170 2 W 3. 3 0. 25 0. 7737 2 L L L L 1 (b) V IL V TNS 0.70 V | Finding V IH : v O V DD V TNL 1 3 v V TNL 0.7 0.5 O W / L S W / L L 1 3 3.3 V TNL v 0.6 0. 6 | 4.395 v O 3.3 0.7 0.5 9.107 1.170 O 3.3 V TNL 4. 935 0.6 0.6 Using the quadratic equation: v O 0. 4990 V V TNL 0.8369V V IH V TNS v o W / L L 1 2 0.499 1.170 1 V v O V TNL 0.7 3. 3 0. 499 0.837 2 2 W / L S v O DD 2 9.107 0. 499 V IH 1. 943V | NM H 2.156 1. 943 0.213 V | NM L 0.7 0. 25 0. 45 V 7.15 0.5mW 100A | V TNL 1 0.5 0.5 0. 6 0. 6 1.137V 5V 25x106 W 1 2 W 6 100x10 5 0.5 1.137 2 L L L L 1.41 I DD 100x10 6 0.5 6 W 25x10 3.39 1 0.5 L S 2 7.16 (a) VDD = 3.3 V VTN =1 V IDS = 33 mA VOL =0.2 V 3.74 W L S 1 VOH = VDD - VTN = 3.3 V - 1V = 2.3 V I DSS IDSL 33A V W I DSS K 'n V GSS V THS DSS V DSS L S 2 33A 25 I DSL ' K n W 2 V GSL V TNL 2 L L 33A 4 A W 0.2 5.5 W 2. 3 1 0.2 2 2 L S 1 V L S 25 A W 1 2 W V 2 3.3 0.2 1 L L 1.67 2 L L (b) V OH V DD V TO V OH 2.687 2 33A 25 I DSL V SB 2 F 2 F V V OH 0.6 0.6 A W 0. 2 8.27 W 1.898 1 0.2 2 L 2 L 1 V S S ' 33A 3.3 1 0.5 0. 25V OH 0. 6 V 2OH 5.625V OH 7.072 0 V OH 1.898 K n W 2 V GSL V TNL | V TNL 1 0.5 2 L L 25 OH 0. 2 0.6 0.6 1. 06V A W 1 2 W V 2 3.3 0.2 1.06 2 L L L L 1.58 7.17 ' V K W 2 W I DSS IDSL | K 'n V GSS V TNS DSL V DSL n V GSL V TNL L S 2 2 L L V K ' 1 2 ' 2.78 K n 5 1 O V O n 5 V O 1 1 2 2 3.52 V 2 19.6V O 4 O 4 V O V 2O 8V O 1. 483 0 V O 0.190V 2 7.18 The problem is similar to Prob. 17.17 except now VTNL 1 0.5 V O 0.6 0.6 V K ' 1 2 ' 3. 53 and K n 5 1 O V O n 5 V O V TNL 1 2 2 3. 39 Using MATLAB or other solver V O 0.154 V 7.19 V K ' W 2 ' W I DSS IDSL | K n V OH V TNS OL V OL n 5 V OL V TNL L S 2 2 L L ' which is independent of Kn . Ratioed logic maintains VOL and V OH independent of K 'n . So V OH 3. 39V and V OL 0. 25V. However, I DSS I DSL K 'n : I DSS 18 A 3.53 0.25 3. 39 1 0.25 36. 0A | P = 5 36. 0A 0.180 mW 2 2 V 1 7.20 V TNL 1 0.5 0.25 0.6 0.6 1.074 V V GSL V TNL 7.5 0.25 1.074 6.18V | V DSL 5 0. 25 4.75V Linear region 50A 25 A W 4.75 1 W 7.5 0.25 1.074 4.75 L L 9.03 V 2 L L 2 The value is incorrect in the First Printing in Figs. 7.16 and 7.20(c). 7.21 For linear operation at vo V OL : V TNL 1 0.5 0.25 0.6 0.6 1. 074V V GSL V TNL V DSL: V GG 0.25 1.074 5 0.25 V GG 6.07V 5 0.6 Also require: V GG 5 V TNL 5 1 0.5 0. 6 6.80V so V GG 6.80 V 5 7.22 ' V K 1 2 5 V TN 1V | V OH 6 1 5.00 V | I DSS I DSL | K 'n 5 1 OL V OL n 6 V OL 1 1 2 2 2 2 11V OL 90 V OL 25 0 V OL 0.2879 V 0.288 V I DSS 25A 2 1 2 6 0.2879 1 138.8A | P = 5V 138. 8A 0. 694 mW 2 7.23 We require V TNL 0: 3 5 0.6 0.6 0 1.89 7.24 V K ' W W 2 V OH V DD | I DSS IDSL | K 'n V DD V TNS OL V OL n V TNL L S 2 2 L L ' For ratioed logic, both VOH and V OL are independent of Kn . V OH 5 V | V OL = 0.25V 40 However, I DS K 'n | I DS 50A 80A | P = 5V 80A 0.400 mW 25 7.25 0.25mW 75.76A 3.3V (a ) I DD V TNL 3 0.5 V TNL 3. 3 0.6 0.6 2. 40V VOH 3.3 V 0. 25 4.90 W W 75.76A 25A 3.3 0.7 0. 25 L S L S 2 1 25A W W 1 3 0.5 0. 25 0. 6 0. 6 2. 926V | 75. 8A 2.926 2 | 2 L L L L 1. 41 (b) V TNL 3 0.5 V V O V DD V TNL O 0.6 0.6 | V IL 0.7 V TNL K 2R K R V 2TNL K R V IL V TNS 3. 3 V TNL 2 | K R 4. 901.41 6.91 V 2TNL 6.91V IL 0.7 2 By MATLAB: V O 3.142 V | V TNL 2.420 V | V IL 1.027 V | NM L 1.027 0. 25 0.777 V VO V 3 0.5 V TNL 3K R V IH V TNS 2V TNL 3K R 0.7 O 0. 6 0. 6 4.553 V O 0. 6225V V TNL 2.834 V 2 2.834 1.945V | NM H 3. 3 1. 945 1. 36 V 4.553 7.26 With A = 1 = B, the circuit is equivalent to a single 4.12 /1 switching device. V 25A 1 4.12 2 25A 5 1 OL V OL V TNL | V TNL 3 0.5 1 2 2 2.15 Solving iteratively V OL 0.1257V | V TNL 2.961V b 7.27 6 V OL 0. 6 0. 6 25A 1 2 2.961 50.1 A 2 2.15 0.125 4.06 W W 50A = 25A 5 1 0.125 L A L A 2 1 0.125 4. 24 W W 50A = 25A 5 0.125 1. 04 0.125 L B L A 2 1 7.28 We require R on R on R on W W K L A L B Setting L =1, and the total area AT WLA WL B 1 1 1 KW B KW B W 2B WA AT WB WA WB K WB K WB K WB K Finding the minimum: 2 2 d W B W B 2KW B 0 W B 2K & W A 2K. dW B W B K W B K 2 7.29 7 7.30 7.31 For M N off, I SDP 0, V SDP 0, V OH V DD 5V Kp V 5 V TP 2 K n V OH V TN OL V OL 2 2 10 5 1 V 2 5 5 1 25x10 6 5 1 OL V OL 1 2 1 2 V OL 0.163 V 7.32 A B Y 0 (a ) 0 0 1 1 0 1 1 0 1 0 1 (b) Y = AB AB A B (c) Assuming equal voltage drops (0.125V ) across M P and M S : W 4.12 M P must carry one unit of load current with V DS 0.125V L P 1 8. 24 W M S must carry two units of load current with V DS 0.125V L S 1 (d) M S will not change. M P will need to be somewhat larger. (e) Coincidence gate (Exclusive NOR) 7.33 7.34 1 W Y A BC DE F | L L 2.15 1 W Y A BC DE | L L 2.15 W 2. 06 6.18 | 3 L A F 1 1 W 2.06 6.18 | 3 L A E 1 1 7.35 1 1.40 W Y ACE ACDF BF BDE | 3 = | ACDF path contains 4 devices L L 2.15 1 2.06 24.7 1 1 1 1 16.5 W W 3 4 | 2.06 L A,C ,D,F L B ,E 1 1 W 24.7 W 1 3 L B 1 L E 1 8 7.36 W 1 L L 2.15 DCA and ECA paths contain three devices W 2.15 6.18 3 L A,C ,D,E 1 1 1 1 1 W W 2.15 L A L B 1 1 1 1 3.09 W 6.18 W 2.15 L B 1 1 A 1 B 1 7.37 1 1 1 W L L 2 2.15 4. 30 CBA and EDA paths contain three devices W 1 2.15 3.09 3 L A E 2 1 1 9 7.38 1 W L L 3. 39 CBA and EDA paths contain three devices W 3.53 10.6 3 L A E 1 1 7.39 1 W L L 3. 39 DCA path contains three devices W 3.53 10.6 3 L A,C ,D 1 1 1 1 1 5. 30 W 10.6 W 3.53 L B 1 1 A 1 B 1 3.53 W L E 1 7.40 Y A B D C E C E G F = C EAB D G F 1 1 W 2 = L L 2.15 1.08 2.06 12. 4 W | 23 L A E 1 1 W 2.06 4.12 1 1 1 W 6.18 2 | L F 1 1 W 12. 36 2 2. 06 L G 1 L G 1 1 10 7.41 (a) 1 W L L 2.15 DCA path contains three devices W 2. 06 6.18 3 L A,C ,D 1 1 1 1 1 3.09 W 6.18 W 2.06 L B 1 1 A 1 B 1 2.06 W L E 1 (b) Device E remains the same. V OL 0.25 V 0.25 0.08333 V | B: V DS 2 OL 2 0.1667 V 3 3 3 3 W 0.08333 6.06 W 25A 5 1 0.08333 50A L A 2 L A 1 A,C,D: V DS 0.08333 0.6 V TNB V TNC 1 0.5 0.6 1. 026V 0.1667 3.15 W W 25A 5 0. 08333 1.026 0.1667 50A L B L B 2 1 0. 08333 6.24 W W 25A 5 0. 08333 1.026 0.08333 50A L C 2 L C 1 0.1667 0.6 V TND 1 0.5 0.6 1.051V W 0.08333 W 6.42 25A 5 0.1667 1.051 0.08333 50A L D 2 L D 1 7.42 Device A remains the same. 2.06 W L A 1 V OL 0.25 0.125 V 2 2 0.125 4.06 W W 25A 5 1 0.125 50A L C ,D 2 L C, D 1 B, C,D: V DS V TNB 1 0.5 0.125 0. 6 0.6 1.038V 0.125 4.24 W W 25A 5 0.125 1. 038 0.125 50A L B L B 2 1 7.43 11 V 0.25 0.25 0.08333 V | A: V DS 2 OL 2 0.1667 V 3 3 3 0.08333 6.06 W W 25A 5 1 0. 08333 50A L B 2 L B 1 BCD : V DS V OL 3 V TNA 1 0.5 0. 08333 0.6 0.6 1.026 V 0.1667 3.15 W W 25A 5 0.08333 1. 026 0.1667 50A L A 2 L A 1 0.08333 6.24 W W 25A 5 0.08333 1. 026 0.08333 50A L D 2 L D 1 V TNC 1 0.5 0.1667 0. 6 0. 6 1.051V 0.08333 6.42 W W 25A 5 0.1667 1.051 0. 08333 50A L C 2 L C 1 7.44 W 0.125 W 4. 06 25A 5 1 0.125 50A L B 2 L B 1 0.125 0.6 V TNA V TND 1 0.5 0.6 1. 038V 0.125 W W 25A 5 0.125 1.038 0.125 50A 4.24 L A L A 2 0.0625 W W 25A 5 0.125 1.038 0. 0625 50A 8. 41 L D L D 2 V TNC 1 0.5 0.1875 0. 6 0. 6 1.056 V W 0.0625 W 8.59 25A 5 0.1875 1.056 0.0625 50A L C L B 2 1 7.45 V OL 0.25 0.08333 V 3 3 0.08333 6. 06 W W 25A 5 1 0.08333 50A L B,E L B, E 2 1 Worst case situation A- E: V DS 0. 08333 0.6 V TND 1 0.5 0.6 1. 026V 0.08333 6. 24 W W 25A 5 0.08333 1. 026 0.08333 50A L D 2 L A 1 0.1667 0.6 V TNA V TNC 1 0.5 0.6 1. 051V 0. 08333 6. 42 W W 25A 5 0.1667 1.051 0.08333 50A L A, C 2 L A, C 1 12 7.46 Original design 0.25 mW - 1 mW requires 4 times larger current. (a ) R = 95k 23.8k 4 2. 06 8.24 W = 4 L S 1 1 1 1.18 W (b) 4 = L L 3.39 1 3.53 14.1 W 4 = L S 1 1 1 1 W (c) 4 = L L 9.03 2. 26 2.06 8.24 W 4 = L S 1 1 W 1 1.86 (d) 4 = L L 2.15 1 W 2.06 8.24 4 = L S 1 1 7.47 W 1 1. 86 4 = L L 2.15 1 2. 06 24.7 W | 4 3 L A E 1 1 1 1 1 12.4 W 2.06 8.24 W 4 | 2. 06 L F 1 L G 1 W 24.72 4 1 1 L G 1 7.48 1 1 1 W = L L 4 2.15 8. 60 7.49 (a ) I DS I 'DS 1 2.06 1.55 W | 3 L A F 4 1 1 W 1 2 1 2 " W n Cox V GS V TN n ox V GS V TN 2 L 2 T ox L 1 n ox T ox 2 2 W 2 I 'DS 2 2 L V GS V TN 2I DS | I DS 2 (b) P 'D = V 2I 2VI 2PD - Power dissipation has increased by a factor of two. 7.50 dv | Assume the transition occurs in DT seconds generating dt 5V a current pulse with constant amplitidue I 10x10 12 F . T 11 5x10 T Then Iavg 1.00mA and P 645V I avg 64 5 1.00mA 0.320 W T 50ns For each line: i = C 2 3.3 (b) P V 2 so P = 0.320 W 0.139 W 5 7.51 13 PHL PHL 7.52 C KS and PLH C | For either case, KL C C "ox WL L2 = KS " W n n Cox L P PDP 100fJ 10 13 J 1 ns PD 100W 10 4 W 7.53 5 0.25 2.63V 2 0.25 0. 475 0.725V V OH 5V | V OL 0.25V | V 50% V 90% 5 0.475 4.53V | V 10% (a ) v I : t r 22.5 1.5 21 ns | v O : t r 81 58 23 ns v I : tf 62 55 7 ns (b) PHL 2. 5 ns | PLH 7.54 (a ) T 301 PHL PLH 602 | v O : t r 12.5 6 6.5 ns 2.5 7 7 ns (c) P 4.8 ns 2 PHL PLH 602 P 6020.1ns 60.2 ns 2 (b) An even number of inverters has a potential steady state and may not oscillate . 7.55 t r 2.2RC 2.295k 0.5pF 105 ns tf 1 2.06 25x10 6 5 1 5 1 1 0.14.75 1 2 6.23 ns 5 1 5 0.94.75 0.5pF ln2 PLH 0.69RC 0.69 95k 0.5pF 32.8 ns PHL P 7.56 14 0.30.5pF 0. 3C 2. 91 ns KS A 2.06 25 2 V 32.8 2. 91 17.9 ns 2 For M S off, I DS 0 and V OH 3. 3V. For V OL , I DS 3. 3 V OL 2. 06 A V 25 3.3 1 OL V OL 95k 1 V 2 2 2.446 V 2OL 12.25V OL 3.3 0 V OL 0.2856 V t r 2.2RC 2.295k0.5pF 105 ns tf 1 0.13. 01 1 3.3 1 0.5pF ln 2 1 2 10. 7ns 3.3 1 2.06 25x10 6 3.3 1 3. 3 0. 93. 01 PLH 0.69RC 0.69 95k 0.5pF 32.8 ns PHL P 1 2. 06 25x10 6 3. 3 1 3.3 1 1 1 4.00ns 3.3 0. 286 2 0.5pF ln 4 32.8 4.00 18.4 ns 2 15 7.57 V TN 1 V OH 5 1 4V 6 4 V 1 25x10 25x10 6 4 1 OL V OL 1 2 2 2 5 V 1 2 OL 2 9V OL 56V OL 16 0 V OL 0.300V | V 4 0.3 3. 7V 160 0.5pF 192 ns 6 9 25x10 0. 55 1 0.3 tr 0.5pF tf 5 1 1 0. 93.7 1 0.13.7 2 ln 4.44 ns 5 1 1 4 5 1 1 5 1 0.9 3.7 25x10 6 PLH 2R ONL C PHL P 7.58 2 25x10 0.55 1 0. 3 6 0.5pF 21. 6 ns 0.5pF 4 25x10 6 5 1 1 2 ln 4 1 2.08 ns 5 1 0.3 3 5 1 1 21.6 2.08 11.8 ns 2 V TN 1 V OH 3. 3 1 2.3V 4 25x10 6 1 6 V OL 1 25x10 3.3 1 V OL 2 2 2 3.3 V 1 2 OL 2 9V OL 41. 40V OL 5.29 0 V OL 0.132V | V = 2.3 0.132 = 2.17V tr tf 160 0.3pF 197 ns 9 25x10 6 0. 53.3 1 0.132 0.3pF 3.3 1 1 0.92.17 1 0.12.17 2 ln 7. 94 ns 3.3 1 1 4 3.3 1 1 3.3 1 0.92.17 25x10 6 PLH 2R ONL C PHL P 7.59 16 2 25x10 0.53.3 1 0.132 6 0.3pF 22.1 ns 0.3pF 4 25x10 6 3.3 1 1 2 ln 4 1 1. 84 ns 3. 3 1 1 3.3 1 0.132 3 22.1 1. 84 12.0 ns 2 *Problem 7.59 VDD 3 0 DC 5 VI 1 0 DC 0 PWL (0 0.25 1N 3.39 25N 3.39 26N 0.25 300N 0.25) CL 2 0 0.25PF ML 3 3 2 0 NMOSFET W=1U L=3.39U MS 2 1 0 0 NMOSFET W=3.53U L=1U .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 .OP .TRAN 0.25N 300N .DC VI 0 5 .01 .PROBE V(1) V(2) .PRINT TRAN V(1) V(2) .END Results: tf = 3.7 ns, tr = 152 ns, tPHL = 1.9 ns, tPLH = 16 ns, tP = 9 ns tr tf 160 9 0. 25pF 1 25x10 6 5 1. 61 0.25 3.39 0. 25pF 5 1.61 1 0.9 3.14 1 0.13.14 2 ln 3.32 ns 5 1. 61 1 3.53 5 1.61 1 5 1. 61 0.93.14 25x10 6 PLH 2R ONL C 2 0. 25pF 25x10 PHL P 7.60 192 ns 6 1 5 1.61 0.25 3.39 21.6 ns 0.25pF 5 1.61 1 2 4 1 1.37 ns ln 3.535 1.61 1 5 1.61 0.25 3 25x10 6 21.6 1.37 ns 11.5 ns 2 *Problem 7.60 - Saturated load cascade inverter delay VDD 1 0 DC 5 VI 2 0 PWL (0 3.39 0.1N .25 100N .25 100.1N 3.39 200N 3.39) ML1 1 1 3 0 NMOSFET W=2U L=6.78U AS=8P AD=8P MS1 3 2 0 0 NMOSFET W=7.06U L=2U AS=28P AD=28P ML2 1 1 4 0 NMOSFET W=2U L=6.78U AS=8P AD=8P MS2 4 3 0 0 NMOSFET W=7.06U L=2U AS=28P AD=28P ML3 1 1 5 0 NMOSFET W=2U L=6.78U AS=8P AD=8P MS3 5 4 0 0 NMOSFET W=7.06U L=2U AS=28P AD=28P ML4 1 1 6 0 NMOSFET W=2U L=6.78U AS=8P AD=8P MS4 6 5 0 0 NMOSFET W=7.06U L=2U AS=28P AD=28P ML5 1 1 7 0 NMOSFET W=2U L=6.78U AS=8P AD=8P MS5 7 6 0 0 NMOSFET W=7.06U L=2U AS=28P AD=28P .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .OP .TRAN 0.2N 200N .PROBE V(2) V(3) V(5) V(6) .END The results of this problem are highly dependent upon the models used. The model must include capacitances. Thus, at a minimum, the TOX parameter must be specified. For the models above: First inverter: t r 25ns t f 0.5ns PLH 2.5ns PHL 0.4ns C= 6 9 tr 9 9 25x10 25x10 5 1 0.25 39 fF 160 R onL 160 3.39 Fourth inverter: t r 25ns t f 4ns PLH 2.5ns PHL 1.3ns 17 Rise time and PLH are controlled by the slow transition of the load device and are essentially the same. Fall time and PHL are faster for the first inverter because of the much faster input signal transistion. 7.61 *Problem 7.61 VDD 3 0 DC 5 VGG 4 0 DC 7.5 VI 1 0 DC 0 PWL (0 0.25 1N 5 25N 5 26N 0.25 300N 0.25) CL 2 0 0.15PF ML 3 4 2 0 NMOSFET W=1U L=9.03U MS 2 1 0 0 NMOSFET W=2.06U L=1U .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 .OP .DC VI 0 5 .01 .TRAN 0.25N 300N .PROBE V(1) V(2) .PRINT TRAN V(1) V(2) .END Results: tf = 2.1 ns, tr = 76 ns, tPHL = 1.1 ns, tPLH = 14 ns, tP = 7.5 ns t f and PHL are the same as for the resistor load: tf 0.15pF 2.06 25x10 PHL 6 1 0.14.75 5 1 ln 2 1.87 ns 2 5 1 5 1 5 0.94.75 0.15pF 2.06 25x10 6 5 1 1 4 1 0.886 ns ln 5 1 5 0.25 2 Estimates for t r and PLH were not developed in the text , but we see from Fig. 7.40 that they will be less than those for the saturated load resistor and greater than those of the resistor load. 2.2RC tr 160 R ONLC 9 2.295k 0.15pF t r 17.78 0.15pF 31.4ns t r 100ns 6 1 25x10 5 1 0.25 3.53 0.69RC PLH 2R ONL C 0.69 95k0.15pF t PLH 7.62 18 20.15pF 8. 80ns PLH 11. 3ns 1 5 1 0.25 3.53 25x10 6 *Problem 7.62 - Linear load cascade inverter delay VDD 1 0 DC 5 VGG 8 0 DC 7.5 VI 2 0 PWL (0 5 0.1N .25 100N .25 100.1N 5 200N 5) ML1 1 8 3 0 NMOSFET W=2U L=18.06U AS=8P AD=8P MS1 3 2 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML2 1 8 4 0 NMOSFET W=2U L=18.06U AS=8P AD=8P MS2 4 3 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML3 1 8 5 0 NMOSFET W=2U L=18.06U AS=8P AD=8P MS3 5 4 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML4 1 8 6 0 NMOSFET W=2U L=18.06U AS=8P AD=8P MS4 6 5 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML5 1 8 7 0 NMOSFET W=2U L=18.06U AS=8P AD=8P MS5 7 6 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .OP .TRAN 0.2N 200N .PROBE V(2) V(3) V(5) V(6) .END The results of this problem are highly dependent upon the models used. The model must include capacitances. Thus, at a minimum, the TOX parameter must be specified. For the models above: First inverter: t r 19ns t f 0.5ns PLH 3.8ns PHL 0.2ns C= PHL 1 0.4 x10 9 R ons V 1 DD V TNS 1 ln 4 V V 2 DD OL 2. 0625x10 6 5 1 51 1 4 1 ln 2 5 0.25 68 fF Fourth inverter: t r 19ns t f 3.5ns PLH 3. 8ns PHL 0.4ns Rise time and PLH are controlled by the slow transition of the load device and are essentially the same. Fall time and PHL are faster for the first inverter because of the much faster input signal transistion. 7.63 We will start by assuming P PLH since we expect PLH PHL 2 3 3 3 0.25 PLH R onLC ln 4 1 2 1. 046R onLC 3 3 0.25 R onL 2 3ns 1 2. 324 W 5.736k | 6 1.046 1pF L L 5736 25x10 3 1 W must be chosen to set the design value of VOL L S 19 0. 25 25 x10 6 2. 324 22. 3 W 2 W 25x10 6 3 1 0. 25 3 L S 2 2 1 L S 1 Now find the actual value of P PHL 1pF 22.3 25x10 6 31 6.789 1 ln 4 1 0.789ns P 3. 40ns 3 0.25 2 2 3 1 To compensate for this error, we simply rescale the device sizes which changes the currents but not the value of VOL . W 22.3 3.40ns 25. 3 | W 2.324 3.40ns 2.63 L S 1 3ns 1 L L 1 3ns 1 tf tr 7.64 1pF 25.3 25x10 6 1pF 2.63 25x10 6 1 0.12.75 3 1 1 2 ln 2 2.07 ns 31 3 1 3 0.9 2.75 203 3 3 0. 25 0.12.75 ln 2.75 1 2 13.6 ns 3 3 *Problem 7.64 VDD 3 0 DC 5 VI 1 0 DC 0 PWL (0 0.25 1N 5 25N 5 26N 0.25 300N 0.25) CL 2 0 0.20PF ML 3 2 2 0 DMOSFET W=1U L=2.15U MS 2 1 0 0 NMOSFET W=2.06U L=1U .MODEL DMOSFET NMOS LEVEL=1 KP=25U VTO=-3 GAMMA=0.5 PHI=0.6 .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 .OP .DC VI 0 5 0.01 .TRAN 0.25N 300N .PROBE V(1) V(2) .PRINT TRAN V(1) V(2) .END Results: tf = 3.3 ns, tr = 26 ns, tPHL = 1.4 ns, tPLH = 11 ns, tP = 6.2 ns tf 2.06 25x10 PHL tr 0.2pF 6 0.2pF 2. 06 25x10 5 1 1 0.14.75 1 2 ln 2 2.49 ns 5 1 5 1 5 0.94.75 6 0. 2pF 1 6 25x10 2.15 5 1 1 4 1 1.18ns ln 5 1 5 0.25 2 20 2. 93 5 2.93 0.25 0.14.75 1 2 ln 19.6 ns 4.75 2. 93 2. 93 2. 93 0. 2pF 5 2.93 0.25 1 2 ln 4 9.54 ns 1 2.93 25x10 6 2. 93 5 0.25 2.15 1.18 9.54 P 5.36 ns 2 PLH 20 7.65 *Problem 7.65 - Depletion load cascade inverter delay VDD 1 0 DC 5 VI 2 0 PWL (0 5 0.1N .25 50N .25 50.1N 5 100N 5) ML1 1 3 3 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MS1 3 2 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML2 1 4 4 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MS2 4 3 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML3 1 5 5 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MS3 5 4 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML4 1 6 6 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MS4 6 5 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P ML5 1 7 7 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MS5 7 6 0 0 NMOSFET W=4.12U L=2U AS=16P AD=16P .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .MODEL DMOSFET NMOS LEVEL=1 KP=25U VTO=-3 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .OP .TRAN 0.2N 100N .PROBE V(2) V(3) V(5) V(6) .END The results of this problem are highly dependent upon the models used. The model must include capacitances. Thus, at a minimum, the TOX parameter must be specified. For the models above: First inverter: t r 2. 6ns t f 0.3ns PLH 1.3ns PHL 0.15ns 1 C = PHL 0.15x10 9 R ons V 1 DD V TNS 1 ln 4 V V 2 DD OL 2.06 25x10 6 5 1 5 1 1 4 1 ln 2 5 0.25 25 fF Fourth inverter: t r 2.6ns t f 1ns PLH 1.3ns PHL 0.4ns Rise time and PLH are controlled by the slow transition of the laod device and are essentially the same. Fall time and PHL are faster for the first inverter because of the much faster input signal transistion. 7.66 *Problem 7.66 - 2-Input Depletion load NAND Gate VDD 5 0 DC 5 VB 3 0 DC 5 VA 1 0 DC 5 PWL (0 5 0.1N .25 100N .25 100.1N 5 200N 5) *NAND1 - A Input Switching ML1 5 4 4 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MSB1 4 3 2 0 NMOSFET W=8.48U L=2U AS=16P AD=16P MSA1 2 1 0 0 NMOSFET W=8.12U L=2U AS=16P AD=16P *NAND2 - B Input Switching ML2 5 6 6 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MSB2 6 1 7 0 NMOSFET W=8.48U L=2U AS=16P AD=16P MSA2 7 3 0 0 NMOSFET W=8.12U L=2U AS=16P AD=16P *NAND3 - Both Inputs Switching ML3 5 9 9 0 DMOSFET W=2U L=4.30U AS=8P AD=8P MSB3 9 1 8 0 NMOSFET W=8.48U L=2U AS=16P AD=16P 21 MSA3 8 1 0 0 NMOSFET W=8.12U L=2U AS=16P AD=16P .MODEL NMOSFET NMOS LEVEL=1 KP=25U VTO=1 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .MODEL DMOSFET NMOS LEVEL=1 KP=25U VTO=-3 GAMMA=0.5 PHI=0.6 +TOX=40N CJ=390U CJSW=500P CGDO=330P CGSO=330P CGBO=395P .OP .DC VA 5 0 .01 .TRAN 0.2N 200N .PROBE V(4) V(6) V(9) .END The VTC for the case of B is shifted by approximately 0.1 V relative to the case for A switching, and the case of both switching is shifted by an additional 0.3 V. The delay results for this problem are highly dependent upon the models used. The model must include capacitances. Thus, at a minimum, the TOX parameter must be specified. For the models above: A switching: t r 3.5ns t f 0. 3ns PLH 2.6ns PHL 80ps B switching: t r 1.5ns t f 0. 25ns PLH 0.8ns PHL 130ps For both inputs switching, the results are identical to the B switching case. 7.67 a V TN 1 0.5 0. 25 0.6 0.6 1.07 V 50x10 6 25x10 6 W 1 2 W 5 0. 25 1.07 L L L L 3.39 2 b 50x10 6 25x10 6 W 1 2 W 5 0. 25 1 2 L L L L 3.52 W 4.75 W c 50x10 6 25x10 6 7.5 0. 25 1. 07 4.75 L L 2 W L L d 50x10 6 25x10 6 7. 5 0.25 1 L L 1 9.03 4.75 1 W 4.75 2 L L 9. 20 e V TN 3 0.5 0. 25 0. 6 0. 6 2. 93V 50x10 6 25x10 6 W 1 2 W 2.93 2 L L L L 2.15 f 50x10 6 25x10 2 6 W W 1 2 3 L L L L 2.25 7.68 For VDD = -5 V, we have VOH =-0.25 V with a power dissipation of 0.25 mW. Since these gates are all ratioed logic design, the ratio of the W/L ratios of the load and switching transistors does not change. We only need to scale both equally to achieve the power level. 22 W 25 2.06 5.15 (a ) R L 95k L S 10 1 1 25 1 1 25 3.53 8. 83 W W (b) | L L 10 3.39 1.36 L S 10 1 1 W 25 1 1 W 25 5.15 (c) | 2. 06 L L 10 9. 03 3. 61 L S 10 1 W 25 1 1.16 W 25 2.06 5.15 (d) | L L 10 2.15 1 L S 10 1 1 7.69 2 V OH 1 10 5 2 V OL 5 1 4 V | 10 -5 5 V OH 1 4 1 V OH 1 2 4 2 9V 2OH 56V OH 16 0 V OH 0. 300 V 7.70 Pretending this is an NMOS gate and using symmetry of the equations : V DD 5 | V OH 4V | V OL 0.300 V | V TN 1V | V IL V TN 1V V IH : V O 5 1 1 3 2 /1 1/ 4 0.800 V | V IH 1 0.800 1/ 4 1 5 0.8 12 2. 20V 2 22 /1 0. 800 Then for the PMOS gate, V IH 1V and V IL 2.20 V NM L V IL V OL 2.20 4 1.80 V | NM H V OH V IH 0.3 1 0.700 V 7.71 Note that VTO is incorrect in the first printing and K'p should be 10 A/V2. Pretend this is an NMOS gate with VDD 3.3V and V OL 0.33 V V OH 3. 3 0. 7 0.5 V OH 0.33 0.6 V TNL 0.7 0.5 30. 3A 0.6 0.6 V OH 2.16 V 0.1mW 30. 3A 3.3V 1. 28 W L L 1 0.6 0.795 | I DS 10A W 2 3.3 0.33 0.795 2 L L 0.33 7.09 W W 30. 3A 10A 2.16 0.70 0.33 L S 2 L S 1 7.72 23 Using the results from Problem 7.71 and pretending this is an NMOS gate: V DD 3.3 V | V OH 2.16V | V OL 0.33V | V TN 0.7V | V IL V TN 0.7 V V IH : V O 3.3 V TNL 7. 09 1 3 1.28 V | V TNL 0.7 0.5 O 0. 6 0. 6 Solving these two equations yields V O 0.582V | V TNL 0.856 V V IH 1 0.582 1.28 1 2 3. 3 0.581 0. 856 1.83V 2 27.09 0.582 For the PMOS gate, these become VIH 0.70V and V IL 1.83 V NM L V IL V OL 1. 83 2.16 0.33 V | NM H V OH V IH 0. 33 0.7 0.37 V 7.73 V OL V TP | V OL 1 0.5 5V OL 0. 6 0. 6 V OL 1.611V ' K p W V 2 ' W K p V SGS V TP SDS V SDS V SGL V TL L S 2 2 L L 5 V OH 3 1 1 2 5 1. 61 1 5 V OH V OH V TPL 1 2 2 3 V TPL 1 0.5 5 V OH 0.6 0.6 Solving the last two equations iteratively : V OH 4. 677 V 7.74 Y is low only when both A and B are high: Y AB or Y = AB. Alternatively, Y is high when either A or B is low: Y A B AB 7.75 7.76 Y is high only when both A and B are low: Y AB or Y = A + B The Using the SPICE lisiting below, VOH = 4.0 V, VOL = -0.300 V. *Problem 7.76 Simulation of Fig.P7.69 VDD 3 0 DC -5 VI 1 0 DC 0 ML 3 3 2 2 PMOSFET W=1U L=4U MS 2 1 0 0 PMOSFET W=2U L=1U .MODEL PMOSFET PMOS LEVEL=1 KP=10U VTO=-1 GAMMA=0 PHI=0.6 .DC VI 0 -5 0.05 .PRINT DC V(1) V(2) .END 7.77 Using the SPICE lisiting below, VOL = -2.16 V, VOH = -0.33 V and IDS = 30.3 A. *Problem 7.76 - Simulation of the design of Fig. P7.71 VDD 3 0 DC -3.3 VI 1 0 DC 0 ML 3 3 2 0 PMOSFET W=1.28U L=1U MS 2 1 0 0 PMOSFET W=7.09U L=1U .MODEL PMOSFET PMOS LEVEL=1 KP=10U VTO=-0.7 GAMMA=0.5 PHI=0.6 .DC VI 0 -3.3 0.05 24 .PRINT DC V(1) V(2) I(VDD) .END 7.78 Using the SPICE lisiting below, VOL = 1.61 V, VOH = -4.68 V. *Problem 7.78 Simulation of Fig. P7.73 VDD 3 0 DC 5 VI 2 0 DC 0 ML 0 0 1 3 PMOSFET W=1U L=3U MS 1 2 3 3 PMOSFET W=3U L=1U .MODEL PMOSFET PMOS LEVEL=1 KP=10U VTO=-1 GAMMA=0.5 PHI=0.6 .DC VI 0 5 0.05 .PRINT DC V(1) V(2) I(VDD) .END 7.79 Using the SPICE lisiting below: *Problem 7.79 - Simulation of Fig. P7.69 VDD 3 0 DC -5 VI 1 0 PWL (0 -0.3 1N -4 250N -4 251N -0.3 3000N -0.3) CL 2 0 1PF ML 3 3 2 2 PMOSFET W=1U L=4U MS 2 1 0 0 PMOSFET W=2U L=1U .MODEL PMOSFET PMOS LEVEL=1 KP=10U VTO=-1 *.TRAN 1N 250N .TRAN 5N 2U .PROBE V(1) V(2) .PRINT TRAN V(1) V(2) .END tr = 1.92 s, tf = 48 ns, PLH = 215 ns, PHL = 22 ns, P = 119 ns 7.80 Using the SPICE lisiting below: *Problem 7.80 - Simulation of Fig. P7.73 VDD 3 0 DC 5 VI 2 0 PWL (0 4.68 1N 1.61 250N 1.61 251N 4.68 3U 4.68) CL 1 0 1PF ML 0 0 1 3 PMOSFET W=1U L=3U MS 1 2 3 3 PMOSFET W=3U L=1U .MODEL PMOSFET PMOS LEVEL=1 KP=10U VTO=-1 GAMMA=0.5 PHI=0.6 .TRAN 1N 300N *.TRAN 5N 2U .PRINT TRAN V(1) V(2) .END PLH tr = 41 ns, tf = 1.34 s, = 19 ns, PHL = 145 ns, P = 82 ns 25