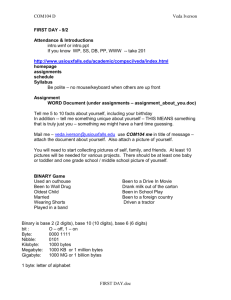

program counter:

advertisement

VAX Architecture

CPU

R0

ALU

R1

.

.

Control Unit

R12 (AP)

R13 (FP)

Local Storage

R14 (SP)

R15 (PC)

PSL

Memory Increment Bus

Memory

BI adaptor

BI Bus BI adaptor

Input/Output

devices

Structure of a VAX 8810

BI Bus

Input/Output

devices

Registers provide a local high-speed storage for the processor.

There are 16 registers (all 32-bit) in a VAX CPU

Six of these registers (R6 - R11) are general purpose registers.

R0 - R5 are also general purpose registers, however, they

should be used with care because they are also implicitly

changed by some VAX instructions.

R12 - R14 are special purpose registers

R12 - Argument Pointer

R13 - Frame Pointer

R14 - Stack Pointer

Register R15 (Program Counter or PC)

program counter:

Holds the address of the next instruction to be executed. PC is

updated by the number of bytes of the instruction.

the address of an instruction is the address of its opcode.

Process Status Register:

Stores status information which describe the current state of the

program in execution. Most important are condition codes.

Condition codes are flags that provide information about the

result obtained from instruction execution.

Codes include

- Z flag: Set if the result is 0

- V flag: Set if the result is out of range

- N flag: Set if the result is negative

- C flag: Set if there was a carry/borrow

In VAX Architecture this register is called the process status

longword

31

0

Not accessible

0000000

15

PSW

DV FU IV T N Z V C

0

T - Trace trap flag; it is used by the VAX Symbolic

Debugger.

IV - Integer Overflow Trap

FU - Floating-point Underflow Trap

DI - Decimal Overflow Trap.

When a trap bit for one of these errors is set, the VAX

hardware causes a termination of execution when that error is

detected, otherwise the error is ignored.

** Traps are exceptions that occur at the end of an

instruction.

** An exception (Software Interrupt) is problem in an

instruction that causes an interruption in the normal flow

of execution.

Register Usage in the VAX architecture:

There are 16 registers

All registers are 32-bit

Registers are numbered R0 - R15.

R0 - R11 used in programs in byte (8 bit),

Word (16 bit), or Longword (32 bits)

R0 - R5 Should be used with caution, they are

used implicitly by some instructions.

R12 - AP

R13 - FP

R14 - SP

R15 - PC (Not accessible by programmer)

Memory Organization in VAX Architecture:

Address space:

Is the set of all addresses. The number of bits on the

address bus determine the address space of the

machine

ex.

32-bit address bus can address up to 4GByte of memory

Digression:

210 = 1K

220 = 1M

230 = 1G

Virtual Memory:

The idea of executing a program while only a portion of

the program resides in main memory. (make believe that

there is more physical memory available). This is done by

breaking the program into equal size blocks (pages) and

bringing it into main memory on demand. The operating

system handles this mapping between the VM and physical

memory.

The VAX address bus is 32-bit (every address is a 32 bit

unsigned integer)

address space is 4GB

1/2 is used by users programs

1/2 is used by the system

Addresses are virtual addresses, not physical

Memory is organized in bytes (byte –addressable)

If a data item is more than one byte, contiguous memory cells

will be allocated for it. VAX uses the little-endian

technique. (least-significant byte first)

address of data b0

byte1

byte0

b1

Data Types Supported by VAX

BYTE

WORD

LONGWORD

QUADWORD

OCTAWORD

8 bits

16 bits

32 bits

4 words (8 bytes)

8 words (16 bytes)

Instruction Format:

In the source file....

[Label:] Opcode Operand_Specifier_1,

Operand_Specifier_2, ..... [;Comment]

[ ] is an optional field.

ex. ADDL2 R1, R2

memory layout of instructions

opcode

op

spec.

.

.

The first Byte of each instruction is an opcode (operation

code).

The address of an instruction is the address of the byte

where the opcode is stored.

Opcodes in the VAX are one byte (most of them). Very

few opcodes are two bytes.

Opcodes tell the CPU the following information:

1- The operation

ex.

1000 0000 in VAX is an ADDB2 instruction

2- Number of operands

ex.

1000 0000 requires two operands

ADDB2 R1, R2

R1,and R2 are operands

3- Data type upon which it will operate

ex. ADDB2 operates on byte data.

Data type is specified using letters

B Byte

W Word

L Longword

Q Quadword

O Octaword

D, F, H, G data type for floating-point data...

Symbols are names of variables, subprograms, and they

label instructions.

Symbols are made up of letters, digits, and underscore.

Must start with a letter and must be less than 31 chars.

A Label is a symbolic name for an address. If an

instruction is started with a label, then it can be

addressed by this label in the program. We use a label to

allow for branching, and naming memory location.

ex. Label: ADDB2 R1, R2

The Label here is the address of this instruction.

label

opcode

rest

of inst.

- Not every instruction needs a label.

Operands are either in memory or in registers.

Programmers must specify the ways in which the

instruction will find them. The different ways in

specifying the location of the operands are called

ADDRESSING MODES.

Effective Address:

Is the address where the operand is stored (the address

where data to be operated on is located)

In the VAX there are 20 different addressing modes.

There are 3 types of statements that can appear in a

source file in the MACRO assembly language

Instructions.

These are executable instructions. They get translated into

machine code by the assembler and executed at run time.

ex.

ADDL2, DIVB3, LOCC, MOVC5 and all the

instructions in the instruction set.

Pseudo-instructions (Macros)

These are names that get replaced by the assembler by a

sequence of other instructions that do a certain task. (We

will talk about Macros in Chap. 11)

Directives.

These are instructions (NOT EXEUTABLE) to the

assembler to perform various bookkeeping tasks, storage

reservations, and other control functions.

They start with "." in the front of the instruction.

ex. .LONG, .BYTE

- Directives are not translated to machine code.

- They resemble declarations in HLLs.

Storage (memory) Reservation in Assembly:

There are two types:

1- Reserve blocks with an initial value of 0

ex. int x,y; (in C)

2- Reserve blocks with initial values

ex. int x = 3;

Reserving initialized memory

.BYTE

.WORD

.QUAD

.OCTA

.ASCIZ and more

.LONG

.ADDRESS

.ASCII

-Each one of the above directives takes a list of

arguments.

-The argument of these directives is the value to

which the memory is initialized

Ex.

X: .BYTE 5

This tells the assembler to allocate a byte of memory and

initialize it to 5.

The assember uses two's complement to represent

negative numbers.

X: 0000 0101

ex.

W: .LONG 7

W:

0000 0111

0000 0000

0000 0000

0000 0000

ex.

Fernando: .WORD -3

Fernando

1111 1101

1111 1111

ex.

Alpha: .BYTE 3, 5, 76

Multiple blocks can be allocated with one directive

ex.

X: .BYTE 5[3]

of blocks}

{number between [] is the number

Allocating memory for character string

(.ASCII, .ASCIZ)

Use ASCII code. Each char occupies a byte.

Must use delimiters like / , " , {, ...

Any character can be used as a delimiter so long as this char

does not appear in the character string.

The .ASCII directive allocates a byte for each char in the

string.

.ASCIZ is the same as .ASCII except it adds an extra (all

zeros) byte at the end of the string. A zero byte is the NULL

character in ASCII.

ex.

message: .ASCII /Hello World/

MSG: .ASCIZ "this is fun"

User Defined Symbols

The user can define symbols explicitly by equating them to

the desired value. (Direct Assignment)

Symbol = Expression

*** This is not an assignment statement as in HLL.

ex.

CR = 13

LF = 10

This is like a DEFINE directive in C

The assembler replaces each occurrence of these symbols by

their values during assembly.

ex.

MAX = 10

B : .BYTE 61

Control characters are ASCII codes that are not printable.

Example: a carriage return or line feed.

To include control characters in the program we must

use their ASCII representation (code) in angle brackets

ex.

linefeed <10>

Carriage return <13>

ex.

T1: .ASCIZ /Hello World/

T2: .ASCII /Firas is/ <13><10> /human/

T3: .ASCII /So what/

Reserving Uninitialized memory

.BLKx

where x = B, W, L, O, Q, A, and more

ex.

.BLKB 3

.BLKW 1

The argument specifies the number of blocks to be

reserved.

The assembler allocates the blocks and initializes them

to zeros.

In the above example .BLKB 3 tells the assembler to

allocate 3 bytes

Memory allocation should be before or after the

executable instructions.

You can have a memory allocation directive within

executable instructions as long as you have a way to

jump over these blocks. (we will talk more on this later)

** All constant values in the assembly program are

decimal numbers unless explicitly specified

otherwise.

To represent constants with number systems other than

decimal a special operator must be used. The operator is

followed by one of the symbols (B, X, O, C, A).

B

X

O

C

A

for binary

for hexadecimal

for octal

used to form the one's complement of its argument

for ASCII code

ex. ^B10110011

^XF76E

^A/F/ (ASCII value of the char F

Beginning and Ending Programs:

.ENTRY Directive

- Establishes an entry point

- Entry point is a place where execution starts.

.ENTRY symbol, Mask

ex.

.ENTRY main, ^M<IV>

The next instruction should be an executable instruction.

The symbol in the directive is the address of the first

instruction of the program.

.END Directive

Tells the assembler that this is the end of the module

that is being translated.

Each file must have a .END directive at the end of the

file.

.END

transfer_address

Transfer address is a symbol that specifies where

execution of the program is to begin.

Transfer address should be the same as the symbol in

the .ENTRY directive.

$EXIT_S Macro

It terminates the execution of the program

It is a macro that gets replaced by a sequence of

instructions

ex.

ALPHA: .LONG 224

BETA: .BLKL 1

.ENTRY EXAMPLE, ^<IV>

MULL3 #3,Alpha,R6

SUBL3 #20,R6,Beta

$EXIT_S

.END EXAMPLE

Instructions:

Arithmetic

operation

type

ADD

SUB

MUL

DIV

B,W,L

B,W,L

B,W,L

B,W,L

ADDx2

op1 + op2 op2

ex.

x = x+y

ADDL2 Y,X

# of operand

2,3

2,3

2,3

2,3

op1,op2

ADDx3 op1,op2,op3

op1+op2 op3

the same applies to MUL instruction

SUB

SUBx2 op1, op2

op2 – op1 op2

SUBx3 op1, op2, op3

op2 – op1 op3

DIV

DIVx2 op1, op2

op2/op1 op2

DIVx3 op1, op2, op3

op2/op1 op3

Ex.

Compute

R7 R44 + R3 * R6

Special Purpose Instructions:

MOVx

Source, Dest.

X = B, W, L, Q, O

Source Dest.

Ex.

MOVL R2, R4

INCx operand

X = B, W, L

Operand +1 operand

DECx operand

X = B, W, L

Operand – 1 operand

MNEGx source, dest.

X = B, W, L, Q, O

(- source) dest.

Ex.

R8 =

CLRL

0000 9AFF

R8

CLRB

R8

CLRW

R8

INCB

R8

INCW

Ex.

R8

FFED 01A2 R4

1234 00D7

R6

0002 1044

R10

Alpha

10

00

1A

40

Beta

04

F1

FF

FF

Gamma 3B

0A

48

27

0002 1044

0002 1045

0002 1046

0002 104F

ADDW2 R4, R10

ADDB3 ALPHA,BETA, R6