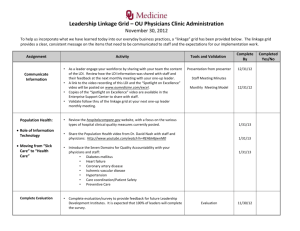

CH 1 ATMega168晶片特性分析

advertisement

蔡樸生 0920-038438,

課程名稱 :嵌入式晶片程式設計

班

別 : 夜二技電子三甲/四甲

上課時間 : 星期日 (3,4,5)

Web: http://ee.cust.edu.tw/tps

email: tsaipusheng@gmail.com

參考書籍:

(1)郁文工作室, ”嵌入式 AVR 程式設計”, 全華圖書公司

(2)李彥杰、葉郁欣, 徐祥憲, 黃克穠, 任善隆, “AVR 控制應用與實

務 –使用 ATmega8515 與 C 語言” , 高立出版社

(3) 陳漢宗、石博元,”AVR 單晶微控器-使用 C 語言”,文魁出版社

(4) ATMega 162 User Guider , 2007 Atmel Corporation.

Application:

(1) Mobile Robot

(2) Human Manipulator Robot

(3) Physiology Signal Measuring System

(4) Integrated Application of INS and GPS

(5) ABS

Chapter I ATMega168 晶片特性

CHINA UNIVERSITY OF SCIENCE AND TECHNOLOGY

DEPARTMENT OF ELECTRONIC ENGINEERING

EDITED BY ASSOCIATED PROFESSOR PU-SHENG TSAI

Features

• High-performance,

Low-power AVR® 8-bit Microcontroller

4 : nibble, 8: byte, 16 : word 32:dword

8 bit: width of bus

32 bit : speed 最快, 耗電最高

4bit : speed 最慢, 最省電

1. 嵌入式微控制器 Embedded MicroController Unit (EMCU)

89S51, ATMega162, PIC18F4520

2. 嵌入式微處理器 Embedded MicroProcessor Unit (EMPU)

ARM9, ARM10

3. 嵌入式 DSP 處理器 Embedded Digital Signal Processor (EDSP)

TMS32C5X, TMS32C6X

4. 嵌入式晶片上系統 Embedded System on Chip (ESOC)

Nios, Psoc

• Advanced RISC Architecture

RISC : Reduced Instruction Set Computing 精簡指令集

1. 指令很少 : 131

2. 每一個指令佔一個記憶體的單位(2 byte)

3. 每一個指令執行時間只佔一個機械週期 (machine cycle)

CISC: Complex Instruction Set Computing 複雜指令集

Since all AVR instructions are 16 or 32 bits wide,

ex 1: By using AVR studio to prove the AVR chip is RISC

…..

每一個機械週期

[Case I] AVR Chip (RISC)

Using 12 MHz osc., machine cycle = 1/ 12 us

rjmp here : 佔 1/6 us

[Case II] 89S51

Using 12MHz osc.

每一個振盪週期所佔時間: 1/12 us

每一個狀態週期所佔時間: 1/6 us

每一個機械週期所佔時間: 1us

nop (1us),

MUL , DIV (4us)

AVR 執行速度為 89S51 快 12 倍以上。

;============================================================

;BASIC_1:

MEMORY ACCESS (SRAM WRITE)

;

Prove that ATMega162 is RISC

;2012/09/13

;============================================================

.include "m162def.inc"

.include "basic.inc"

.cseg

.org

0

rjmp

start

;============================================================

;main program

;============================================================

start:

;(1)Set Stack Pointer(SP)堆疊指標

ldi

out

ldi

buf_1,low(RAMEND)

SPL,buf_1

buf_1,high(RAMEND)

out

SPH,buf_1

;(2)Set I/O PORT MODE 輸出/輸入模式

;

PORTC : OUTPUT

ldi

buf_1,$ff

out

DDRC,buf_1

out

PORTC,buf_1

ldi

r27,$01

;X = $0100 index register

ldi

ldi

ldi

r26,$00

buf_1,255

buf_2,$aa

;counter

;data

st

dec

brne

X+,buf_2

buf_1

L1

st

dec

X+,buf_2

buf_1

brne

L2

st

dec

brne

X+,buf_2

buf_1

L3

st

dec

brne

X+,buf_2

buf_1

L4

st

X,buf_2

L1:

L2:

L3:

L4:

here:

rjmp

here

;==============================================

;

BASIC.INC

;==============================================

.def

buf_1

=r16

.def

buf_2

=r17

.def

.def

.def

.def

.def

.def

.def

.def

buf_3

buf_4

count

index

code

cmd

data

delay_time

=r18

=r19

=r20

=r21

=r22

=r23

=r24

=r25

.equ

.equ

.equ

.equ

.equ

.equ

LCD_BUS

LCD_DDR

LCD_PIN

e

rw

rs

=PORTC

=DDRC

=PINC

=3

=2

=1

.equ

.equ

.equ

KEY_BUS

KEY_DDR

KEY_PIN

=PORTA

=DDRA

=PINA

SRAM:

– 131 Powerful Instructions – Most Single-clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– X , Y , Z denoted as 索引暫存器

[指令集] 搬移指令

Immediate data

(x)

ldi

( x ) ldi

(O)

(O)

(O)

(O)

(x)

(x)

(x)

(x)

Register ldi

rd, K($K)(0b001.)

r3,48

ldi

r16,#48

rd (r16 ~ r31)

K=0 ~ 255

ldi r28,48

ldi r19,$48

ldi r19,0x48

ldi r18,0b01001000

ldi r23,256

cpi r7,$7a

andi r7,$7a

ori r7,$7a

note: cpi, andi, ori 運算子為 r16 ~ r31 與立即資料。

[指令集] 搬移指令

Register

Register

(x)

ldi

r3,48

(O)

ldi

r16,48

(O)

mov

r3,r16

MOVW

(

)

Rd, Rr

movw

mov(movw) rd, rs (byte, word)

mov

movw

rd(r0 ~ r31)

Rd+1:Rd

r4,r16

rs(r0 ~ r31)

<- Rr+1:Rr

r17 -> r5, r16 -> r4 (even)

(x

)

movw

r5,r17

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

MIPS : Mega instruction / second

在 20MHz 的工作頻率下,每一個指令之執行速度可達到 50ns。

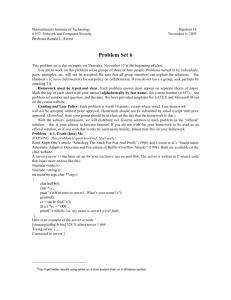

ex2 : 藉由 AVR 每個指令與時脈關係,設計 delay_01ms 與 delay_10ms 模組

利用 matlab 來解二元一次方程式求最逼近解

執行指令

指令週期

執行次數

delay_3:

ldi

buf_3,#x

1

z

delay_2:

ldi

buf_4,#y

1

xz

delay_1:

dec

buf_4

1

xyz

brne delay_1

2

2xyz

dec

1

xz

brne delay_2

2

2xz

dec

1

z

brne delay_3

2

2z

ret

1

1

buf_3

delay_time

(1+(1+(1+2)y+1+2)x+1+2)z+1

=(1+(1+y+2y+1+2)x+1+2)z+1

=(1+x+xy+2xy+x+2x+1+2)z+1

=(4 + 4x +3xy) z +1

* (4+4x+3xy) *

(1) delay 0.1ms

1

×(3xy+4x+4)=0.0001

11059620

3xy+4x+4 1104

[(3y+4)x+4] 1104

Taking the value of x=5,y=72

(2) delay 10ms

1

×(3xy+4x+4)=0.01

11059620

110596=3xy+4x+4

[(3y+4)x+4] 110596 110604

Taking the value of x=200,y=183

AVR 速度比 MCS_51 快 12 倍以上

藉由 AVR 每個指令與時脈關係,設計 delay_01ms 與 delay_10ms 模組

利用 matlab 來解二元一次方程式求最逼近解

3xy + 4x +4 = 110596.2

y= (110596.2 – 4x – 4)/3x

0<x<255,

0<y<255

clear all;close all;

for k=1:255

x(k)=k;

t(k)=k;

y(k)=fix((110592.2-4*x(k))/ (3*x(k)));

e(k)=abs(110592.2-3*x(k)*y(k)-4*x(k));

end

x=184, y=199 (10ms)

[case I] : 延遲 1 秒鐘

ldi

delay_10ms : 10ms

delay_time,100

rcall delay_10ms

~2.55s

[case II]: 延遲 20ms 時間

ldi

delay_01ms: 0.1ms ~ 25.5ms

delay_time,2

rcall delay_10ms

l

ldi

delay_time,200

rcall delay_01ms

Problem:

(3xy+4x+4) * (1/11.05962*106)=0.0001

(3xy+4x+4) = 1105.962

(3xy+4x)=1101.962

(1)

(1101.962-4x)/3x

Optimal Solution: x = 3, y = 121, or x =20 , y=17

for delay 0.1ms

(3xy+4x+4) * (1/11.05962*106)=0.01

(3xy+4x+4)=110596.2

3xy + 4x =110592.2

(2)

Optimal Solution: x = 172, y = 213, for delay 10ms

On-chip 2-cycle Multiplier

• High Endurance Non-volatile Memory segments

– 16K Bytes of In-System Self-programmable Flash program memory

Flash ROM : +5V, small current(mA) 可以作程式燒錄(ISP)

–

In System Programming(ISP)

Batch File : 燒錄時間短

– On-chip 2-cycle Multiplier

• High Endurance Non-volatile Memory segments

–

16K Bytes of In-System Self-programmable Flash program memory

–

Addressing : 0000H ~3FFFH

ex2: 16K 定址由:

0000H

~

3FFFH

64K

0000H

~

FFFFH

9K

~

9K=8K+1K

$0000 ~ $1FFF (2000H)

+ $0000 ~ $03FF

$0000 ~ $23FF

ex3: The ATmega162 contains 16K bytes On-chip In-System

Reprogrammable Flash memory for program storage. Since all AVR instructions are 16 or 32 bits wide,

the Flash is organized as 8K x 16.

AVR 的程式記憶體, 每一個位址所佔之空間為

2

位元組 (Bytes),

由 studio 4.0 Memory 中觀察

example : 假定 user 寫成是用掉 16 K flash ROM, 每張 A4 紙可印 40

行, 試問共需幾張 A4 紙.

Function:

(a) 存放本文程式之 machine code.

(b) 中斷向量表,中斷服務副程式(Interrupt Service Routine, ISR)之起始位址

(c) 存放表格資料 (Table)

[example]

試比較以下 IC 之內部功能 ATMega8515, ATMega162, ATMega128,

PIC18F452, 89s51 , 試以表格方式列出記憶體, 執行速度, 內部功能

.cseg

; Reset and Interrupt Vector Area

.org

rjmp

.org

rjmp

.org

rjmp

0

start

EXT_INT1

?

TIM0_OVF

.

.

.

.

; External module include setup area (path need to be set)

.include

.include

.include

"m162def.inc"

"delay_10ms.asm" ; file path is needed to set

"scan_keyboard.asm"

.

.

.

Access Table Data Method :

[指令集] 搬移指令

ROM

lpm

lpm

Register

rd,Z (r0 ~ r31)

r0

相關操作指令

adiw

d {24, 26, 28,30}, 0 K 63

rd,K

rd 1: rd rd 1: rd K

adiw

r24,1;

ldi

ldi

lpm

lpm

lpm

adiw

str_table:

將 r25:r24 內容加 1

ZH,high(2*str_table)

ZL,low(2*str_table)

r0 = 41H

r6,Z+

r6 = 41h

r0 = 42h

ZH:ZL,1

(Z)

“ABCDabcd01234”,0xaa,0xbb,0xcc,0xdd,0xee,0xff

.db

ex4: 設計一段程式,讓七段顯示器每隔一秒由 0 數到 F,並置於 studio4.0 中

的 debug 作驗證。

[Hint]: Table Data of Seven Segment Display

seg7_table:

.db

0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8

.db

0x80,0x90,0x88,0x83,0xC6,0xA1,0x86,0x8E

mov

Immediate data

ldi

lpm

Registe

r

in

out

I/O Register

lds

ld

st

sts

– 1K Bytes Internal SRAM

Z

XY

Memory

RAM

Memory

ROM

32 通用暫存器 r0 ~ r31 ($0000 ~ $001F)

64 I/O 暫存器 ($0020 ~ $005F) : Special Function Register

160 擴充 I/O 暫存器 ($0060 ~ $00FF)

1K 內部 SRAM 記憶体 ($0100 ~ $04FF) : 存放程式中所用到的

資料, 變數以及工作旗標.

(5) 外部擴充 SRAM 記憶体 ($0500 ~ $FFFF): 最大可擴充至 64K

(1)

(2)

(3)

(4)

[指令集] 搬移指令

Register

Memory (Direct Addressing)

lds

rd, k

sts

k, rd

lds

rd (r0 ~ r31)

k ($0000 ~ $ffff)

sts

lds

r3,$0600

(off chip memory)

lds

r3,$0200

sts

$0200, r3

.equ

ult_L

lds

r3, ult_L

sts

ult_L, r3

lds

r17,$fe00

(on chip memory)

=$0100

(off chip memory)

[指令集] 搬移指令

Register

Memory (Indirect Addressing)

ld

rd, X(Y,Z)

ld

rd, -X(Y,Z)

ld

rd, X-(Y,Z)

ld

(X), (Y), (Z)

rd (r0 ~ r25)

st

MOV A,@R0

MOV A,Rn

MOV Rn,A

MOV @R0,A

(R0, R1) 才能作間接定址

[Example]

for

ldi

ldi

ld

ld

ldi

ld

ld

ATMega8515

RAM address = $0060

r27,$00

r26,$60

r0,X+

r1,X

r26,$63

r2,X

r3,-X r0 =

66H

39H

A4 H

78H

, r1 =

, r2 =

$0060

, r3 =

ex5: 試設計 AVR162 間接定址的程式,將 SRAM 記憶体全部清除為 $AA,並

置於 studio4.0 中的 debug 作驗證。

====================================================

ldi

ldi

ldi

ldi

r27,$0101

; X= $0100 index register

r26,$0000

buf_1,25555 ;counter

buf_2,$aa$aa ;data

stst

dec

X+,buf_2 buf_2

buf_1

brne

L1

stst

dec

brne

X+,buf_2 buf_2

buf_1

L2

stst

dec

brne

X+,buf_2 buf_2

buf_1

L3

stst

dec

brne

X+,buf_2 buf_2

buf_1

L4

L1:

L2:

L3:

L4:

.

.

I/O Register :

out

in

PORTA, buf_1

buf_1, PINA

.

– 512 Bytes EEPROM

The ATmega162 contains 512 bytes of data EEPROM memory. It is organized as a separate

data space, in which single bytes can be read and written.

The access between the EEPROM and the CPU is described in the following, specifying

EEPROM Address Registers, EEPROM Data Register, and EEPROM Control Register.

• Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be

written. When EEMWE is set, setting EEWE within four clock cycles will write data

to the EEPROM at the selected address. If EEMWE is zero, setting EEWE will have

no effect. When EEMWE has been written to one by software, hardware clears the bit

to zero after four clock cycles.

• Bit 1 – EEWE: EEPROM Write Enable

When address and data are correctly set up, the EEWE bit must be written to one to

write the value into the EEPROM.

EEPROM

WRITE

EEPROM

READ

ex6 : To verify the function of EEPROM of AVR,

$00~ $ff 資料被寫入 EEPROM $00~ $ff 位置內,斷電後依序讀出並存入

SRAM $0060 的位置內。

;========== EEPROM Access =========

Ldi

count,255

ldi

code,0

ldi

buf_1,0

;EEPROM_write:

;

;

;

;

;

;

;

;

;

;

sbic

rjmp

out

out

out

sbi

sbi

inc

dec

brne

EECR,EEWE

EEPROM_write

EEARH,buf_1

EEARL,code

EEDR,code

EECR,EEMWE

EECR,EEWE

code

count

EEPROM_write

;====================================

clr

r29

ldi

r28,$60

ldi

count,255

ldi

code,0

ldi

buf_1,0

EEPROM_read:

sbic

EECR,EEWE

rjmp

out

out

sbi

in

st

inc

dec

brne

EEPROM_read

EEARH,buf_1

EEARL,code

EECR,EERE

buf_2,EEDR

Y+,buf_2

code

count

EEPROM_read

– Write/Erase cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/100 years at 25°C(1)

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

• JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

• Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– Two 16-bit Timer/Counters with Separate Prescalers, Compare Modes, and

Capture Modes

– Real Time Counter with Separate Oscillator

– Six PWM Channels

– Dual Programmable Serial USARTs

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Five Sleep Modes: Idle, Power-save, Power-down, Standby, and Extended Standby

• I/O and Packages

– 35 Programmable I/O Lines

– 40-pin PDIP, 44-lead TQFP, and 44-pad MLF

• Operating Voltages

– 1.8 - 5.5V for ATmega162V

– 2.7 - 5.5V for ATmega162

• Speed Grades

– 0 - 8 MHz for ATmega162V (see Figure 113 on page 266)

– 0 - 16 MHz for ATmega162 (see Figure 114 on page 266)