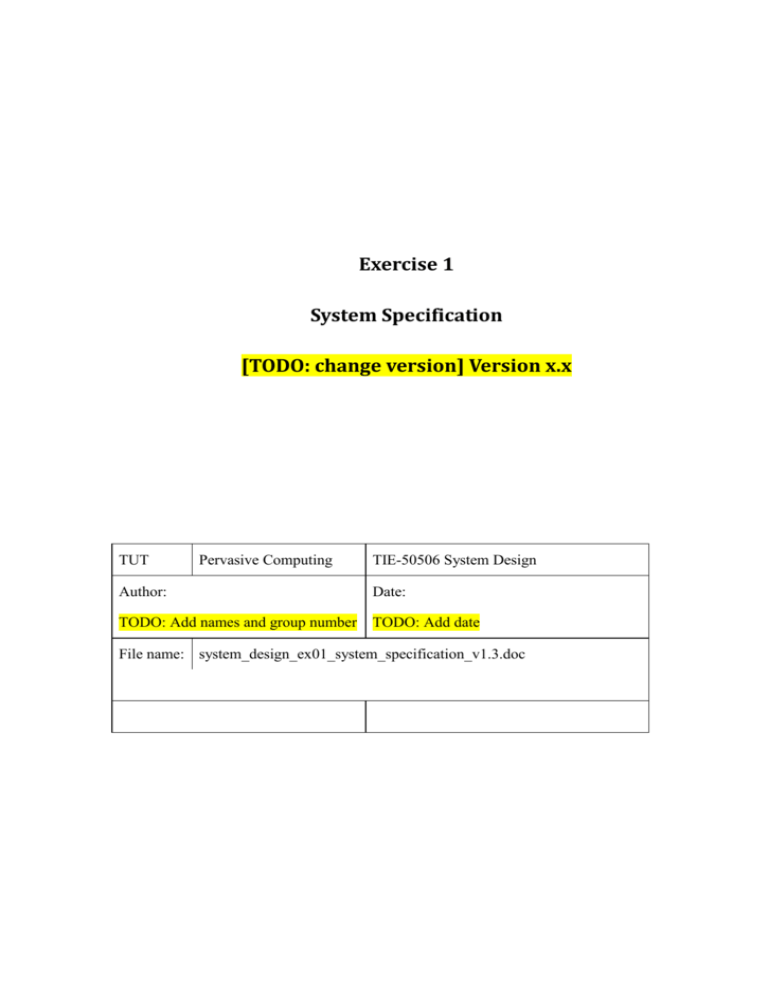

Exercise 1

System Specification

[TODO: change version] Version x.x

TUT

Pervasive Computing

TIE-50506 System Design

Author:

Date:

TODO: Add names and group number

TODO: Add date

File name: system_design_ex01_system_specification_v1.3.doc

TIE-50506 System design

Exercise 01

System specification

Version history

TODO: Change to represent specification revisions.

Version Date

Authors

Role

Details

1.0

11.01.2013

Jussi Raasakka

Creator

Initial Version

1.1

11.01.2013

TDH

Reviewer

Revision for spec template

1.2

11.01.2013

Jussi Raasakka

Editorial

Fixed few sentences

1.3

29.08.2013

LM

Editorial

Updated for the new course

Copyright notice

This document and its content is copyright of Tampere University of Technology, Department of Pervasive Computing, 2013. All rights reserved.

Any redistribution or reproduction of part or all of the contents in any form is prohibited

other than the following:

you may print or download to a local hard disk extracts for your personal and noncommercial use only

You may not, except with our express written permission, distribute or commercially exploit

the content. Nor may you transmit it or store it in any other website or other form of electronic retrieval system.

Modified: 02.09.2013 15:09

2/18

TIE-50506 System design

Exercise 01

System specification

TABLE OF CONTENTS

Version history .................................................................................................................................................... 2

Copyright notice ................................................................................................................................................. 2

TABLE OF CONTENTS ................................................................................................................................... 3

Terms and abbreviations.................................................................................................................................... 5

List of Tables ....................................................................................................................................................... 5

List of Figures ..................................................................................................................................................... 5

List of Appendices............................................................................................................................................... 5

List of Files .......................................................................................................................................................... 5

1.

INTRODUCTION .......................................................................................................... 6

1.1 Scope and purpose of this document ....................................................................................................... 6

1.2 Product ....................................................................................................................................................... 6

1.3 Requirements ............................................................................................................................................. 6

General checklist for following Chapters and sections – REMOVE THIS BEFORE FINAL

SUBMISSION ..................................................................................................................................................... 7

Present for the system and each module level: ................................................................................................. 7

a. functionality (behavior) .................................................................................................................................. 7

b. structure (architecture) .................................................................................................................................. 7

2.

OVERALL VIEW OF THE PRODUCT AND ITS DEVELOPMENT .................... 8

2.1

2.2

2.3

2.4

Description of the Application Area ........................................................................................................ 8

Product Hardware Platform .................................................................................................................... 8

Development Environment ....................................................................................................................... 8

Design workflow ........................................................................................................................................ 8

3.

SYSTEM LEVEL DESIGN ........................................................................................ 10

3.1

3.2

System Behavioral Model ....................................................................................................................... 10

System Structural Model ........................................................................................................................ 10

4.

SOFTWARE ................................................................................................................. 11

4.1

4.2

4.3

4.4

Software Design Principles ..................................................................................................................... 11

Software Architecture............................................................................................................................. 11

Software Files .......................................................................................................................................... 11

Compilation ............................................................................................................................................. 11

5.

SOFTWARE MODULES ............................................................................................ 12

5.1 Module X.................................................................................................................................................. 12

5.1.1

Introduction ..................................................................................................................................... 12

5.1.2

Function X ....................................................................................................................................... 12

6.

HARDWARE................................................................................................................ 13

6.1

6.2

6.3

Hardware architecture ........................................................................................................................... 13

Hardware Files ........................................................................................................................................ 13

Compilation/synthesis ............................................................................................................................. 13

7.

IP BLOCKS .................................................................................................................. 14

7.1 Block X ..................................................................................................................................................... 14

7.1.1

Block Connections ........................................................................................................................... 14

7.1.2

Dependencies ................................................................................................................................... 14

8.

IC ................................................................................................................................... 15

8.1

ICs............................................................................................................................................................. 15

Modified: 02.09.2013 15:09

3/18

TIE-50506 System design

8.1.1

8.1.2

9.

Exercise 01

System specification

IC Connections ................................................................................................................................ 15

Dependencies ................................................................................................................................... 15

FURTHER DEVELOPMENT .................................................................................... 16

References ......................................................................................................................................................... 16

Appendices ........................................................................................................................................................ 18

Modified: 02.09.2013 15:09

4/18

TIE-50506 System design

Exercise 01

System specification

Terms and abbreviations

TODO: Add any definitions or abbreviations (except SI units) here in alphabetical order.

DE2

Development and Education [board version] 2

EDA

Electronic Design Automation

HAL

Hardware Abstraction Layer

PSM

Process State Machine

SoC

System-on-Chip

UI

User Interface

UDP

User Datagram Protocol

List of Tables

TODO: list of ”Table X [caption]”

List of Figures

TODO: list of ”Figure X [caption]”

List of Appendices

TODO: list of “Appendix X [name]”

List of Files

TODO: list or table of files, paths and meaning

Modified: 02.09.2013 15:09

5/18

TIE-50506 System design

Exercise 01

System specification

1. INTRODUCTION

This Chapter introduces the design and explains what is contained in other Chapters.

1.1 Scope and purpose of this document

This document describes the embedded, System-on-Chip-based product specification developed in the TIE-50506 System design course [1] exercise work in fall 2013.

TODO: Add brief description what is presented in this document. Section XX presents…

TODO: Add any references that might be useful to Section 9 and cite them in text.

1.2 Product

Product is simplified version of H.263 encoder which is being created as an exercise work

for the TIE-50506 System design course [1] . Encoder implementation is implemented on

Altera DE2 Development and Education board [3]

H.263 encoder takes its input video stream from Ethernet using User Datagram Protocol

(UDP) as transport layer. Input video stream is encoded using Nios II processors and dedicated DCT hardware accelerator. Encoded video stream is then transferred out from the DE2

board using Ethernet and UDP.

Encoder has small user interface where user can see the current frame rate of encoding from

7-segment display located on DE2 board. Quantization factor for the encoding can be set

interactively using DE2 pushbuttons.

The purpose of the exercise work is to teach students few basics about SoC design, such as

abstraction, layering, inter-processor communication, operating systems designed for embedded applications, and lots more.

1.3 Requirements

TODO: refer to the requirements document and add it as appendix to this document

Complete if applicable with the following (some requirements come from in-house constraints)

Regulations, standards, certifications required

Methods, tools, design languages, design environments required

Development, testing, manufacturing, …

Non-functional requirements: Price, performance, appearance, required user expertise…

Functional requirements (overview)

Modified: 02.09.2013 15:09

6/18

TIE-50506 System design

Exercise 01

System specification

General checklist for following Chapters and sections – REMOVE THIS

BEFORE FINAL SUBMISSION

Present for the system and each module level:

a. functionality (behavior)

For system and processor (module) levels

For external and internal behavior

Process State Machine (PSM), Control Data Flow Graph (CDFG), and/or other

charts that are necessary to describe the behavior, like UML Use case diagrams, activity diagrams, message sequence charts, and timing diagrams.

Clear names for signals, packets, protocols, services

For all: modes of operation, options

b. structure (architecture)

Overall architecture

o Block diagram, class diagram, photographs, drawings, …

o Hierarchy, encapsulation, …

o HW/SW division/mapping

o Dependencies

Modules (Processing Elements, Communication Elements, …)

o Tables, block diagrams

o Interfaces (port name, type, …)

o Provided and requested communication, signals

For all: options, configurations

Modified: 02.09.2013 15:09

7/18

TIE-50506 System design

Exercise 01

System specification

2. OVERALL VIEW OF THE PRODUCT AND ITS DEVELOPMENT

This Chapter describes the overall view of the system and how it works.

2.1 Description of the Application Area

The product is an embedded video encoder that can fetch video directly from a suitable camera and stream compressed video into Ethernet. The user can control in real-time the quality

of the compressed video.

2.2 Product Hardware Platform

TODO: Describe briefly what the used DE2 board is. Also explain what resources are being

used from the board. For example the FPGA type, memories, pushbuttons etc…

Tip: Use e.g. 0.5-1 pages

2.3 Development Environment

TODO: Describe all the programs and their version numbers you are using in your product

design. These include e.g. the OS running on the Nios II processors.

Also describe all programs and their version numbers that you are using in the development

of the H.263 application.

Example: Altera Quartus version 11.0 SP1

Draw a block diagram of devices, instruments etc. that are used in the development.

Example: USB-Blaster cable is connected to the DE2 board to program Cyclone II FPGA

chip. Ethernet cable is connected between PC and DE2 board to test video streaming.

2.4 Design workflow

Explain here the product design workflow (applied from the course textbook). Use the body

below:

-

High-level system model (this document, application processes and abstract channels)

-

Executable specification for testing correct functionality and profiling performance

(implementation on PC using C-code as Basic Blocks in PSM diagram, using

Kactus2 tool for drawing the models)

-

Creating new IP-blocks for HW platform (DE2 board)

Modified: 02.09.2013 15:09

8/18

TIE-50506 System design

Exercise 01

System specification

-

Creating new SW components for SW platform (NIOS)

-

Synthesis (mapping) of application on platform (H.263 on DE2)

-

Testing, measuring and analyzing performance at each necessary steps

Modified: 02.09.2013 15:09

9/18

TIE-50506 System design

Exercise 01

System specification

3. SYSTEM LEVEL DESIGN

This Chapter describes the design at system level.

3.1 System Behavioral Model

TODO: Describe the behavior of H.263 encoder system as system level. Describe the behavior using Process State Machine (PSM). Example PSMs can be found in the course book

figures 1.7 and 3.5 [4] . You can use Powerpoint/Visio tools to draw PSM.

Refer to course book sections 1.2.5 and 3.1.2 for additional information about system behavioral model and PSMs.

3.2 System Structural Model

TODO: Describe how each process and channel is mapped to hardware. Use system structural model shown in the course book figure 1.8. Focus on the processes and communication

(channels) when drawing the diagram. You can leave out unnecessary details from the figure, such as memories which aren’t directly involved in processing or communication. These

will be presented in more detail in Chapter 6.

Refer to course book section 1.2.6 for more information on system structural model.

Modified: 02.09.2013 15:09

10/18

TIE-50506 System design

Exercise 01

System specification

4. SOFTWARE

This Chapter describes the software part of the design.

4.1 Software Design Principles

The encoder software is designed to run in top of the μC/OS-II operating system. Encoder

software is written in C and uses Nios II soft-core processors.

Communication between Nios II processors, UI peripheral devices, UDP controller, and

DCT accelerator is handled exclusively by HIBI SoC Interconnection network

Custom HIBI device driver is created for HIBI_PE_DMA hardware component. This driver

is integrated to Nios II Hardware Abstraction Layer (HAL) [5] .

4.2 Software Architecture

TODO: Describe how the software is divided into modules and how they communicate between each other. Use figure and textual explanation.

If you have SW running both on the workstation and embedded system, pay attention that

reader understand their differences, and which parts belongs where.

Add sequence diagram to show how the different tasks and modules interact. Add textual

explanation.

4.3 Software Files

TODO: Describe the software files that are used in the design.

Ex. cpu0_main.c

Application entry point for CPU0.

Categorize the files and point out the most complex ones. Give rough approximation of

number of code lines.

4.4 Compilation

TODO: Describe how software is compiled. (Tip see [6] for more information).

Modified: 02.09.2013 15:09

11/18

TIE-50506 System design

Exercise 01

System specification

5. SOFTWARE MODULES

This Chapter describes detailed information on each software module used in the design.

Tip: Use e.g. 0.5 pages per module.

5.1 Module X

TODO: Add all modules of your design into their respective sections. These modules should

contain the processes that you defined in Chapter 3 to be run on Nios II processors and some

additional helper modules if necessary.

5.1.1

Introduction

TODO: Add short introduction what is the purpose of this module and what is its purpose in

the design. If module requires other modules to perform, mention these dependencies also.

5.1.2

Function X

TODO: Add each function of the module here. For each function at least following must be

added: names, parameters, return value, and brief description of operation.

Modified: 02.09.2013 15:09

12/18

TIE-50506 System design

Exercise 01

System specification

6. HARDWARE

This Chapter describes the hardware part that is synthesized on the FPGA.

6.1 Hardware architecture

TODO: Describe briefly the hardware used in the design.

Add hierarchical block diagrams created by the Kactus2 software [7] and explain different

hierarchy levels in detail. Describe the main parts of the HW and explain how to data flows

through the system.

Explain the clocking and reset.

Explain the I/O.

6.2 Hardware Files

TODO: Describe shortly all the hardware files that are used in the design. Document what

language they use.

6.3 Compilation/synthesis

TODO: Describe how HW is compiled and uploaded to FPGA.(Tip: See [8] and [9] ).

Modified: 02.09.2013 15:09

13/18

TIE-50506 System design

Exercise 01

System specification

7. IP BLOCKS

This Chapter includes detailed information of the IP-blocks used in the design. The IPs are

categorized as… (Tip: and explained in that order) (Note: In our case, these are ready made

and, hence, the description differs from SW part.)

7.1 Block X

TODO: Describe the block X in detail and explain for which purpose the component is added to the system, how it is connected to the rest of the system, and all other relevant information.

Tip: Use e.g. 0.5 page per IP and cite external sources for further details.

Point out where this block is in the figure that describes the whole architecture.

7.1.1 Block Connections

TODO: Describe briefly how the IP-block is connected to the rest of the system, not necessarily at bit-level (as this is just exercise work).

7.1.2 Dependencies

TODO: If IP-block requires additional IP-blocks/ICs in order to work add them here together

with brief description why they are needed. Similarly, describe which parts and vendorspecific or tied to certain FPGA board.

Modified: 02.09.2013 15:09

14/18

TIE-50506 System design

Exercise 01

System specification

8. IC

This Chapter includes detailed information of the ICs used in the design. The ICs are categorized as… (Tip: and explained in that order) (Note: In our case, these are ready made and,

hence, the description differs from SW part.)

8.1 ICs

TODO: Describe the IC X in detail and explain for which purpose the chip is added to the

system, how it is connected to the rest of the system, and all other relevant information.

Tip: Use e.g. 0.5 pages per IC and cite external sources for further details.

Point out where this IC is in the figure that describes the whole architecture.

8.1.1 IC Connections

TODO: Describe briefly how the chip is connected to the rest of the system, not necessarily

at bit-level (as this is just exercise work).

8.1.2 Dependencies

TODO: If chip additional IP-blocks/ICs in order to work add them here together with brief

description why they are needed.

Modified: 02.09.2013 15:09

15/18

TIE-50506 System design

Exercise 01

System specification

9. FURTHER DEVELOPMENT

TODO: Add some additional thoughts how the design could be improved. E.g. Addition of

the VGA module to handle the display instead of the 7-segment display. Or you could speculate what is needed to port this application in to different environment (FPGA, CPU, OS)

etc.)

Tip: Use <1 page

References

TODO: Add references here. The order is either the citation order or alphabetical according

to the family name of the first author

Each entry consists of authors’ names (if known), title, version number, publisher/ a place

where the reader can find the reference, date, and cited/total number of pages. References

could include for example DE2 reference manual, eCos user manual etc…

[1]

Lauri Matilainen, TIE-50506 System design course web page, Department of Pervasive computing, Jun 2013, [Online], Available: http://www.tkt.cs.tut.fi/kurssit/50506/,

Accessed June 28, 2013

[2]

Jussi Raasakka, TKT-2431 SoC Design course web page, Department of Computer

Systems, Jan 2011, [Online], Available: http://www.tkt.cs.tut.fi/kurssit/2431/, Accessed January 09, 2013

[3]

DE2 Development and Education Board User Manual, Version 1.4, Altera Corporation,

2006,

[Online],

Available:

ftp://ftp.altera.com/up/pub/Webdocs/DE2_UserManual.pdf, Accessed March 28, 2011

[4]

Daniel D. Gajski, Embedded System Design Modeling, Synthesis and Verification

Available: http://link.springer.com/book/10.1007/978-1-4419-0504-8/page/1, Accessed January 11, 2013

[5]

Overview of the Hardware Abstraction Layer, Version 11.0.0, Altera Corporation,

2011,

[Online],

Available

http://www.altera.com/literature/hb/nios2/n2sw_nii52003.pdf, accessed Jan 11, 2012

[6]

NiosII Command-Line Tools, Version 2.2, Altera Corporation 2011, [Online], Available: http://www.altera.com/literature/hb/nios2/edh_ed51004.pdf, Accessed Jan 11,

2012

[7]

Kactus2 homepage, Department of Computer Systems, Oct 2011, [Online], Available :

http://funbase.cs.tut.fi/index.php/Kactus2, accessed Jan 11, 2012

Modified: 02.09.2013 15:09

16/18

TIE-50506 System design

Exercise 01

System specification

[8]

Quartus II Integrated Synthesis, Version 11.1.0, Altera Corporation, 2011, [Online],

Available http://www.altera.com/literature/hb/qts/qts_qii51008.pdf, accessed Jan 11,

2012

[9]

Quartus II Programmer, Version 11.1.0, Altera Corporation, 2011, [Online], Available

http://www.altera.com/literature/hb/qts/qts_qii53022.pdf, accessed Jan 11, 2012

Modified: 02.09.2013 15:09

17/18

TIE-50506 System design

Exercise 01

System specification

Appendices

Modified: 02.09.2013 15:09

18/18