(ms-word).

advertisement

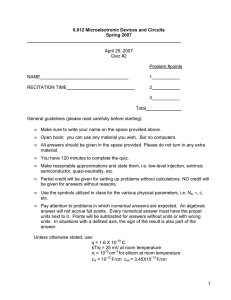

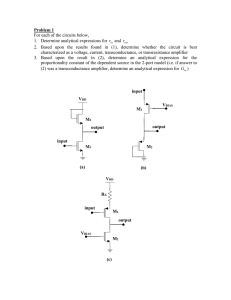

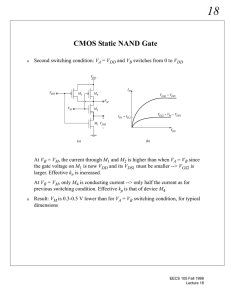

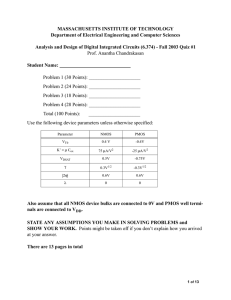

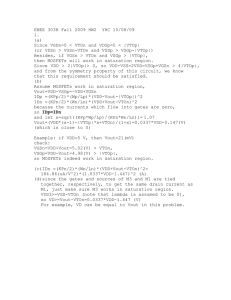

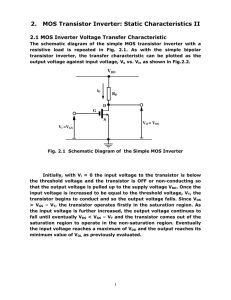

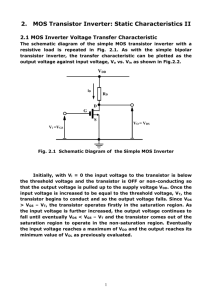

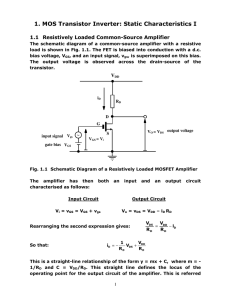

SOLUTION EE 141 Fall 1999 Homework Set #4 Due Wed. Oct 6 1999, 5.00 pm Problem 1) a) Pav = 1.25 mW refer eqn. 3.42 of textbook b) With lower voltages one would expect power to drop. But with increasing frequency the power becomes greater than the original power at a period of 5ns. Problem 2) a) VOH = Vdd VOL = 0.9 using eqn 4.11 of textbook b) 0 static power dissipation when Vin is low. When Vin is high Pav = 3.2 mW from eqn 4.13 of textbook c) In this problem tpLH = 0.69 RL CL tpHL = 0.69 (RL || RPDN ) CL RL is the load resistance. RPDN is the resistance of the pull down network. RL = ½[(Vds/Id)vout=vol + (Vds/Id)vout = vdd/2] = ½ [(Vdd – Vol) / ((Kp/2) (Vdd -|Vtp|)2) + (Vdd/2) /((Kp/2)((Vdd-Vt)Vdd – Vdd2 /4))] = 10951 RPDN = ½[(Vds/Id)vout=vdd + (Vds/Id)vout = vdd/2] = ½ [Vdd / ((Kn/2) (Vdd -Vtn)2) + (Vdd/2) /((Kn/2)((Vdd-Vt)Vdd/2 – Vdd2/4))] = 9791 tpLH = .3778 ns tpHL = .1783 ns d) higher. Lambda,p > Lambda,n. So if effect of channel modulation is included, it is likely that Isd,p > Isd,n. So Vol has to move higher to make |Vds,p| smaller and |Vds,n| bigger. Problem 3) If you solved all the parts of the problem assuming a short channel device that is ok. The grader will be notified. For this problem use table 3.5 and 3.6 a) S= 3.5 New speed is 1225 Mhz Power is 35 W. (with short channel- speed= 1.225 Ghz, power = Same) b) with U= 3.5 and S= 3.5 Speed = 350 Mhz Power = 0.816 W (With short channel Speed = 350Mhz, power = 0.816 W) c) consider general scaling Pav = 1= S/U3 U3 = 3.5 Vdd= 3.5/U = 2.3V d) There is no change in power consumed in constant voltage scaling for short channel devices Problem 4) a) tw = 0.38 r c L2 = 0.38 (10000)2 (0.08/3.6) (3.6 * 0.03 + 0.04 *2) = 0.158 ns b) - We have to find Cout as seen by the second buffer Output cap of the 2nd stage is approx by Ctotal. The problem then becomes We want to set u = ((Ctotal) / Ci)1/2 Total delay is tp0 u + tp0 u + tw u = 13.7 Problem 5) a) ((A+C)(B+D)F(A+E+D)(B+E+C))’ b) c) There is no common Euler path. Therefore no existing solution such that the PMOS network can be laid out in one contiguous strip. d)