Layer

advertisement

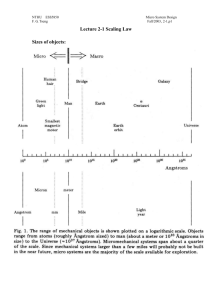

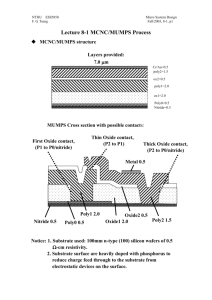

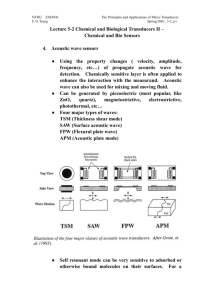

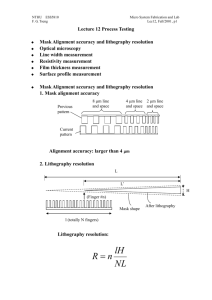

NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p1 Lecture 6-1 MEMS Design Through Foundries What is a foundry? Foundry: a fabrication service provider. We provide designs to the foundry service. The foundry fabricates the device for us. The fabrication process is usually fixed. The service providers do not need to have facilities. They either fabricate devices themselves or negotiate with other service provider for fabrication service. Advantages: 1. We do not need to spend capital for expensive fabrication facilities. 2. Good for small volume (typically 10-20 chips) 3. Fast for prototype (turn around time ~3-6 months) 4. We do not need to worry about the design of fabrication processes and the yield of the process, because experts have taken care of all the fabrication issues. The design variables can be minimized. Disadvantages: 1. Fabrication process is not flexible for wild experiments. 2. Materials are always limited. 3. Device geometries are tightly constrained by the provided process. 4. Post process is sometimes limited and difficult. 5. Limited for certain types of devices. IC and MEMS foundry: IC foundry is more mature than MEMS one, for fewer variations. NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p2 MEMS Foundries: 1. MOSIS/Orbit (Supertex), HP…, under USC/ISI: using CMOS process plus post-process. MOSIS: MOS Implementation Service. ~$10,000/cm2 Layers provided: 5.73 m 3.58 m 3.18 m over glass=1 met2=1.15 ox2=0.65 o-g met1=0.6 ox2 ox1=0.85 poly2=0.4 poly ox1=0.08 Poly=0.4 fox=0.85 ox1 fox CMOS Cross Section: MEMS on CMOS chip examples: Micro cantilever beam [1] Micro flow sensor[1] NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p3 2. MCNC/MUMPS (Muti-User MEMS Process, now spun-off as Cronos Integrated Microsystems, Inc.), research triangle, NCSU: surface micromachining using 3 layers of polysilicon. ~$3500/cm2 Layers provided: 7.0 m Cr/Au=0.5 poly2=1.5 ox2=0.5 poly1=2.0 ox1=2.0 Nitride=0.5 Poly0=0.5 MUMPS Cross section with possible contacts: MUMPS examples: Micro Motor (MCNC/MUMPS) NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p4 3. MCNC/LIGA, LIGA process from U of Wisconsin: one layer of thick Ni structure with sacrificial/seed layer of Ti/Cu/Ti. Thick one: 200 um, width minimum 20 um, 10 to 1 length to width aspect ratio. Thin one, 30 um thick, 5 um feature, ~$500/cm2 30 or 200 m Nickel, 30 or 200 m Thin sacrificial metals, Ti /Cu/Ti Micro gears (Henry Guckel) 4. MCNC/Deep Silicon RIE: aspect ratio~ 10, vertical wall. ~$3000/3 wafers Micro bar (F. G. Tseng) NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p5 MEMS Design using MOSIS/SCNA process 1. Advantages: Integrating MEMS with IC directly Process simple, usually using one releasing procedure to obtain MEMS structure No extra mask required Mature process, low risk 2. Disadvantages Geometry limited Material limited Layer thickness not flexible at all Extra process with high temp prohibited Sensitivity to the chemical for bulk etching Process is expansive for small area 3. MOSFET a. Structure Gate Source Body Drain NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p6 D D G G S S NMOS PMOS Vdd S G P D IN OUT N G S Vss CMOS Inverter b. nMOS operational Principle Basically ID is controlled by VGS and VDS Cut off: VGS Vth : Channel is not estabilished => ID~0 Vth: throshold voltage Active: i. Triode region: VGS ,t 0 and VDS VGS ,t Here VGS , t VGS Vth => I D n 2 2 [2(VGS Vth )VDS VDS ] NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p7 n Kn W 2 L : Device transconductance, Amp/Volts K n nCox n ox X ox : Process transconductance n: electron mobility, Cox: oxide capacitance ii. Saturation region VDS VGS ,t n 1 2 I ( V V ) [ 1 (VDS VGS ,t )] GS th => D 2 VA VA range 30-200 Volts. ID Saturation Triode VGS -VA VDS I-V curve of n-channel MOSFET NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p8 c. Examples for MOSFET layout (NMOS, PMOS, parallel connection) Parallel connection of 2 N-MOS NTHU ESS5850 F. G. Tseng d. Layout process of a CMOS Micro System Design Fall/2003, 6-1, p9 NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p10 4. CMOS Detail process flow vs. layer names NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p11 NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p12 MOSIS/SCNA process layer names Layer Dep/Diff Contact Active Si3N4 Field ox wet ox N well Cif name GDS II # Color (L.) Protect act CAA 43 Green fill n CWN 42 Tan box N select n+ CSN 45 Grey box P select p+ CSP 44 Blue box Gate ox Dry ox Poly poly CPG 46 Red fill Poly ox ox Poly2 poly CEL 56 Tan fill Ox 1 CVD ox Poly cont. M1 to p CCP 55 Black fill Poly2 cont. M1 to P2 CCE 48 Black fill Active cont M1 to Act CCA 47 Black fill CMF 49 Blue fill CVA 50 White fill 51 Grey fill Metal 1 Al Ox 2 CVD ox Via M2 to M1 Metal 2 Al CMS Pad Define pad XP Over glass Out To M2 COG Pruple 52 Purple cro. NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p13 NOTE: 1. pit=CAA+CCA+CVA+COG 2. There is around 20% overetching for etching process 5. Design rules for MOSIS/SCAN 2.0 General: Layer poly Met1 Met2 active P,n select to well contact Pad Pad to metal b. Pit Line size () 2 3 3 3 5 2*2 (exact value) 100 10 20 Space () 2 3 4 3 2 50 Details: please check [2] (chapt 3) and [3] for detail information. 6. Methods for Fabricating MEMS device on CMOS chip Methods for Bulk micromachining to “release” MEMS structure on CMOS chip: 1. Bulk etching by EDP, TMAH 2. Bulk Etching by gas type etchant: XeF2 3. SCREAM process—Deep silicon RIE+ side wall protection + bottom under cut Methods for surface micromachining to “add” MEMS structure on CMOS chip: 1. Low temp process—metal, PR, LTO, etc… 2. Electro plating Metal layer--EFAB NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p14 7. Layout examples : MOS Inverter and Micro Fan. References: 1. M. Parameswaran, Lj. Ristic, K. Chau, A. M. Robinson, and W. Allegretto, “CMOS Electrothermal Microactuators”, IEEE MEMS’90, pp128-131, 1990 2. CMOS 實體層設計-使用 L-EDIT, Uyemura 著, 楊忠煌譯, 高立出版社, 1998. 3. http://www.mosis.org/Technical/Designrules/scmos/#tech-codes, for MOSIS/SCMOS design rules. (Using SCNA 2.0 m process) NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p15 HW#4 (Due 11/7 Wed) Please put the answers of 1(a)-(d), 4(a)-(d) into a .tdb file, with the file name: hw4+your student#.tdb. For example: hw4g883145.tdb. Mail this file to my email address fangang@ess.nthu.edu.tw before the due with a subject of the file name. 1. Review L-edit layout tools. Draw the following components fitting the MOSIS/SCNA 2.0 m process design rules: (a) A nMOS FET in one cell, name the cell “NMOS”, with W/L=10, minimum line width for all layers. (b) A pMOS FET in the other cell, name the cell “PMOS”, with W/L=20, minimum line width for all layers. (c) Draw a standard bonding pad in another cell, name the cell “PAD”, with metal2, Pad command, and overglass. After you have the above cells, try to finish the following: (d) Instance all these three cells into the ground cell, named “MST-HW4-1”, and connect them together to form a inverter with four pads. Label the four pads with either one of Vdd, Vss, Vin, and Vout. (e) Try to squeeze the whole device into a area as small as possible. Draw a rectangle which can just include the whole device. What is the size of the rectangle you get? 2. Find the following material properties: (a) The density of Al, SiO2, Si, poly Si, (b) The average sheet resistance and contact resistance of poly, poly2, Metal 1, metal 2 in MOSIS/SCNA 2.0 m process. (check lecture 6-1 reference [2] and [3]) (c) The thermal expansion coefficient of SiO2, Si, and Al. 3. In the CMOS process, there are essentially three different kinds of materials: silicon, silicon dioxides, and aluminum metalization. In general, the etch for one material is designed to stop on only one of the other two materials. The polysilicon etch, for example, is designed to stop on silicon dioxide, and not on aluminum. (a) Fill in the table 3 (a) below, indicating the layer that each etch typically stops on, what material the etch should be select to (i.e., not etch), and what material the etch is not likely to be selective to. (b) Assume that all etch steps have perfect selectivity (no etching) to the layer NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p16 that they are intended to stop on, and that they etch all other materials at the same rate. Assume that all etch steps use a 100% overetch. Please draw the 5 cross sections (from A-A’ to E-E’) indicated in fig. 3(a) with layer names and dimensions. Table 3(a) CIF Etch material Stop on layer Selective to material Not selective to material CPG (Poly)silicon Gate oxide Silicon dioxide aluminum CCA CMF CVA CMS COG PIT A’ A CPG B’ B CMF C’ C CMS D’ D CPG CMF E’ E Fig. 3 (a) NTHU ESS5850 F. G. Tseng Micro System Design Fall/2003, 6-1, p17 4. Design a hot plate flow sensor with on-chip current sources to run the sensor in constant temperature mode. (a) Design an thermally isolated polysilicon resistor based sensor similar to the one shown in fig. 4a. into a cell named “SENSOR”. The polysilicon sensor should have resistance of approximately 1 k. (b) Design a reference resistor with a resistance 10% greater than the resistance of your sensor resistor into a cell named “REF” (c) Design a matched pair of PMOS transistors with a of 1 mA/V2 (assume k=10 A/V2) into a cell named “PMOS FOR SENSOR”. What is the W/L ratio of your design? (d) Integrate the elements together into a cell named “MST-HW4-4” to form a constant temperature circuit, as shown in Fig. 4b. Please put on bonding pads for all possible joints for future testing. (e) Estimate the excepted operation temperature of the sensor. (hint: TCR, R 1 Temperature Coefficient of Resistance , R: resistance, T: R0 T Temperature, TCR for polysilicon in CMOS process1.23e-3 1/C) Vdd Met1 Pit Vbias Vsensor Poly Vref R(T) Rref GND Fig. 4 (a) Fig. 4 (b)