Abstract - Electrical & Computer Engineering

advertisement

Design of Capacitive Displacement

Sensors for Nanoalingment

A Thesis Presented

by

Jose Luis Medina

To

The Department of Electrical and

Computer Engineering

in partial fulfillment of the requirements

for the degree of

Master of Science

in the field of

Electrical and Computer Engineering

Northeastern University

Boston, Massachusetts

December 17, 2007

ABSTRACT

Nanotechnology is a very promising technology that could potentially have a great

impact in fields such as medicine, electronics, material science, and energy storage.

Improvements in microscopy, as the invention of the Scanning Tunneling Microscope in

1981 and the Atomic Force Microscope in 1986, enabled the observation of molecules at

nanoscale and helped obtain a better understanding of the extraordinary dominant effects

at nanoscale, and later enabled the manipulation of single atoms or molecules.

Furthermore, the discovery of carbon nanotubes brought a novel material with excellent

properties at nanoscale. Fabrication of nanodevices is already a reality. However, in order

for this technology to become cost-effective and available for society, scalable fabrication

processes that would enable massive production of nanodevices must be developed.

Towards this goal, the ‘Center for High Rate Nanomanufacturing’ is developing a

scalable nanomanufacturing process flow based on transferring nanoelements from a

template to a substrate.

For one of the step of this process flow, a alignment of template and substrate at

nanoscale is required. This work aims at designing a capacitive displacement sensor for

alignment of two chips or wafers. First, the alignment process is analyzed and different

sensing techniques studied in relation to this specific project. After that, modeling and

analysis of the sensor is carried out, followed by the design of the sensor, including its

readout circuit.

ii

ACKNOWLEDGMENTS

From my experience studying and researching in several institutions in three different

countries, I know usually advisors care more about the final goals of the project than

about the students who are doing that research. I would specially like to thank professor

McGruer for, not only giving me the opportunity to work with him on this project, but

also for his interest in my academic and personal development, in addition to my research.

I appreciate his guidance through my studies at Northeastern and beginning of my career.

I also want to thank professors George Adams, Demetrios Papageorgiou, Ahmed

Busnaina, Sun, and Sinan Muftu for their help and guidance during my thesis.

In the Northeastern Microfabrication Lab, I want to thank the students Prashanth

Makaram, Andy Pamp, Peter Ryan, Juan Aceros, and Siva Somu for helping with the

tools and equipment in the lab. I also want to thank Jen Dawson, for copyediting my

thesis, and for so much more.

iii

TABLE OF CONTENTS

Abstract

Acknowledgments

ii

iii

1. Introduction

1.1 Nanotechnology and Nanomanufacturing

1.2 Alignment and Nanopositioning

1.3 Displacement Sensors

1.4 Sensor requirements

1.5 Comparison sensors literature and nanoaligner sensor

1

1

2

3

5

2. Sensor design

2.1 Arrangement for connections-free substrate

2.2 Arrangement for large gap variations

2.2.1 Fractal arrangement

2.2.2 Switchable variable width

2.2.3 Central fractal

2.3 Fabrication

8

10

10

12

14

15

3. Modeling

3.1 Capacitance and FEM field solvers

3.2 Modeling scenarios

3.3 Equivalent capacitance circuit

3.4 FEM simulations

3.4.1 Algorithm

3.4.2 Fringing field effect

3.4.3 Influence of plate conductivity

3.5 Convergence

17

22

24

27

27

28

32

45

4. Capacitance-to-voltage converter

4.1 Introduction

4.2 Converters

4.3 Oscillators

4.4 Capacitive Bridge

4.5 Transimpedance amplifier

4.5.1 Gain and noise

4.5.2 Stability

4.5.3 Demodulator

4.6 Switched-Capacitor Converter

4.6.1 Switched-Capacitor Amplifier

4.6.2 Parasitic Capacitance

4.6.3 Correlated Double Sampling

49

50

51

52

52

52

55

59

60

60

63

64

iv

4.6.4 Bandwidth

4.6.5 Noise Analysis

4.6.6 Simulations

4.7 Sigma-Delta modulator

68

70

73

76

5. Experimental verification

5.1 Scaled model

5.2 Setup

5.3 Readout circuit

5.4 Designs tested

5.4.1 Large features test board

5.4.2 Central fractal test board

81

84

85

86

87

90

6. Conclusions and future work

6.1 Experimental results

6.2 Recommendations for design

6.3 Future work

93

95

97

Appendices

A. Calculation of equivalent output capacitance

B. APDL macro for capacitance extraction simplified model table 3.2

C. APDL macro model for large gap and displacement range table

D. MATLAB filter for ANSYS capacitance results

E. APDL macro to calculate capacitance versus number of nodes per

electrode’s horizontal surface

F. Input equivalent capacitance for connected plates.

G. Hspice code readout circuit Figure 4.24 and RC LPF

v

101

vi

1. Introduction

1.1 Nanotechnology and Nanomanufacturing

Nanotechnology can be defined as the engineering of functional systems at nanometer

scale, i.e. at the molecular scale. Currently there is technology available that enables

manipulation single molecules and building of nanodevices [1.5]. However, in order for

nanotechnology to become commercially available for the general public, instead or

manipulating single molecules at a time, billions of molecules have to be manipulated at

a time. A scalable nanomanufacturing process that would enable the fabrication of

nanodevices at high rates is one of the main keys towards the commercialization of

nanotechnology.

1.2 Alignment and Nanopositioning

Towards the successful commercialization of nanotechnology, the ‘Center for High Rate

Nanomanufacturing’ (CHN) aims to develop a process flow that would enable scalable

fabrication of nanodevices. A novel process studied at this center involves the transfer of

nanotubes and or nanoparticles from a template to a substrate. In order for the transfer to

be successful, an extraordinarily accurate alignment between substrate plate and template

plate must be achieved. This alignment would have two phases. A first phase would align

the plates up to a few nanometers by means of a displacement sensor. A nanopositioner,

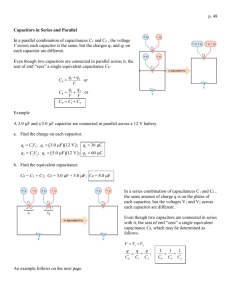

like the one in Figure 1.1, would be used to move the plates, while a displacement sensor

1

would sense the relative position and close the feedback loop. The nanopositioner would

move one of the plates, while the other one would remain static.

Figure 1.1: Model of nanopositioner used for high rate nanomanufacturing [1.6].

Then, the second phase of the alignment would take over, where molecular forces of

chemical and physical nature would further align the plates. Once alignment is achieved,

the nanotubes or nanoparticles would be transferred from template to substrate.

1.3 Displacement Sensors

Displacement sensors are widely used in industry. Most displacement sensors are based

on transducers that convert displacement to another signal such as temperature, light, or

electrical resistance. The main transducer principles are given in the following table.

Criteria

Probe-based

Optical

Capacitive

Thermal

Accuracy

++

++

+/++

+/++

Range

-/+

++

+/++

+/++

Speed

+

+

+

Fabrication

-++

++

Electronics integration

+

++

++

Parasitic forces

-/+

++

--/+

Power consumption

+/++

-/+

++

+

Table 1.1: Main displacement sensor transducers that enable integration within a MEMS device, with

accuracy in the nm-range, and range over 100 μm [1.1].

Optical transducers achieve high accuracy, but are complex to fabricate and integrate.

Capacitive transducers are easier and inexpensive to fabricate, can easily be integrated in

2

any system, and do not need complicated electronics. On the other hand, capacitive

transducers are highly affected by any surrounding capacitances different from the

capacitance to be measured. Thermal transducers are simple and inexpensive as well,

although the measurement is slower.

1.4 Sensor requirements

To align two chips or wafers, a displacement sensor can be integrated in the chips to align,

so that the relative position of both chips can be sensed.

A displacement sensor for plate alignment must meet several characteristics from

fabrication and economics point of view. First, its fabrication should be compatible with

the nanomanufacturing process flow, and enable integration. Second, it must be flexible

and compatible with general nanopositioner equipment. Third, it should be as

inexpensive and robust as possible. A probe-based converter may not be compatible with

the alignment process and nanopositioner. An optical transducer would require a complex

circuitry to obtain an electrical signal for the feedback. A thermal actuator may be too

slow, which would require a more complex controller for the feedback and may result in

instability. A capacitive transducer is easy to integrate in the feedback loop with rather

simple circuitry, and inexpensive to fabricate. Furthermore, built-in capacitive sensors

can easily be fabricated on top of the same plates to align, which results in easier

integration in the alignment process and compatibility with the nanopositioner. For all

these reasons, capacitive transducers are used for this project’s purposes.

As illustrated in the following figure, a group of metal strips can be fabricated on the

chips to align, in a way that the capacitance between the strips in the substrate and the

3

strips in the template would depend on the relative position of the plates. Four

independent sensors are incorporated on both plates, two sensors oriented in one direction

and the other two perpendicular. In principle, these four sensors should be able to

determine the relative position of both plates in six degrees of freedom.

Figure 1.2: substrate and template plates (grey) with built-in electrodes (yellow) for capacitive sensing.

Figure 1.3 shows the strips on substrate and template.

Figure 1.3: Detail of substrate and template strips. The figure on the left shows the

pads for external connections.

The main drawback of this approach is the parasitic capacitances in the sensor, which

deteriorates the sensor performance. Care should be taken in the design of the electronic

readout circuit to minimize the influence of parasitic capacitances.

4

1.5 Comparison sensors literature and nanoaligner sensor

There is extensive research literature in the field of micromachined capacitive sensors for

applications such as Bioengineering [1.2], positioners [1.3], temperature and humidity

sensor [1.7], and automotive [1.4]. Most of these sensors are based on two parallel

electrodes, where the overlapping area of the electrodes changes with the lateral

displacement of the plates, while the gap remains constant.

Figure 1.4: Schematic model of a capacitive position sensor [1.2].

Humidity and temperature capacitive sensors have fixed electrodes, so the structure

usually used for these sensors is quite different from the structure needed for alignment

with a nanoaligner [1.7]. Something common in all displacement sensors reviewed during

the literature research done is that in all sensors only one dimension varies, while the

other dimension is meant to stay as constant as possible. Indeed, in most displacement

sensors, the gap between the electrodes is kept constant, while the overlap electrode area

changes with displacement. The sensor in Figure 1.4 follows such approach. Typically

capacitive sensors are based on the capacitance from the strips on one plate to the strips

on the other plate.

5

~

Figure 1.5: typical scheme used in capacitive displacement sensors. The top strips and the bottom strips are

attached to two different plates. An excitation is applied to the strips on one plate, while the strips on the

other plate are connected to a readout circuit. The gap remains constant, while the plates move laterally in

parallel to each other. The sensor detects the relative plate displacement.

Unlike these sensors, a sensor aimed at alignment with a nanopositioner like the one

shown in Figure 1.1 would have two novel main requirements. First, in order for the

nanopositioner to move one of the plates, this plate must be free of connections.

Therefore all the connections to a readout circuit have to be done to the static plate. This

means that a scheme such as the one in Figure 1.5 cannot be used, since this scheme

requires connections to both top and bottom plates.

Second, capacitive sensors are usually designed to work under either a constant gap or an

overlapping area constant. In this way the electrode geometry can be optimized for given

range. However, in this project it will be assumed that the nanopositioner starts the

alignment at a long gap. Once the best possible alignment is achieved at that gap, the gap

is decreased, so the sensitivity of capacitance to displacement increases, and a new finer

realignment can be achieved. This process is repeated several times until the minimum

gap before contact is reached. As a first assumption, the gap at the beginning of

alignment process would be 0.5 mm, while the last smallest gap could be as short as 50

nm. A widely variable gap introduces an important issue to overcome in the sensor

6

design. Parallel plate capacitors such as the ones shown in Figure 1.5 become insensitive

to lateral displacement if the ratio of strip width to gap is large. A large number of strips

with small width would give high sensitivity for small gaps, but it would be almost

insensible to lateral displacement for long gaps. However, a smaller number of strips with

larger width would result in greater sensitivity for large gaps, but less sensitivity for small

gaps. Potential solutions and trade-offs to this issue, such as fractal geometries with sets

of electrodes with different width, will be addressed during the sensor design.

References:

[1.1] A. A. Kuijpers, ‘Micromachined Capacitive Ling-Range Displacement Sensor for

Nano-positioning of Microactuator Systems’, PhD thesis, Universiteit Twente.

[1.2] A. Pedrocchi, S. Hoen, G. Ferrignl, A. Pedotti, ‘Perspectives on MEMS in

Bioengineering: A Novel Capacitive Position Microsensor’, IEEE Vol. 47, No. 1, January

2000

[1.3] H. U. Meyer, ‘An Integrated Capacitive Position Sensor’, IEEE Vol. 45, No. 2,

April 1996

[1.4] G. Brasseur, B. Brandstatter, H. Zangl, ‘State of the Art of Robust Capacitive

Sensors’, IEEE 2003.

[1.5] A. Busnaina, ‘Nanomanufacturing Handbook’, Northeastern University, Boston,

CRC Press

[1.6] A. Busnaina, ’High-rate Directed Assembly of Nanoelements’. NSF presentation

[1.7] A. Tetelin, C. Pellet, ‘Modeling and Optimization of a Fast Response Capacitive

Humidity Sensor’, IEEE Sensors Journal, Vol. 6, No. 3, June 2006.

7

2. Sensor design

2.1 Arrangement for connections-free substrate

As explained before, the scheme of Figure 1.4 would be incompatible with the alignment

process, since the nanopositioner needs the moving plate to be free of connections.

Instead, a scheme such as the one shown in Figure 2.1 could be used.

Figure 2.1: scheme of capacitive sensor with connections (the black arrow on the left and the voltage

source on the right) on only one side and equivalent capacitances. The capacitance symbols represent the

main capacitances between electrodes.

In the scheme of Figure 2.1 the two bottom electrodes 1 and 2 would be attached to plate

4, while top electrode 3 would be attached to plate 5. As in Figure 1.5, several groups of

strips could be placed in parallel to increase the capacitance. The resulting capacitance

that the detection circuit would sense when connected to electrodes 1 and 2 neglecting

capacitances to plates 4 and 5 would be

Ctotal C12

C13C 23

C13 C 23

(2.1)

A scheme similar to the one in Figure 2.1 is used for differential capacitive sensors [2.1].

This is shown in the following figure.

8

Figure 2.2: differential capacitor. The figures show the bottom plate, the bottom electrodes and the top

electrodes. In the figure on the left, three electrode groups are set in parallel to increment the capacitance.

The figure on the right shows a simplified model of the capacitances [2.1].

The differential sensor of Figure 2.2 uses excitation applied at electrode 3 (the top

electrode), while electrodes 1 and 2 are connected to a differential amplifier. Figure 2.3

shows a differential readout circuit and the electrical signal through its stages when there

is a displacement [2.2].

Figure 2.3: differential capacitor sensor and readout circuit [2.2]. The circuit is based on a differential

transimpedance amplifier as explained in section 4.5.

The circuit of Figure 2.3 models the sensor capacitance C1 and C2 of Figure 2.2 as an

initial capacitance Cx0 plus an increment due to a lateral displacement. This increment is

the same in absolute value for both capacitances C1 and C2, but of opposite signs. The

output voltages are processed by the circuit independently and subtracted at a final stage.

9

Therefore the sensitivity of capacitance to displacement compared to single capacitive

sensors is twice as much. This scheme is useful for alignment if a connection to the plate

moved by the nanopositioner is possible. Otherwise, the scheme of Figure 2.1 should be

considered.

2.2 Arrangement for large gap variations

Capacitive sensors composed of parallel strips or plates as in Figure 1.4 are designed to

have a gap around 10 times smaller than the strip width. As will be shown in section 3.4.2,

larger gaps than one third of the width would give poor sensitivity of capacitance to

lateral displacement. Therefore, hypothetically, a parallel plate capacitor for lateral

displacement sensing would need to be optimized for a specific gap or a short range

around it. In the following sections several approaches are proposed to overcome this

issue. These approaches will be analyzed by means of a FEM simulator in Chapter 3.

2.2.1 Fractal arrangement

Fractals can be defined as geometrical objects that are self-similar under a change of

scale, for example, magnification [2.3]. In principle, the strips of a capacitor could be

arranged in fractal geometry, in a way that the different levels of the fractals would be

used for different gaps.

The simplest and first discovered fractal is the Cantor set [2.4]. This fractal is constructed

be deleting the open middle thirds of a set of line segments. The first step starts by

deleting the open middle third from the interval [0, 1], leaving two line segments:

[0, 1/3] , [2/3, 1]. Next, the open middle third of each of these remaining segments is

10

deleted. This process is continued ad infinitum. Figure 2.4 shows the first six steps of the

process [2.4].

Figure 2.4: From the top to the bottom, first six steps of Cantor set [2.4].

A capacitor arranged in such way would be expected to give peaks with displacement that

would be divided in several new peaks for shorter gaps. These new peaks would be again

divided in new peaks for even shorter gaps, and so on. Instead of dividing a line into

three segments, for the sensor design the line is divided in five segments, where the

second and fourth segment would be removed. The following figures show the process.

For small gaps, a couple of strips is used to sense lateral displacement.

Figure 2.5: first fractal level

When the gap increases, the association of the first level unit with the strips around it

takes over, sensing as it was one unit.

Figure 2.6: second fractal level

In a similar way, for longer gaps, three second level units form a larger unit, which gives

the third level.

11

Figure 2.7: third fractal level

And finally, for larger gaps, the fourth level takes over

Figure 2.8: fourth fractal level

For a three electrodes scheme as in Figure 2.1, hypothetically the fractal arrangement

could be implemented as well:

Figure 2.9: first fractal level

Figure 2.10: second fractal level

Figure 2.11: third fractal level

Figure 2.12: fourth fractal level

12

2.2.2 Switchable variable width

By connecting and disconnecting different strips, the sensor configuration can be changed

and adapted to the most convenient arrangement for a specific gap. With the threeelectrode configuration of Figure 2.1, for small gaps the electrodes can be arranged as in

Figure 2.13.

Figure 2.13: first level arrangement for short gaps. The colors represent the three groups of electrodes that

are connected.

For larger gaps, two consecutive plates can be grouped as one plate, obtaining a larger

plate, as shown in Figure 2.14.

Figure 2.14: second level arrangement for short gaps.

And further on, more consecutive plates can be grouped for larger gaps as in Figure 2.15

and Figure 2.16

13

Figure 2.15: third level arrangement for short gaps.

Figure 2.16: fourth level arrangement for short gaps.

The sensor configuration could be changed by means of switches that would connect the

different parts.

2.2.3 Central fractal

The central fractal geometry is meant to obtain high resolution for short gaps while still

using electrodes with large width. Starting with three groups, instead of continuing the

fractal in the three groups, only the central part is replaced by three identical parts. The

process can be repeated ad infinitum with the new three central parts.

The geometry starts with three identical parts as shown in Figure 2.17.

Figure 2.17: capacitor geometry arranged in three identical groups

Then the central part is replaced by three more parts as in Figure 2.18.

Figure 2.18: capacitor geometry of Figure 2.17 replacing the central group by three identical groups

14

And further on, the central part is replaced by three more parts as in Figure 2.19.

Figure 2.19: capacitor geometry of Figure 2.18 replacing the central group by three identical groups

To decrease the change in capacitance with the gap, the lateral groups could be

disconnected and left floating once the alignment at that level has been achieved and the

gap is reduced. This would probably increase the sensitivity of the sensor as well, since

the capacitance from the larger groups may overlap the changes in the smaller groups for

short gaps.

2.3 Fabrication

The fabrication of the capacitor sensor is rather simple, with a three steps process. First,

to isolate the chip substrate from the capacitor electrodes, a layer of oxide is grown.

Figure 2.20: first step fabrication process. Substrate (grey), silicon dioxide (brown)

Second, metal is deposited to form the electrodes. A thin layer of zinc is deposited,

followed by a layer of gold.

Figure 2.21: second step fabrication process. Deposition of Zn (green), and gold (yellow)

15

The third step is pattern of the metal. Photoresist is spunned on top, and exposed by

optical lithography.

Figure 2.22: clear mask for metal pattern. The green line delimits the section showed in following figures

Figure 2.23: chip section after exposure. From the bottom to the top: substrate (grey), oxide (brown), Zn

(green), gold (yellow), photoresist (blue).

Once the photoresist is exposed, the metal is etched, and the photoresist removed.

Figure 2.24: chip section

16

Reference:

[2.1] Z. Liu, Q. Huang, W. Li, ‘A differential Capacitive Mini-Displacement Sensor’,

Key Lab. Of MEMS of the Minist. Of Educ., Southeast Univ., Nanjing, China. Sensors,

2004. Proceedings of IEEE.

[2.2] J. C. Lotters, W. Olthuis, P. H Veltink, ‘A sensitive differential capacitance to

voltage converter for sensor applications’. IEEE Vol. 48, No. 1, February 1999

[2.3] McGraw-Hill Encyclopedia of Science and Technology. Copyright © 2005 by The

McGraw-Hill Companies, Inc.

[2.4] http://en.wikipedia.org/wiki/Cantor%27s_fractal_set

17

3. Modeling

3.1 Capacitance and FEM field solver

When a battery is connected to two isolated conductors, the battery extracts negative

charges, i.e. electrons, from one conductor to the other, until a determined difference of

potential is achieved. This is shown in Figure 3.1.

Conductor a

e-

+

+

+

+

+

+

+

+

Q

+

+

+ +

+

++++++++++++++++++++++++++++

E

Vs

e-

-

- - - - - - - - - - - - - - - - - - -Q

Conductor b

Figure 3.1: two conductors being charged by a battery

Capacitance is defined as the ratio of the charge stored to the voltage applied.

C

Q

Vs

(3.1)

The capacitance of a system only depends upon the geometry of its elements and the

material properties of the surrounding medium. The capacitance of simplified models,

such as uniformly charged parallel plate capacitor, can be obtained analytically by

resolving Maxwell’s equations. Although analytical solutions to more complex

geometries are sometimes available in transmission line and microstrips theory literature

[3.1]-[3.4], numerical methods are needed to obtain accurate solutions for systems

composed by more than two electrodes.

18

Finite Element simulations calculate ground capacitance, which relates the charge on

each conductor with the conductor’s voltage drop to ground [3.5]. The following figure

illustrates a system with four conductors, where the fourth one is ground.

Figure 3.2: Multielectrode system with three conductors and ground

The ground capacitances are given by Eqns. 3.2-3.4

Q1=Cg11U1+Cg12U2+Cg13U3

(3.2)

Q2=Cg21U1+Cg22U2+Cg23U3

(3.3)

Q3=Cg31U1+Cg32U2+Cg33U3

(3.4)

Where Ui is the potential of conductor i, Qi is the charge of conductor i, and Cgij is the

ground capacitance of electrode i to electrode j. A matrix of ground capacitance is

defined from the coefficients of Eqns. 3.2-3.4

C g11 C g12

C g C g 21 C g 22

C g 31 C g 32

C g13

C g 23

C g 33

(3.5)

For a linear system Cgij=Cgji, and therefore Cg becomes symmetric. Because ground

capacitance does not relate the capacitance between conductors, circuit simulators such as

Spice use lumped element capacitance models. A lumped model is defined as a model in

which the dependant variables of interest are function of time only, as opposed to

19

distributed models, whose variables are function of time and more spatial variables [3.6].

The lumped circuit model of the system of Figure 3.2 is shown in Figure 3.3.

Figure 3.3: Lumped capacitor equivalence of four conductor system

The lumped matrix capacitance is extracted from the ground capacitance equations.

Q1=(Cg11+Cg12+Cg13)(U1-0)+(-C12)(U1-U2)+ (-C13)(U1-U3)=Cl11U1+Cl12(U1-U2) +Cl13(U1-U3)

Q2=(-C21)(U2-U1)+ (Cg21+Cg22+Cg23)(U2-0)+ (-C23)(U2-U3)=Cl21(U2-U1)+Cl22U2 +Cl23(U2-U3)

Q3= (-C31)(U3-U1)+ (-C32)(U3-U2)+ (Cg31+Cg32+Cg33)(U3-0)=Cl31(U3-U1)+Cl32(U3-U2)+Cl33U3

(3.6), (3.7), (3.8)

The lumped matrix capacitance is therefore obtained from the ground capacitance with

the following relation.

C g11 C g12 C g13

C g12

C g13

Cl

C g12

C g12 C g 22 C g 23

C g 23

C

C

C

C

C

g 13

g 23

g 13

g 23

g 33

(3.9)

To illustrate an example of matrix capacitance, the results from a capacitance extraction

simulation of a five electrode system with ANSYS are shown below

20

________________ CMATRIX SOLUTION SUMMARY ___________________

*** Ground Capacitance Matrix ***

Self Capacitance of conductor 1. =

Self Capacitance of conductor 2. =

Self Capacitance of conductor 3. =

Self Capacitance of conductor 4. =

Self Capacitance of conductor 5. =

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Ground capacitance matrix is stored in

*** Lumped Capacitance Matrix ***

Self Capacitance of conductor 1. =

Self Capacitance of conductor 2. =

Self Capacitance of conductor 3. =

Self Capacitance of conductor 4. =

Self Capacitance of conductor 5. =

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Mutual Capacitance between conductors

Lumped capacitance matrix is stored in

0.30142E-03

0.30118E-03

0.54565E-03

0.35634E-02

0.35719E-02

1. and 2. =

-0.45432E-06

1. and 3. =

-0.19700E-03

1. and 4. =

-0.24790E-04

1. and 5. =

-0.79176E-04

2. and 3. =

-0.19686E-03

2. and 4. =

-0.24780E-04

2. and 5. =

-0.79081E-04

3. and 4. =

-0.12600E-03

3. and 5. =

-0.25787E-04

4. and 5. =

-0.33717E-02

3d array parameter cmatrix ( 5., 5.,1)

0.22795E-16

0.33339E-16

0.39858E-16

0.16123E-04

0.16122E-04

1. and 2. =

0.45432E-06

1. and 3. =

0.19700E-03

1. and 4. =

0.24790E-04

1. and 5. =

0.79176E-04

2. and 3. =

0.19686E-03

2. and 4. =

0.24780E-04

2. and 5. =

0.79081E-04

3. and 4. =

0.12600E-03

3. and 5. =

0.25787E-04

4. and 5. =

0.33717E-02

3d array parameter cmatrix ( 5., 5.,2)

Capacitance values are per unit length

Capacitance matricies are stored in file cmatrix .txt

_____________________________________________________________

Figure 3.4: capacitance extraction simulation output with ANSYS. The solution given by ANSYS includes

both the ground capacitance matrix from the simulations and the lumped capacitance matrix for a lumped

circuit model.

In order to obtain the matrix capacitance of a system, the following equation, known as

Gauss’s law, can be used.

Qi o r E (r )dAi

(3.10)

Ai

where Qi is the charge of electrode -i, E (r ) is the electric field at point r , εo and εr the

vacuum permittivity and medium relative permittivity, and Ai is the area of integration

around electrode -i. Due to numerical reasons, a more efficient way to calculate

capacitance is by using the principle of energy conservation [3.7].

21

W

2

1

1

o r (r ) E (r ) dV E (r ) D(r )dV

2 V

2V

(3.11)

Instead of using Eqn. (3.1), the following relation of energy and capacitance is used.

W

1

CU 2

2

(3.12)

Eqn. (3.12) is used to set up a system of equations that relates voltage differences to

energy stored.

C W

U1,12 2 U1,132 U1,14 2 U1, 232 U1, 24 2 U1,34 2 12 1

2

2

2

2

2

2 C13

W2

U 2,12 U 2,13 U 2,14 U 2, 23 U 2, 24 U 2,34 C W

1

14

3

.

.

.

.

W4

C23

2

.

.

U 2 U 2 U 2 U 2 U 2 U 2 C24 W5

6 ,13

6 ,14

6 , 23

6 , 24

6 , 34

6,12

C34 W6

(3.13)

Eqn (3.13) represents a system of 4 electrodes, which has 6 unknown capacitances. Even

though different electrode potentials would give a completely different electric field

distributions, the capacitance must remain the same because it is exclusively a geometric

and material factor. Using this principle, any electrode potential Uk,ij can be used as

boundary condition. Once the electric field is obtained for a particular boundary

condition, the energy is calculated with the numerical equivalent of Eqn. 3.11

Wk

1 l n

2

2

2

2

2

2

E xk ,l E yk ,l E zk ,l Dxk ,l D yk ,l Dzk ,l velem,l

2 l 1

(3.14)

The process is repeated until the number of required independent equations is obtained.

Once mutual capacitances are calculated, self capacitances can easily be calculated with

the following expression

Cii

22

n

C

j 1, j i

ij

(3.15)

It can easily be verified that the ground matrix capacitance given in the example above

matches Eqn. (3.15).

3.2 Modeling scenarios

In electrostatic, magnetic, and thermal domain, a system model can be classified as open

scenario or closed scenario [3.5]. A closed scenario is a model whose field is restricted to

a determined area by its boundary conditions.

Figure 3.4: Three conductor system modeled as closed scenario

On the other hand, an open scenario assumes that the field is not restricted and extends

indefinitely. An open scenario can be seen as a closed scenario with boundary conditions

at the infinity. There are three main approaches to model the far-field. The simplest one is

to assume a natural boundary condition that the field has to match. This is illustrated in

Figure 3.5.

Figure 3.5: Three conductor system. Natural boundary condition to model far-field

A more accurate approach to model far-fields is by defining Far-field elements around

the area to model, as illustrated in Figure 3.6

23

Figure 3.6: Three conductor system. Far-field elements (infinite elements) to model far-field

The most accurate approach, although restricted to 3D models, is to define a Trefftz

domain. This method models the far-field with hybrid infinite elements and Trefftz nodes.

This is illustrated in Figure 3.6.

Figure 3.6: Three conductor system. Trefftz method to model far-field

If the plates to align were conductive and could be connected to ground, a closed model

scenario could be used to simulate the system. However, for the most general case, no

connection to either plate is assumed. Therefore an open model scenario must be used.

Due to the large number of strips that compose the sensor, and the longitudinal

geometrical symmetry, 2D simulations are accurate and far more computationally

efficient. Thereby, infinite elements were used as modeling scenario for the project’s

sensor.

3.3 Equivalent circuit

In Figure 2.1 the capacitances between electrodes 1, 2, and 3 are illustrated. For the most

general case, however, the plates which will be aligned are conductors as well. This

24

means that the system is composed of 5 electrodes instead of 3, with mutual capacitances

from every electrode to every electrode.

Figure 3.7: Sensor capacitance model

The scheme of Figure 3.7 can be simplified to a circuit with lumped capacitances. This

circuit is shown in Figure 3.8.

Figure 3.8: Sensor equivalent circuit

The equivalent circuit of Figure 3.8 can be simplified to an equivalent input impedance

from nodes 1-2. To do so, a test voltage is applied between nodes 1 and 2. By applying

the loop-current method, the test current is obtained in function with the equivalent

impedance. In order to resolve a circuit with b branches and n nodes, b-n+1 equations are

sufficient to obtain the current through every branch [3.8]. The following figure shows

the six branches whose equations are to be obtained, and the current references.

25

Figure 3.9: Circuit graph with selected tree and branch current references

The selected branches are a, b, c, d, e, and f. The current in the remainder branches g, h, j,

and k can be obtained as a function of the selected branches.

ig=ia+ib+if

(3.16)

ih=ig -id -ie=ia+ib+if -id - ie

(3.17)

ij=if+ik-id=ib+ic+if -id -ie

(3.18)

ik=ib+ic –ie

(3.19)

Assuming an impedance Zij at every branch, and applying a test voltage in branch g, the

following circuit is obtained

Figure 3.10: Circuit to obtain equivalent impedance

To resolve the circuit, the current equations of the six fundamental branches are obtained

as in Table 3.1.

26

Loop

Branches

Equation

a

a, h, g

0=Z23 ia + Z13 ih - Vt

b

b, k, j, h, g

0=Z24 ib + Z45 ik – Z35 ij + Z13 ih -Vt

c

c, k, j

0=Z34 ic + Z45 ik – Z35 ij

d

d, h, j

0=Z15 id – Z13 ih + Z35 ij

e

e, h, j, k

0=Z14 ie – Z13 ih + Z35 ij –Z45 ik

f

f, j, h, g

0=Z25 if – Z35 ij + Z13 ih - Vt

Table 3.1: Fundamental branches, loops’ branches, and loop equations

Substituting the currents ig, ih, ij, and ik from Eqns. (3.16)-(3.19) into the equations in

Table 3.1, a system of six equations with six unknown currents is obtained. Calculated

the fundamental branch currents, the test current it is obtained with Eqn. (3.16). The

equivalent impedance is then calculated as,

Z equiv

it

Z12 .

Vt

(3.20)

To resolve the system of equations for generic capacitance Cij , the equations from Table

3.1 were implemented in MATLAB. The code and results are given in appendix A.

A first interesting result that can be extracted from the output capacitance expression is

the weight of every capacitance over the total output capacitance. This can be obtained as

the partial derivative of the output capacitance

Cout Cout (Cij Cij ) Cout (Cij )

Cij

Cij Cij

(3.21)

Table 3.2 shows the derivative of the output capacitance respect to each lumped

capacitance. The lumped capacitance values were extracted from one of the simulation of

Section 3.4.

27

Cij

Set up point [pF/μm]

dC/dCij

C12

3.8079e-5

1

C13

1.108e-5

0.2148

C14

7.677e-4

0.2488

C15

5.518e-4

0.2453

C23

7.263e-6

-0.2596

C24

7.692e-4

0.2444

C25

5.540e-4

0.2393

C34

9.059e-4

-0.0078

C35

1.265e-4

-0.0056

C45

0.2314

-3.01e-5

Table 3.2: Derivative of output capacitance respect to each lumped capacitance.

Results from one of the simulation of section 3.4. The capacitance between the two plates (C 45),

and from electrode 3 to both plates have almost no influence in the output capacitance

3.4 Simulations

3.4.1 Algorithm

A finite element simulation software (ANSYS), was used to model and simulate the

sensor. As illustrated in Figure 3.4, ANSYS calculates the matrix capacitance for a given

model. A model is defined basically by its geometry, material properties, element

properties, electrode’s nodes, and mesh. To obtain the sensor response to lateral

displacement, a series of simulations was performed, in which the plates' relative position

was varied. This resulted in vectors of capacitance and displacement, which can be

plotted as capacitance versus displacement. Once the lumped matrix capacitance is

obtained, the equivalent capacitance is calculated as explained in Section 3.1. This gives

the input equivalent capacitance that a readout circuit connected to the sensor would ‘see’.

Since a large number of simulations had to be carried out for every geometry to obtain

curves capacitance-displacement, macros in APDL language were written. The macro

28

codes for the simulations are given in different Appendices. The diagram in Figure 3.11

shows the algorithm on which the macros were based.

k=1

Plate displacement

δ=[δ1, …, δN]

k=k+1

δk

k = 1?

no

Remove model

yes

Define geometry

material properties

and element type

Define number of

nodes

Mesh

Set up external flag

and electrodes

solve

Store results Cijk

k=N?

no

yes

Cij=[Cij1,…,CijN]

Figure 3.11: Flow diagram of FEM simulations with ANSYS

29

3.4.2 Fringing field effect

The variation or sensitivity of capacitance per unit length to displacement with the

infinite parallel plate model can be calculated as the derivative of capacitance with

respect to lateral displacement. By using the well-known capacitance of infinite parallel

plates, the sensitivity is

dC d ( w x)

n

n

dx dx

g

g

(3.21)

where g is the gap, ε the air permittivity, w the electrode width, and n the number of

parallel capacitors. In actuality, the capacitance displacement sensitivity is lower than in

Eqn. 3.21 due to fringing field capacitance. Eqn. 3.21 does not take into account the

fringing field capacitance, which is much less sensitive to lateral displacement than the

ideal ‘overlap’ capacitance of Eqn. 3.21.

C real Cideal C fringing

nwL

C fringing

g

(3.22)

Figure 3.12 shows the variation of dimensionless capacitance to lateral displacement for

different gaps for a simple parallel plate geometry.

2 electrodes 1 um width capacitor

dimensionless capacitance

1

0.9

0.8

0.7

gap 0.1 um

gap 0.2 um

gap 0.3 um

gap 0.5um

gap 1 um

gap 2 um

gap 5 um

gap 10 um

gap 100 um

0.6

0.5

0.4

0.3

0.2

0.1

0.5

1

1.5

2

2.5

3

3.5

4

4.5

displacement [um]

Fig 3.12: Dimensionless capacitance ( C(x)/C(x=0)) versus displacement for different gaps. The system

modeled was two parallel plates of 1μm width and negligible thickness.

30

Figure 3.12 shows how capacitance becomes less sensitive to displacement for larger

gaps. Eqn. 3.21 does not hold for large gaps, in which case the fringing field capacitance

is no longer negligible. The percentage of fringing field capacitance to total capacitance

is shown in Figure 3.13 for different gaps.

Fig 3.13: Ratio of fringing field capacitance (Cnumerical-Canalytical) to total capacitance (Cnumerical).

Analytical capacitance is calculated with the ideal parallel plate capacitance equation. Numerical

capacitance is calculated with a FEM simulator and includes both the ideal term and fringing term

of Eqn. 3.22. The system modeled was two parallel plates of 1μm width and negligible thickness.

Although Figure 3.13 shows fringing field for the case of two electrodes capacitor of

Figure 1.4, the results can be extrapolated to the 3 electrode capacitor of Figure 2.1.

When capacitance is dominated by fringing field capacitance, the capacitance sensitivity

to lateral displacement becomes negligible because the fringing effect sensitivity to

lateral displacement is very low. This can be extracted from Figure 3.13 and Figure 3.12.

For 100 μm gap, Figure 3.13 shows that capacitance is mostly made of fringing field

effect. For the same gap, Figure 3.12 shows that this capacitance, which is basically

fringing field, has very little variation with lateral displacement.

According to Figure 3.13, if fringing fields want to be kept under 30% of the total field

when the plates are aligned, the ratio of gap to width should be in the order of 1/3. In this

way, a minimum capacitor displacement sensitivity is guaranteed.

31

3.4.3 Influence of plates conductivity

The influence of the plates’ conductivity was analyzed by using different models that

include the plates as conductors or dielectrics.

-Simplified model, 5 electrodes

To reduce the number of nodes and make the simulations more time efficient, simplified

models with just a small fraction of the plates and reduced number of strips were used.

Figures 3.14-3.16 show the FEM model.

Figure 3.14: FEM model of capacitive sensor

The outer ring with square elements encloses the infinite elements modeling the far-field.

The triangular elements model the surrounding medium, which is air. And the two white

squares are sections of bottom and top plate. Between the two plates, the thin area models

the sensor’s electrodes, air and oxide. Figures 3.15-3.16 focus on this area.

Figure 3.15: Space between plates from Figure 3.14

32

Figure 3.16: Zoom in figure 3.14 showing electrodes, gap air, oxide layers, and plates

Figure 3.16 shows a part of the two plates, the three electrodes that compose the basic

sensor unit, two meshed layers of oxide separating the electrodes and the plates, and the

meshed space between the plates. A description of the model’s geometry is summarized

in Table 3.3.

gap

electrode thickness

width bottom electrodes

width top electrode

thickness oxide layer

thickness Si substrate plates

width plate

spacing between two bottom electrodes

spacing bottom electrode different groups

electrode length

plate lenght

Number of groups

Electrodes per group

Total number of electrodes

0.1 μm

0.1 μm

1 μm

2 μm

0.5 μm

381 μm

500 μm

1 μm

3 μm

500 μm

15 mm

3

3 (2 bottom, 1 top)

9

Table 3.3: model geometry

By changing the relative position of bottom and top plate, the change of capacitance

matrix versus displacement is obtained. Figures 3.17-3.21 show the results obtained. The

code is given in Appendix B.

33

-3

3.5

capacitance simulations g=0.1 um

x 10

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

3

capacitance [pF/um]

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.17: Lumped mutual capacitances per unit length. The electrodes are numbered as in

Figure 2.1 and 3.7

As expected, the largest capacitance is C45, which is the capacitance between the two

plates. Figure 3.18 focuses on the other capacitances.

-4

capacitance simulations g=0.1 um

x 10

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

capacitance [pF/um]

3

2

1

0

-3

-2

-1

0

1

displacement [um]

2

3

Figure 3.18: Lumped mutual capacitances per unit length.

Figure 3.16 shows that the capacitances C13 and C23 change drastically with displacement.

Capacitance C12 can be neglected compared to C13 and C23, in agreement to an

assumption commonly used in differential capacitance sensors [2.1]. However, the rest of

capacitances are in the same order of C13 and C23 and must be taken into account.

Figures 3.19-3.25 show the total capacitance in picoFarads.

34

total capacitance one group g=0.1 um

60

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

capacitance [pF]

50

40

30

20

10

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.19: Lumped mutual capacitances.

total capacitance one group g=0.1 um

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

0.16

0.14

capacitance [pF]

0.12

0.1

0.08

0.06

0.04

0.02

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.20: Lumped mutual capacitances.

Plugging the values from the capacitance matrix in the expression of equivalent input

capacitance deduced in Appendix B, input capacitance versus displacement curves are

obtained. Figures 3.21-3.22 show these results.

35

total capacitance one group g=0.1um

c12

c13

c23

cout

0.16

0.14

capacitance [pF]

0.12

0.1

0.08

0.06

0.04

0.02

0

-3

-2

-1

0

1

displacement [um]

2

3

Figure 3.21: C12, C13, and C23 from the lumped matrix capacitance, and equivalent input capacitance (Cout).

total capacitance one group g=0.1um

c12

c13

c23

cout

0.075

0.07

capacitance [pF]

0.065

0.06

0.055

0.05

0.045

0.04

0.035

-3

-2

-1

0

1

displacement [um]

2

3

Figure 3.22: C13 and C23 from the lumped matrix capacitance, and equivalent input capacitance (Cout).

Scaling up the results obtained with the simplified model, results for a model in scale can

be obtained. Figures 3.23-3.25 show the result of the simplified model scaled-up by

assuming 15 mm x 15 mm plates, and 27 groups of strips, across the 500 μm sensor

width.

36

total capacitance 27 groups g=0.1 um

1400

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

1200

capacitance [pF]

1000

800

600

400

200

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.23: Lumped mutual capacitances.

total capacitance 27 groups g=0.1 um

4.5

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

4

capacitance [pF]

3.5

3

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

Figure 3.24: Lumped mutual capacitances.

total capacitance 27 groups g=0.1um

4.5

c12

c13

c23

cout

4

capacitance [pF]

3.5

3

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.25: C13 and C23 from the lumped matrix capacitance, and equivalent input capacitance (Cout).

37

-Model for large gap and displacement range, 5 electrodes

For larger gaps and displacement ranges, a more precise model was developed. This

model is summarized in Table 3.4.

gap

electrode thickness

width bottom electrodes

width top electrode

thickness oxide layer

thickness Si substrate plates

width plate

spacing between two bottom electrodes

spacing bottom electrode different level 1

spacing bottom electrode different level 2

spacing bottom electrode different level 3

electrode length

plate lenght

Number of electrodes group level 1

Number of groups level 1

Number of groups level 2

Number of groups level 3

Total number of electrodes

20 μm

0.1 μm

1 μm

2 μm

0.5 μm

381 μm

500 μm

1 μm

2 μm

13 μm

65 μm

500 μm

15 mm

3

3

3

3

81

Table 3.4: characteristics model for large gap and deflections

The APDL macro is given in Appendix C. Figures 3.26-3.27 show the meshed model.

Figure 3.26: FEM model of sensor from table 3.4. Detail gap and 9 group of electrodes

38

Figure 3.27: FEM model of sensor from table 3.4. Detail of gap and 3 groups of electrodes

The curves equivalent input capacitance versus displacement are shown in Figure 3.283.29.

-4

1.64

x 10

output capacitance, 3x3x3x3 model, g=20 um

1.63

capacitance [pF/um]

1.62

1.61

1.6

1.59

1.58

1.57

1.56

-100

-80

-60

-40

-20

0

20

displacement [um]

40

60

80

100

Figure 3.28: Input equivalent capacitance per unit length versus displacement

Due to the large number of electrodes, the number of nodes per electrode had to be kept

low to avoid an excessive number of elements in the model. Because of the lower number

of nodes per electrode, the results for different displacements showed less consistency

than in other simulations. Figure 3.29 filters the results to minimize the error.

39

-4

filtered output capacitance, 3x3x3x3 model, g=20 um

x 10

1.62

capacitance [pF/um]

1.61

1.6

1.59

1.58

1.57

-80

-60

-40

-20

0

20

displacement [um]

40

60

80

100

Figure 3.29: Input equivalent capacitance per unit length versus displacement. Results from ANSYS

filtered with MATLAB (MATLAB code given in Appendix D)

-Model for connected plates, 4 electrodes

During the alignment, the nanopositioner may connect electrically both plates. For this

case, a model was developed to obtain the input equivalent capacitance. In this case,

instead of 5 electrodes, there would be 4 electrodes. The equivalent input impedance in

function with the lumped capacitances was obtained as well. Its deduction is given in

Appendix F.

The model has the characteristics given in Table 3.4. The results from the FEM simulator

are shown in Figure 3.30-3.31.

-4

3.5

x 10

substrates wired,three groups, per unit lenght g=0.1 um

c12

c13

c14

c23

c24

c34

3

capacitance [pF/um]

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

Figure 3.30: Lumped capacitance matrix

40

4

-4

3.5

x 10

substrate wired, three groups, per unit lenght, g=0.1um

c12

c13

c23

cout

3

capacitance [pF/um]

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.31: C12, C13, and C23 from lumped capacitance matrix and input equivalent capacitance (cout)

-Model for glass top electrode

Another model was developed to analyze the influence of non-conductive plates. In this

case, the plate on top was modeled as Silicon dioxide. Figures 3.32-3.33 show the model

meshed.

Figure 3.32: Glass top plate meshed model. It can be seen in the figure that the space for the top

plate has been meshed

41

Figure 3.33: Glass top plate meshed model. The detail of the gap shows, from the bottom to the top, air not

meshsed, a layer of silicon dioxed, the electrodes, air between the electrodes, a top electrode, and a large

surface meshed which is the top plate

The results from the model with the characteristics of Table 3.4 are shown in Figure 3.343.35.

Figure 3.34: Lumped capacitance matrix model glass top plate

-4

1.5

three groups, top substrate glass, g=0.1um

x 10

1.4

capacitance [pF/um]

1.3

1.2

1.1

1

0.9

0.8

0.7

0.6

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.35: Input equivalent capacitance model glass top plate

42

-Model for glass top electrode

In Figures 3.36-3.38, simulations for a model with glass bottom plate are shown.

Figure 3.36: Meshed model with glass bottom plate. Meshed model with glass bottom plate.

Detail of gap on the left

-4

3.5

three groups, bottom substrate glass, g=0.1um

x 10

c12

c13

c14

c23

c24

c34

3

capacitance [pF/um]

2.5

2

1.5

1

0.5

0

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.37: Lumped capacitance matrix model glass bottom plate

43

-4

1.4

three groups, bottom substrate glass, g=0.1um

x 10

1.3

capacitance [pF/um]

1.2

1.1

1

0.9

0.8

0.7

0.6

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.38: Input equivalent capacitance model glass bottom plate

-Four models compared

To analyze the influence of the plates in the equivalent input capacitance, the following

figure compares the results from the four models above.

simulations 4 simplified models

2.2

top subs glass

subs wired

bottom subs glass

5 electrodes

2

capacitance [pF]

1.8

1.6

1.4

1.2

1

0.8

-4

-3

-2

-1

0

1

displacement [um]

2

3

4

Figure 3.39: Equivalent input capacitance from models with different plate characteristics.

Although whether the plates are conductive or dielectric has an influence on the

equivalent input capacitance, the sensor would work for all the cases studied.

44

3.5 Convergence

To obtain the optimal mesh in terms of accuracy and computation time, the algorithm

convergence was analyzed. Because the greatest field gradient is at the space between

electrodes 1, 2, and 3 (see Figure 2.1), the mesh must be finer around them. The macros

used for capacitance extraction specify the number of nodes on the surface of electrodes

1, 2, and 3 surfaces, and leave the rest as auto mesh. This results in a much denser mesh

around the electrodes. To find the optimal number of nodes on the electrodes’ surface,

simulations changing the number of nodes were carried out. Figures 3.40-3.41 show a

mesh with 5 nodes per electrode and a mesh with 105 nodes per electrode. The APDL

macro is given in Appendix E.

Figure 3.40: Detail of meshed model with 5 nodes per electrode’s horizontal surface

Figure 3.41: Detail of meshed model with 105 nodes per electrode’s horizontal surface

Figures 3.42-3.44 show the dimensionless lumped matrix capacitance versus the number

of nodes per electrode surface for different gaps.

45

convergency, 3x3 model, g=0.1 um

capacitance(nodes)/capacitance(5 nodes)

1.03

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

cout

1.02

1.01

1

0.99

0.98

0.97

0.96

0.95

0.94

0

20

40

60

80

nodes per surface electrode

100

120

Figure 3.42: Dimensionless lumped matrix capacitance. Gap 0.1 μm.

The capacitance is divided by the capacitance obtained with 5 nodes per electrode surface

convergency, 3x3 model, g=1 um

capacitance(nodes)/capacitance(5 nodes)

1.015

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

cout

1.01

1.005

1

0.995

0.99

0.985

0.98

0

20

40

60

80

nodes per surface electrode

100

120

Figure 3.43: Dimensionless lumped matrix capacitance. Gap 1 μm.

convergency, 3x3 model, g=10 um

capacitance(nodes)/capacitance(5 nodes)

1.004

c12

c13

c14

c15

c23

c24

c25

c34

c35

c45

cout

1.002

1

0.998

0.996

0.994

0.992

0.99

0.988

0.986

0.984

0

20

40

60

80

nodes per surface electrode

100

120

Figure 3.44: Dimensionless lumped matrix capacitance. Gap 10 μm.

46

Figures 3.42--3.44 show that reaching convergence requires less number or nodes for

larger gaps. This was expected, since shorter gaps induce greater potential gradients. A

large gradient leads to greater errors in the integration, so to keep the error low the

number of nodes has to be increased.

Reference:

[3.1] F. Stellari, A. L. Lacaita, ‘New Formulas of Interconnect Capacitances Based on

Results of Conformal Mapping Method’, IEEE Vol. 47, No. 1, January 2000

[3.2] N. D. Arora, K. V. Raol, R. Schumann, L. M. Richardson, ‘Modeling and

Extraction of Interconnect Capacitances for Multilayer VLSI Circuits’, IEEE Vol. 15,

No.1 January 1996.

[3.3] A. Toulouse, D. Bernard, C. Landrault, P. Nouet, ‘Efficient 3D Modelling for

Extraction of Interconnect Capacitance in Deep Submicron Dense Layouts’.

[3.4] U. Choudhury, A. Sangiovanni-Vincentelli, ‘Automatic Generation of Analytical

Models for Interconnect Capacitances’, IEEE 1994.

[3.5] ‘Ansys Low-Frequency Electromagnetic Analysis Guide’, Ansys Release 10.0,

August 2005

[3.6] http://ccrma.stanford.edu/~jos/NumericalInt/Lumped_vs_Distributed_Systems.html

[3.7] A. Hieke, ‘Simple APDL implementation of a 3D FEM simulator for mutual

capacitances of arbitrarily shaped objects like interconnects’, SIEMENS Microelectronics,

c/o IBM Semiconductor Research & Development Center.

[3.8] J, W. Nilsson, ‘Electric Circuits’, Addison-Wesley Publishing Company, Fourth

Edition.

47

4. Capacitance-to-voltage converters

4.1 Introduction

In chapter 2 the sensor was modeled by a lumped capacitor connected to a circuit. To

measure the impedance of a capacitor, an excitation is applied to one of the terminals, as

illustrated in Figure 4.1

Figure 4.1: Capacitance in function with displacement and voltage supplied

The output current through the capacitor is the derivative of stored charge with respect to

time. By using the definition of capacitance C=Q/V, and the definition of current i=dQ/dt,

the following expression is obtained

iC

dQ

dV

C

C

V

dt

dt

t

(4.1)

where V is the voltage applied, and δ the displacement. Assuming that the excitation

voltage is a sinusoidal function whose frequency is much higher that the rate of

capacitance change with displacement, Eqn. (4.1) is simplified to

iC C

dV

d

C A sin( t ) CA cos(t )

dt

dt

48

(4.2)

where A is the applied voltage amplitude, and ω the frequency. According to Eqn. (4.2), a

capacitor with a sinusoidal voltage excitation can be modeled as a sinusoidal current

source modulated by the capacitance itself. This description can easily be extended to any

periodic excitation as long as the excitation frequency is much larger than the variation of

capacitance over time.

4.2 Converters

A converter is an electrical circuit aimed at transforming an electrical signal to another

more convenient electrical signal. As explained in Section 4.1, the output of a capacitor is

a periodic current modulated by the capacitance. To electrically process this signal, it

must be converted to a different electrical signal easier to process, such as a bias voltage

linear with the capacitance or a digital signal.

Because the purpose of a capacitance-to-voltage converter is to detect changes in

capacitance, the performance will be mainly evaluated by the circuit’s ability to read the

minimum possible change in capacitance, which is limited by the circuit’s noise. The

root-mean-square (RMS) of a circuit’s noise waveform vn(t) is defined as [4.13]

tˆ / 2

v n rms v lim

ˆ

2

n

t

(v

n

(t )) 2 dt

(4.5)

tˆ / 2

Similar to the definition of RMS voltage noise, the RMS minimum detectable

capacitance is defined as [4.14]

C min rms

vnrms

dvo / d (C )

49

(4.6)

where vo is the output voltage and ΔC is a change in the capacitance to measure over the

initial capacitance.

Extensive literature research on capacitance converters was carried out during this project

to obtain a wide understanding of the different approaches and select the best readout

circuit. The most common converters are described and analyzed throughout the

following sections.

4.3 Oscillators

Capacitance-controlled oscillators have been widely analyzed in the instrumentation

literature. However, currently other types of converters are replacing this technique. A

capacitance-controlled oscillator is based on an oscillator whose time period is modulated

by a capacitance. A modification of Martin oscillator is shown in Figure 4.2 [4.2]

Figure 4.2: Modified Martin oscillator for multielectrode capacitive sensors [4.2].

The period of the circuit in Figure 4.2 is

T=4R(Coffset-Cos+Cx,i)

(4.5)

which is proportional to the sensor capacitance Cx,i. Although large accuracy and linearity

can be achieved with this technique, the output would require complex signal processing.

Furthermore, the oscillator performance is highly dependant on parasitic capacitances.

50

4.4 Capacitive bridge

Capacitive bridges are based on the well-known Wheatstone bridge [4.3]. A possible

implementation is shown in the Figure 4.3.

Figure 4.3: Capacitive bridge

The output voltage of such circuit is

Vo V

C1 C 2

Cf

(4.6)

In the scheme of Figure 4.3, the capacitance C1 and would be replaced by the sensor

equivalent capacitance, and C2 by a reference capacitor. The main disadvantage of this

circuit is its high sensitivity to parasitic capacitances.

4.5 Transimpedance amplifier

4.5.1 Gain and noise

The transimpedance amplifier, or charge amplifier, is basically a current to voltage

converter, i.e. a circuit that converts a current modulated signal to a voltage modulated

signal. The following figure shows the schematic of such circuit, modeling the capacitor

and its voltage supply as a current source

51

Figure 4.4: Transimpedance amplifier

The output voltage of the circuit is

Vo = -Rf Is

(4.7)

Modifying the circuit of Figure 4.4 for differential input, and including parasitic

capacitances, the circuit results in that shown in Figure 4.5

Figure 4.5: Transimpedance amplifier, sensor capacitance, and excitation. Cref can be used to cancel an

offset of Cs. Assuming that Cs=Coff+ΔC, if Cref=Coff, the circuit will only measure ΔC.

where Cr is a reference capacitance, and Cp models any parasitic capacitance at the

inverting input of the op-amp. Applying Eqn. (4.7), the output of this circuit is

│Vo│=2 π fdrive Vs Rf ΔC

(4.8)

being Vs the input voltage amplitude, fdrive the input excitation frequency, Rf the feedback

resistor, and ΔC the change in capacitance over Cs. The feedback resistor, with the

parasitic and sensor capacitance, creates a low pass filter, which limits the bandwidth.

The pole of this filter is [4.6]

f pole

1

1

2 R f (2C s C p )

52

(4.9)

The optimal circuit performance is obtained at resonance frequency, which is given by

the pole frequency given in Eqn. (4.9) and the amplifier gain bandwidth. Therefore, the

optimal drive frequency is

f driveopt GBWamp

1

2R f (2C s C p )

(4.10)

where GBWamp is the amplifier gain bandwidth. By substituting Eqn. (4.10) in Eqn. (4.8),

the output voltage for an optimal drive frequency is obtained

Vo

2 (GBWamp ) R f

(2C s C p )

Vm (C )

(4.11)

The amplifier noise can be modeled by ideal components and current/voltage sources

dependent on noise. The following circuit shows the amplifier with ideal components and

the noise sources.

Figure 4.6: Transimpedance amplifier with noise sources

By applying superposition, the output voltage noise is

v n ,rms en ( R f in ) 2 4 K B TR f 4 K B TR f

2

(4.12)

The approximation of Eqn. 4.12 assumes that an optimal ultra-low noise op-amp is used,

so that the feedback resistor is the dominant noise source. The minimum detectable

capacitance as defined in Eqn. 4.6 is:

53

C min rms

2 K BT (2C s C p )

1

Vm

(GBWamp )

BW

(4.13)

Even though the feedback resistor is the main source of error, the minimum capacitance

detectable does not depend on the feedback resistor value. While the feedback resistor

increases the noise linearly with its resistance value, the capacitance measurement is also

amplified linearly with the feedback resistance. Therefore the feedback resistance value is

cancelled out for the signal to noise ratio, and the minimum capacitance detectable

becomes independent of the feedback resistance. Figures 4.7-4.8 show the minimum

detectable capacitance for different cases.

minimum

detectable capacitance transimpedance amplifier

-3

1.5

x 10

Cmin-rms [aF/sqrt(BW)]

1.45

1.4

1.35

1.3

1.25

1.2

1.15

1.1

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

parasitic capacitance [pF]

Figure 4.7: Minimum detectable capacitance by transimpedance

amplifier assuming Vm=1V, T=300 K, GBWamp=1 MHz, Cs=1pF

54

minimum detectable capacitance transimpedance amplifier

3

10

Csensor=1nF

Csensor=1pF

Csensor=1fF

2

Cmin-rms [aF]

10

1

10

0

10

-1

10

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

parasitic capacitance/sensor capacitance

Figure 4.8: Minimum detectable capacitance by transimpedance

amplifier assuming Vm=1V, T=300 K, GBWamp=1 MHz, BW=100 KHz.

4.5.2 Stability

The amplifier model of Figure 4.4 assumes no parasitic capacitances and infinite

resistance. A more realistic model is shown in Figure 4.9.

Figure 4.9: Transimpedance amplifier with parasitic capacitance Cs and sensor finite resistance Rs

Cs introduces two drawbacks in the circuit. First, as the frequency increases, the

impedance of Cs decreases. Therefore, at high frequencies Cs acts as a short circuit, and

so the current from the source Is flows through Cs instead of through Rf. This leads to a

reduction of bandwidth. Second, Rf and Cs create a low pass filter, which introduces

negative phase into the system and reduces the bandwidth. Figures 4.10-4.11 show the

55

frequency and time response of the circuit in Figure 4.9 under different stray capacitances

Cs.

Figure 4.10: Output voltage Vo for Cs=0, Cs=50 pF, and Cs=200 pF.

Figure 4.11: Frequency response for Cs=0, Cs=50 pF, and Cs=200 pF.

Figure 4.10 shows how the output voltage oscillation increases with larger values of stray

capacitance. The reduction of bandwidth due to stray capacitance is illustrated in Figure

4.11. To improve the stability, a resistance is included in parallel in the feedback as in

Figure 4.12.

56

Figure 4.12: Transimpedance amplifier with capacitive feedback to improve stability. The values used for

the simulations are indicated in the figure

The feedback capacitor Cf creates a high pass filter with Rs, which adds positive phase to

the system and pushes the circuit into stability. Figure 4.13 shows simulation of the

circuit in Figure 4.12 under different values of Cf.

Figure 4.13: Simulations circuit Figure 4.12 for Cf= 0, Cf=2 pF, Cf=4 pF

The drawback of this approach is the reduction of bandwidth due to the low pass filter

composed by Cf and Rf..

57

Figure 4.14: Frequency response simulations circuit Figure 4.12 for Cf= 0, Cf=2 pF, Cf=4 pF

4.5.3 Synchronous demodulator

The outputs of the transimpedance amplifier and capacitive bridge are both sinusoidal

voltages modulated by the sensor capacitance. To convert this signal to a more

convenient DC signal proportional to the capacitance, a synchronous demodulator can be

used. This circuit ideally implements the following equations

Vo = Vin if Vin>0

Vo= -Vin if Vin<0

(4.14)

The following figure shows the diagram of this circuit

Figure 4.15: synchronous demodulator circuit. An amplifier obtains the negative of the input signal. A

periodic excitation, usually a square wave, controls two switches that close and open at opposite times.

58

An accurate and flexible converter can be implemented by applying a high frequency

voltage to the unknown impedance and another known reference capacitance, amplifying

the signal, applying it to a demodulator, and low-pass filtering it. A scheme is shown in

the Figure.

Figure 4.16: capacitance to voltage converter based on synchronous demodulation

The following figure shows the output waveform of the different blocks

Figure 4.17: output waveforms from the different blocks of a capacitance to voltage amplifier.

From left to right, amplifier, synchronous demodulator, and low-pass filter

4.6 Switched-capacitor Converter

4.6.1 Switched-capacitor Amplifier

Switched-capacitor circuits are based on replacing resistances by capacitors and switches.

Figure 4.17 shows a simple circuit with a resistance

59

Figure 4.18: circuit with resistance

The current flowing through the resistor is

I=R1(V2-V1)

(4.15)

If the resistor is replaced by a capacitor and two switches, the circuit in figure 4.19 is

obtained

Figure 4.19: Circuit with switched-capacitor equivalent resistance

The switches are controlled by two non-overlapping complementary clocks like in Figure

4.20.

phi1

t

phi2

t

Figure 4.20: Non-overlapping clocks

When clock φ1 is high, the capacitor charges up to V1, whereas when φ2 is high, the

capacitor charges/discharges up to V2. Therefore, from one phase to the next one there is

a transfer of charge of

60

Q = C (V1 – V2)

(4.16)

With a switch rate fclk, the amount of current transferred per unit time is

Q fclk = C fclk (V1 – V2)

(4.17)

Eqn. 4.17 has the unit of currents, so that an average current can be defined as

Iavg = C fclk (V1-V2)

(4.18)

Assuming that the clock frequency is much higher than the voltage waveforms frequency,

the switches and capacitor can be modeled as an equivalent resistance [4.4]

Req

V1 V2

1

I avg

Cf clk

(4.19)

Based on Eqn. 4.19, an inverting amplifier with capacitors instead of resistors can be

implemented. In principle, an inverting amplifier implemented with capacitances would

not provide a dc bias for the op-amp input. This is shown in Figure 4.21.

Figure 4.21: Inverting amplifier with capacitive feedback. This configuration does not provide

dc bias at the op-amp input