Subtask 1 - WordPress.com

advertisement

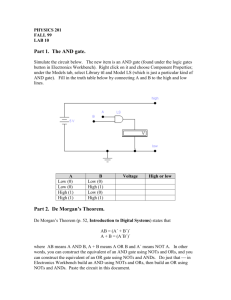

Leeds College of Technology National Diploma for IT Practitioners (Networking Level 3) Unit 9 – Computer Architecture Unit Tutor: [OMITTED] Name: Tat Ho Tat Ho Computer Architecture Page 1 of 37 10 March 2009 Tat Ho Computer Architecture Page 2 of 37 10 March 2009 Contents: 1.1 Number Systems................................................................... 3 - Notation........................................................................................ 3 - The Base Number........................................................................ 4 - How number systems are stored in memory................................ 4 - Binary Coded Decimal (BCD) ....................... .............................. 4 1.2 Analogue to Digital Conversion.......................................... 5 - Method of Conversion………………………………………........... 5 1.3 Decimal and Hexadecimal Conversion............................... 6 1.4 Arithmetic Hexadecimal operations.................................... 7 2.1 Logic Gates........................................................................... 9 2.2 A-Stable and Bi-Stable Flip Flops....................................... 13 2.3 Prototype for a Process Control System........................... 15 - Truth Table................................................................................. 15 - Output........................................................................................ 15 - Boolean Terms and Expressions............................................... 15 - Logic Circuit (Unsimplified)......................................................... 16 - Karnaugh Map............................................................................ 17 - Simplified Expression................................................................. 17 - Logical Circuit (Simplified).......................................................... 17 - Evaluation................................................................................... 17 2.4 Features of a Processor.......................................................... 19 - Key Components of Computer Architecture............................... 19 - Fetch Execute Cycle................................................................... 20 - Comparing and Contrasting Two Processors.............................. 24 3.1 SMS Program Simulator.............................................................. 25 3.2 SMS Traffic Light Simulator....................................................... 29 Tat Ho Computer Architecture Page 3 of 37 10 March 2009 Tat Ho Computer Architecture Page 4 of 37 10 March 2009 Subtask 1.1 (P1) Describe using examples how numeric and alphanumeric data can be coded within a computer system. Numeric and alphanumeric data within a computer system can be coded in several ways. One method in which, uses what we call number systems in order to represent values. Number Systems Part I: A number system is a defined system in which we use to represent numerical values. Values in number systems can be converted from one to another and vice versa. For example the most common number system of today is the decimal number system. You can convert a decimal value into a hexadecimal value. Other forms of number systems that are used in computing are Hexadecimal, Octal and Binary. The following table will show how a decimal number system relates in respect to the other number systems. Notation: You will notice that to avoid confusion, the number notation is xy (x to the base y), with the base number always written as a subscript. Binary (Base 2) Octal (Base 8) Decimal (Base 10) Hexadecimal (Base 16) 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 00 (000) 01 (001) 02 (010) 03 (011) 04 (100) 05 (101) 06 (110) 07 (111) 10 (001) (000) 11 (001) (001) 12 (001) (010) 13 (001) (011) 14 (001) (100) 15 (001) (101) 16 (001) (110) 17 (001) (111) 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 A B C D E F Tat Ho Computer Architecture Page 5 of 37 10 March 2009 The Base Number: Each number system will have a base number. The following table will show you the relationships between the base number and the range of values that specific number system can take. Number System Range of Values Number of Digits Base Number Binary Octal Decimal Hexadecimal 0–1 0–7 0–9 0–F 2 8 10 16 2 8 10 16 Number Systems Part II: Binary: Has two digits consisting of values ranging from 0-1, and has 2 different unique characters. The binary place values can be represented in the following table: 28 27 26 25 24 23 22 21 128 64 32 16 8 4 2 1 Octal: Has eight digits consisting of values ranging from 0-7, and has 8 different unique characters. The way an octal value is written is in a series of three binary digits. Notice that the values of 8 and 9 are not recognised as only the numbers 0-7 are used. Decimal: Has ten digits consisting of values ranging from 0-9, and has 10 different unique characters. Hexadecimal: Has sixteen digits consisting of values ranging from 0-9, followed by A-F and has 16 different unique characters. How Number Systems are Stored in Memory: When you wish to store data in memory, there are a few things you have to consider which are the entities address and the data location. The way information is stored is dependant on the width of the bus. For example a 16bit data on a 4bit bus will require it to be sent in parts of 4. Binary Coded Decimal This is a 4 bit representation of numerical values as shown in the table below: Decimal 0 1 2 3 4 5 6 7 8 9 Digit BCD 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Code For example to represent 55 in BCD this will be: 0101 0101. Tat Ho Computer Architecture Page 6 of 37 10 March 2009 Data Storage in a Computer: Location Contents 1 0 0 0 204 0 0 1 0 0 1 0 0 205 1 0 0 1 This is how data is stored in RAM. The location 204 and 205 are each segment of a set space in RAM. The contents can hold up to 8 bits of information. As you can see above, 4 BCD’s can be stored in the two locations. Characters in ASCII: In order to represent characters in binary, you would have to convert the binary value into a decimal value. You will then use each of the characters to represent a BCD code for each. If I were to represent the word ‘binary’, this would be; ASCII Character b i n a r y Tat Ho Binary 01100010 01101001 01101110 01100001 01110010 01111001 Decimal 98 105 110 97 114 121 Computer Architecture Page 7 of 37 BCD Code 1001 1000 0001 0000 0101 0001 0001 0000 1001 0111 0001 0001 0100 0001 0010 0001 10 March 2009 Subtask 1.2 (P2) Describe how analogue data can be converted and stored in computer systems. [OMITTED] Tat Ho Computer Architecture Page 8 of 37 10 March 2009 Subtask 1.3 (P3) The following data is stored in memory locations in an 8-bit memory store. Convert each binary number into decimal and hexadecimal. [OMITTED] Tat Ho Computer Architecture Page 9 of 37 10 March 2009 Subtask 1.4 (P4) Convert the following hexadecimal into binary and perform the operations shown using 2’s complement arithmetic where appropriate. Reconvert the results to hexadecimal. [OMITTED] Tat Ho Computer Architecture Page 10 of 37 10 March 2009 Task 2 Subtask 2.1 (P7) Describe with the aid of truth tables, the operation of six basic logic gates. For each gate include the logic symbol and logic expression. A logic gate is one in which performs a logical operation. In the following I will go through the six main ones that are used universally. Gate Truth Table NOT INPUT OUTPUT A NOT A 0 1 1 0 Symbol Description Gate Truth Table This gate inverts the output of the gate. It is most commonly known as an inverter. Therefore a 1 input results in a 0 output, conversely a 0 input results in a 1 output. AND INPUT OUTPUT A B A AND B 0 0 0 0 1 0 1 0 0 1 1 1 Symbol Description Tat Ho This gate only produces an output when all the inputs are 1. Computer Architecture Page 11 of 37 10 March 2009 Gate Truth Table OR INPUT OUTPUT A B A+B 0 0 0 0 1 1 1 0 1 1 1 1 Symbol Description Gate Truth Table This gate produces a 1 output when the conditions of having a 1 in the input are met. NAND INPUT OUTPUT A B A NAND B 0 0 1 0 1 1 1 0 1 1 1 0 Symbol Description Tat Ho Opposite of AND with inverter at the end. This can be considered as a combination of the AND and NOT gate. This gate produces a 1 output in any combination except from 1 and 1. Computer Architecture Page 12 of 37 10 March 2009 Gate Truth Table NOR INPUT OUTPUT A B A NOR B 0 0 1 0 1 0 1 0 0 1 1 0 Symbol Description Gate Truth Table Opposite of OR with inverter at the end. This can be considered as a combination of the OR and NOT gate. This gate produces an output when there is no input to this gate (i.e. both are 0). XOR INPUT OUTPUT A B A XOR B 0 0 0 0 1 1 1 0 1 1 1 0 Symbol Description Tat Ho This gate produces a 1 output when the inputs are not identical. i.e. both are 0 or 1. Computer Architecture Page 13 of 37 10 March 2009 Gate Truth Table XNOR INPUT OUTPUT A B A XNOR B 0 0 1 0 1 0 1 0 0 1 1 1 Symbol Description Tat Ho This gate produces a 1 output when both the inputs are the same. Computer Architecture Page 14 of 37 10 March 2009 Subtask 2.2 (M4) Describe the difference between an a-stable and a bi-stable flip-flop. Explain how these devices are used as memory elements and a computer clock source. A-stable: This circuit is a free running oscillator. It oscillates between two states at a certain frequency defined by the clock cycle intervals in the circuit itself. This then generates a wave output that can be described as a ‘square wave’. Another example of an a-stable circuit is the 555 integrated circuit. The IC can produce very accurate oscillations used in popular applications. The diagram below shows the configuration of an a-stable flip flop consisting of an oscillator, a switch and an ‘AND’ gate. There is a buzzer to indicate that the circuit is functioning. This is a universal 555 timer which is implemented in many circuit boards. Bi-stable: This circuit is defined by having a state that is either on or off. It remains in this state until one of the switches is activated. Tat Ho Computer Architecture Page 15 of 37 10 March 2009 It is also called a ‘flip-flop’. The bi-stable circuit provides uses in several applications such as frequency dividers, counters, or a storage device in computer memory. In order to store data in a memory location, you would implement the use of a bi-stable circuit. For example the data below will be stored unless the ‘reset’ switch is activated. 0 Tat Ho 1 0 1 1 0 1 0 Computer Architecture Page 16 of 37 10 March 2009 Subtask 2.3 (M2, D1) Design a prototype for a process control system with the aid of the following: - Truth Table - Output - Boolean Terms and Expressions - Logic Circuit (Unsimplified) - Karnaugh Map - Simplified Expression - Logical Circuit (Simplified) - Evaluation The specification states that the system has four inputs (A, B, C, D) with a single output (X). The system will be used to check a four-bit binary (word) number within the HEX range 0 to F. A being the most significant and D the least significant bit. The output will produce a logic ‘1’ at the output (X) whenever an odd number is detected. NOTE: HEX Value F ignored. Truth Table: Variable A B C D 0 1 2 3 4 5 6 7 8 9 10 (A) 11 (B) 12 (C) 13 (D) 14 (E) 15 (F) 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 O/P Terms 1 A∙B∙C∙D 1 A∙B∙C∙D 1 A∙B∙C∙D 1 A∙B∙C∙D 1 A∙B∙C∙D 1 A∙B∙C∙D 1 A∙B∙C∙D EXP = A∙B∙C∙D + A∙B∙C∙D + A∙B∙C∙D + A∙B∙C∙D + A∙B∙C∙D + A∙B∙C∙D + A∙B∙C∙D Tat Ho Computer Architecture Page 17 of 37 10 March 2009 Logical Circuit (Unsimplified): The above shows an unsimplified version of the logical circuit. - The switches are all switched on. - The output can be seen from the 7 segment LED. - The LED indicator shows that there is no output value. - The oscillator makes the LED appear to be flashing. Tat Ho Computer Architecture Page 18 of 37 10 March 2009 Karnaugh Map: a = C∙D b = A.D c = A.B.D EXP = C∙D + A.D + A.B.D Simplified Expression: D(A + AB + C) Logical Circuit: Evaluation: Using the Karnaugh Map process is to create a more simplified circuit. This is highly beneficial due to the significantly fewer gates used in the processed circuit for example in the above circuits, the original gates used were 23, whereas using the Karnaugh Map, we reduced to to 8. It can reduce costs to Tat Ho Computer Architecture Page 19 of 37 10 March 2009 manufacturers if there is a complex circuit involving several hundred logical gates. Another advantage of having reduced number of gates is that it is easier to service and allows more space for more functionality. Fault finding would be far more easier compared to the more complex un-simplified version of the circuit. Tat Ho Computer Architecture Page 20 of 37 10 March 2009 Subtask 2.4 (P5, P6, M1, D2) Describe the key components of computer architecture and how they interact. (P5) Produce a section in your report which describes, with the aid of diagrams, (including logic gates, registers, buses, PC, Control unit, ALU and Memory) the features of a processor and how data travels around the processor. (P6, M1) Compare and contrast two different processors. (D2). Key Components of Computer Architecture: [OMITTED] The control unit controls the flow of data going though the processor. The Arithmetic Logic Unit performs mathematical operations. Fetch Execute Cycle Part I: Logic gates are a set of predefined gates that produce a series of operations. Tat Ho Computer Architecture Page 21 of 37 10 March 2009 Fetch Execute Cycle II: Control Bus Data Bus Address Bus This represents the allocation slots in RAM (memory) [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 22 of 37 10 March 2009 [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 23 of 37 10 March 2009 [OMITTED] Tat Ho Computer Architecture Page 24 of 37 10 March 2009 Comparing and Contrasting Two Processors: [OMITTED] Tat Ho Computer Architecture Page 25 of 37 10 March 2009 Task 3 Subtask 3.1 Simple Addition [OMITTED] Registered the value of AL. Registered the value of BL. Result is shown in register AL. Tat Ho Computer Architecture Page 26 of 37 10 March 2009 Simple Subtraction [OMITTED] Registered the value of AL. Registered the value of BL. Result is shown in register AL. Tat Ho Computer Architecture Page 27 of 37 10 March 2009 Simple Multiplication [OMITTED] Registered the value of AL. Registered the value of BL. Result is shown in register AL. Tat Ho Computer Architecture Page 28 of 37 10 March 2009 Simple Division [OMITTED] Registered the value of AL. Registered the value of BL. Result is shown in register AL. Tat Ho Computer Architecture Page 29 of 37 10 March 2009 Subtask 3.2 Traffic Light Sequence Control Truth Table Seq Lights EW 1 R 2 RA 3 G 4 A 5 R 6 R 7 R 8 R 9 R On NS R R R R R RA G A R Hex 90 D0 30 50 90 98 84 88 90 EW (East West ) R A G 1 0 0 1 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 NS (North South) R A G 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 1 0 1 0 1 0 0 Spare 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Source code for traffic light system: [OMITTED] Tat Ho Computer Architecture Page 30 of 37 10 March 2009 - Registers: These can be considered as data stores that stores data from the code a user defines – and is then executed. Currently you can see the AL register with the value of 10010000 (90) and the BL register with the value 00010101 (15). - Traffic Light Simulation: This is a real-time simulation that shows you visually what commands are being executed in order to produce specific lights to be turned on. Currently both red lights are turned on. - RAM Hexadecimal View: This shows you the current entries stored in RAM. There are three views, namely; X Hexadecimal, Y ASCII, Z Source. c Tat Ho Computer Architecture Page 31 of 37 10 March 2009 Currently you can see the AL register with the value of 11010000 (D0) and the BL register with the value 00010101 (15). This represents RED + AMBER, and RED. Notice that in the RAM hexadecimal view the pointer has moved to the next set of instructions. [OMITTED] Tat Ho Computer Architecture Page 32 of 37 10 March 2009 [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 33 of 37 10 March 2009 [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 34 of 37 10 March 2009 [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 35 of 37 10 March 2009 [OMITTED] [OMITTED] Tat Ho Computer Architecture Page 36 of 37 10 March 2009 [OMITTED] Tat Ho Computer Architecture Page 37 of 37 10 March 2009