OVER VIEW

CAD E N C E A N A L O G /

MIX E D - S I G N A L D E S I G N

MET H O D O L O G Y

The Cadence® Analog/Mixed-Signal (AMS) Design Methodology employs

advanced Cadence Virtuoso® custom design technologies and leverages

silicon-accurate design flows to help design teams create differentiated silicon

faster and with less risk. It delivers verified and packaged methodologies

demonstrated on a real-world mixed-signal design. The Cadence AMS Design

Methodology combines the best of top-down (behavioral and mixed-level

approaches) with bottom-up (transistor-level design and abstraction) design

techniques to achieve predictable, high-quality results for complex mixedsignal designs.

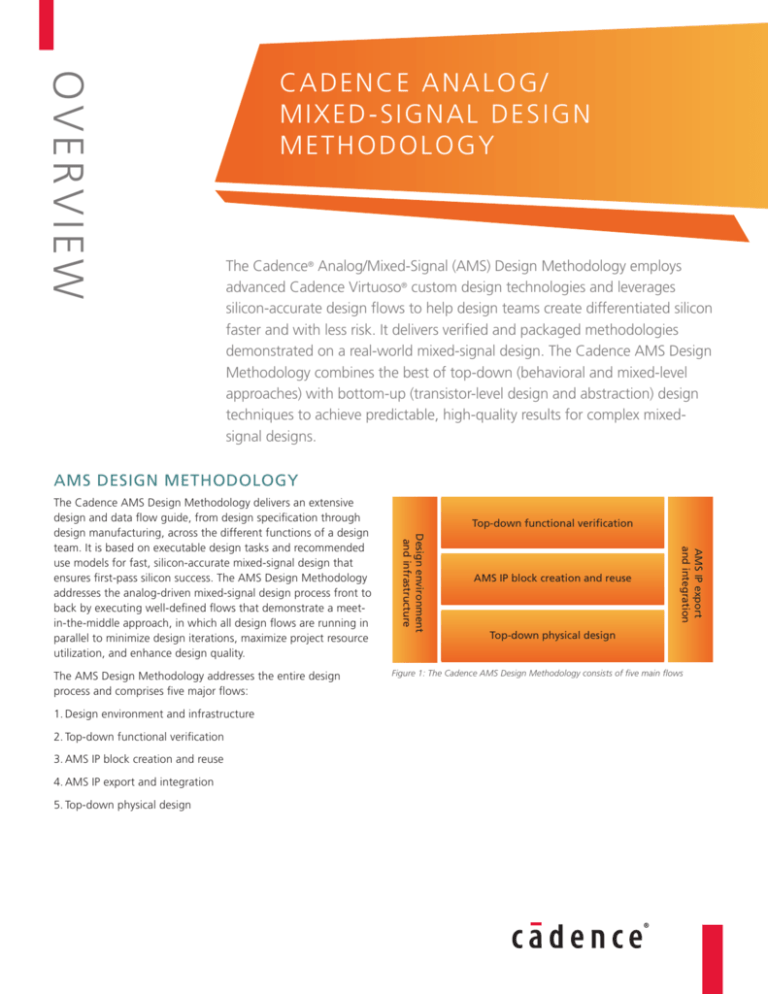

AMS DESIGN METHODOLOGY

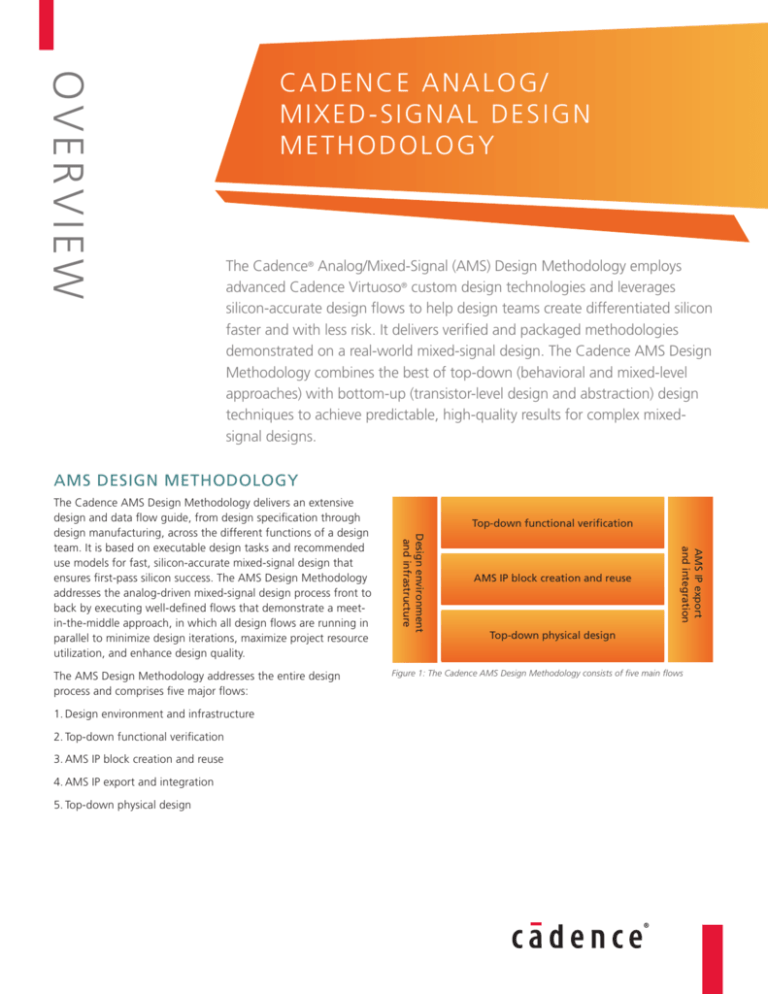

1.Design environment and infrastructure

2.Top-down functional verification

3.AMS IP block creation and reuse

4.AMS IP export and integration

5.Top-down physical design

AMS IP block creation and reuse

AMS IP export

and integration

The AMS Design Methodology addresses the entire design

process and comprises five major flows:

Top-down functional verification

Design environment

and infrastructure

The Cadence AMS Design Methodology delivers an extensive

design and data flow guide, from design specification through

design manufacturing, across the different functions of a design

team. It is based on executable design tasks and recommended

use models for fast, silicon-accurate mixed-signal design that

ensures first-pass silicon success. The AMS Design Methodology

addresses the analog-driven mixed-signal design process front to

back by executing well-defined flows that demonstrate a meetin-the-middle approach, in which all design flows are running in

parallel to minimize design iterations, maximize project resource

utilization, and enhance design quality.

Top-down physical design

Figure 1: The Cadence AMS Design Methodology consists of five main flows

Design Data

Input

1A

Target

CDK

(90nm)

Top-Down Functional Design

Design Data

Output

2

AMS Block

Validation Strategy

3

AMS Block Design

Partitioning

6

AMS Block

Functional

Concept

Validation

4

Sub-Blocks

Specifications

8A

Analog Block

Circuit Design and

Optimization

5A

Analog Block

Circuit Design

1B

Design

Specs

5B

Analog Block

Behavioral Design

1C

System-Level

Models

and Sims

13

AMS Block

Functional

Post-Layout

Validation

10A

12A

Block Physical

Estimation

Analog Physical

Design

8C

Block IP

Qualification

5D

Digital Hierarchical

RTL Design

16

AMS Block

Functional

Signoff

Validation

14

Block Physical

Integration

Preparation

17

AMS Block

Preparation

for SoC

Integration

12B

Digital Block

Physical Design

8B

Digital Design

Synthesis

5C

Analog Block

Circuit Migration

1D

Third-Party

IP

9

AMS Block

Functional

Performance

Validation

12C

Block IP Layout

Integration

10B

Block IP Physical

Import

12D

Analog Block

Layout Migration

5E

Block IP

Bottom-up Functional and Physical Design

7

1E

Legacy

IP

AMS Block Early

Floorplanning

11

AMS Block

Refinement

Floorplanning

15

AMS Block

Assembly

Top-Down Physical Design

Figure 2: The combination of top-down (behavioral/mixed-level) and bottom-up (transistor-level design/abstraction) techniques ensures high-quality results

ETHERNET PHY Transceiver Macro

The five flows are further divided into modules of logically related

design tasks, which are illustrated and documented with in-context

scenarios. The different scenarios are demonstrated on a siliconimplemented and verified real-life design, namely an Ethernet

physical layer macro (PHY) and a sigma-delta fractional-N PLL

frequency synthesizer macro for WLAN applications. The Ethernet

PHY contains 20k analog devices and 30k digital gates including

typical analog, digital, and mixed-signal blocks such as flash ADC,

VGA, equalizer, and clock recovery circuit. The fractional-N PLL is a

2.4GHz synthesizer that contains 20k devices and includes a 5GHz

LC VCO, a high-speed divider, on-chip regulators, and a calibration

mechanism for loop filtering and VCO.

10BASE-T

Receiver

Rx

Polarity Correction

Squelch Link Detect

VGA Control

Digital Equalizer/Slicer

Timing/BLW Control

10BASE-TX

Receiver

Clk

10BASE-T PLL

100BASE-TX PLL

Digital

60k Gate

Tx

Analog 30k Device

Both Ethernet PHY and frac-N PLL are implemented on a 90nm

generic process design kit (GPDK), which has virtually all the

aspects of an actual design kit. The design blocks have all the

necessary views for complete design, including symbols,

schematics, constraints, behavioral models, abstracts, layout, and

extracted views, as well as configurations, testbenches, and

simulation states. A design team can use the reference design as

a basis to enter a new design domain, understand a wide range

of new Virtuoso technologies, acquire new methodologies, and

map selected elements onto their own design environment.

Clock Recovery

Manchester Decoder

MLT-3

Decoder

Descrambler

Autonegotiation

10BASE-T

Driver

4B/5B

Decoder

Collision

Carrier Sense

MII

Manchester Encoder

Digital Waveshaping

MLT-3

Dedoder

Scrambler

100BASE-TX

Driver

dvdd/dgnd

dvdd/dgnd

Modulator

Control

∆∑

Modulator

4B/5B

Encoder

ATB

1.2V (LF)

MultiModulus

Divider

1.2V (LF)

1.2V (HF)

1.2V (HF)

1.2V (HF)

PFD &

CP

Loop

Filter

LPF

VCO

RC

Calibration

Control

dvdd/dgnd

VCO

Calibration

Control

dvdd/dgnd

1.2V Regulator (HF)

1.2V Regulator (LF)

1.2V (HF)

I&Q

Divide

by 2

Figure 3: The Cadence AMS Design Methodology is demonstrated

on a real-world mixed-signal design

www.cadence.com

CADENCE ANALOG/MIXED-SIGNAL DESIGN METHODOLOGY

2

FEATURES

TOP-DOWN FUNCTIONAL VERIFICATION

DESIGN ENVIRONMENT AND INFRASTRUCTURE

Any design process takes place in a certain environment including

different projects, CAD tools, process design kits (PDKs), and users

on different hardware platforms and operating systems. It is very

important to create a consistent design environment to ensure the

quality of the design and the credibility of the results.

A comprehensive functional verification flow is presented,

spanning all levels of abstraction and all design stages, from

planning to post-layout device-level signoff verification. First, an

introduction to the concept of design partitioning and simulation

planning is given. Next, behavioral modeling guidelines and

testbench strategies are presented.

This part of the Cadence AMS Design Methodology gives the

foundation to set up a design environment using tested and

proved methods and technologies, including incremental tool

access, project directory structure, how to set up and control

PDKs, and how to automate project and flow setup using the

Design Environment and Configuration Manager.

A consistent testbench structure is used over all later stages of

verification, starting with concept validation using behavioral

model representation in AMS simulation, and system validation

using Simulink/AMS co-simulation. Next is performance

validation using mixed-level-transistor plus behavioral-level

simulation on Virtuoso AMS Designer Simulator with SDF

backannotated to the digital part.

The data exchange between the design house and the foundry is

explained, detailing required datasets from the foundry and how

to qualify them against the defined AMS flows. Special attention

is given to the PDK—how to automatically check its content

using the Data Surveyor and how to use the Incremental

Technology Database (ITDB) to customize and enhance the PDK

Finally, a post-layout and signoff verification is prepared to include

both analog extracted parasitics and SDF backannotation for the

most accurate timing estimation using Virtuoso AMS-Ultra

Simulator. An IDDQ analysis is performed using full extracted

transistor-level DC simulation with the Virtuoso UltraSim Full-Chip

Simulator along with top-level EM IR drop analysis.

/projects/

ProjectA/

deslibs/

ProjectB/

ProjectC/

doc/

Project

Documents

Design

libraries

user1/

user2/

.cdsinit

Working

libraries

.cds.lib

assura_tech.lib

display.drf

.csdenv

hdl.var

Figure 4: AMS design environment and infrastructure

www.cadence.com

Figure 5: AMS top-down functional verification

CADENCE ANALOG/MIXED-SIGNAL DESIGN METHODOLOGY

3

AMS IP BLOCK CREATION AND REUSE

AMS IP EXPORT AND INTEGRATION

A thorough approach to creation of both analog and digital blocks

is presented using productivity-oriented Virtuoso technology. The

constraints concept and management is used to amend the

schematic with the required information to automatically create its

layout. Furthermore, constraints can be inferred from pre-defined

circuit structures using the Circuit Prospector Assistant.

The IP flow is a comprehensive guide for analog and digital IP

handling, from top-level integration to extensive characterization

and packaging. On the exporting side, a complete step-by-step

scenario of characterizing and modeling an analog IP in Verilog®AMS is presented, taking an N-bit flash ADC as an example.

Automated testbench extraction is discussed; generic behavioral

model planning, coding, and debugging is illustrated. The model

includes advanced features like noise, aperture time, INL, and DNL

parameters. The layout abstract is generated using the Virtuoso

Abstract Generator. The timing information (.lib) file for top-level

digital integration is generated using Virtuoso Spectre® MDL

language and verified by importing to the Cadence Encounter®

platform. Finally, packaging of all generated views for publishing is

discussed and implemented using Vulcan technology.

New layout techniques like design-rule–driven (DRD), module

generator (Modgen), and constraint-driven editing are shown in

action through a dedicated assisted layout module. A new approach

to simulation is shown through the specification-oriented simulation

platform (Virtuoso Analog Design Environment) with its numerous

productivity enhancement features including simulation history,

check points manager, parameterization flow, design specifications,

and parasitic estimation flow. The high-capacity Virtuoso Analog

Design Environment optimization engine is used for local and global

optimization on the block level, over corners, and as a yield

optimizer with Monte Carlo and sensitivity analyses.

Target PDK

Target DFH library

where generated

DFH will be located

Repository directory

where non-DFH

outputs will be stored

Processing scratch run

directory for various

log files and

temporary data

Inherited connections

definition for

global nodes

List of cell found in

various inputs data and

the target repository

library if it already exists

Each entry represents a

cell and columns

represents views that

need to be created and

to be re-used

Selection of views

to be created

Definition of power

and ground nodes

used at several stages

of view creation (RCX,

CeltiC, VoltageStorm)

Figure 6: AMS IP block creation and reuse

Later, Virtuoso Layout Optimizer is used to boost the yield on

the back end. A tutorial introduction to analog-driven digital

implementation using the Virtuoso Digital Implementation Option

shows a typical digital layout flow including planning, prototyping,

placement, routing, timing optimization, clock tree synthesis, SDF

generation, parasitic extraction, and parasitic closure.

www.cadence.com

Figure 7: AMS IP export and integration

CADENCE ANALOG/MIXED-SIGNAL DESIGN METHODOLOGY

4

On the importing and integration side, feasibility of IP integration

employing multi-technology simulation (MTS) is exemplified,

followed by actual import using Vulcan technology. Legacy cdb

file import into the Virtuoso OpenAccess (OA) database is shown.

Importing of digital IP in an analog context is also presented.

TOP-DOWN PHYSICAL DESIGN

The physical design flow introduces a true top-down approach to

chip layout using state-of-the-art Virtuoso technologies. Special

emphasis is given to early floorplanning to get information about

the critical parasitics to feed back to the verification flow. This is

possible through a Virtuoso Floorplanner, a Physical Hierarchy

Configurator, and an Abstract Generator, along with several

floorplanning techniques like connectivity analysis, area

estimation, pushdown block shaping, and pin optimization. The

flow is illustrated on the PLL.

The analog-oriented physical assembly and routing is described

using both Virtuosos Chip Assembly Router and Virtuoso SpaceBased Router, both accepting design constraints. The flow is

demonstrated by top-level routing of the Ethernet PHY and the

PLL macro using advanced analog routing techniques like critical

signal, differential signal, shielded signal, bundle, and supply

routing. After routing, chip finishing is applied, including metal

density and antenna checks, metal filling, and guard rings.

The assembled layout is then verified using Cadence Assura®

verification technology with dedicated scenarios for Design Rule

Checking (DRC), Layout Versus Schematic (LVS) checking, and

Parasitic Extraction (RCX) applied to the Ethernet PHY. A

comprehensive guide to practical Assura features like flat and

hierarchical, black-box or selected area checking, different

netlisting, and extracted parasitic formats is illustrated.

EXECUTABLE SCENARIOS

DESIGN ENVIRONMENT AND INFRASTRUCTURE FLOW

• AMS design flow overview

• Foundry enablement

• Project environment setup

• Automated project setup with the Design Environment and

Configuration Manager

• Reference Data Surveyor

• ITDB implementation

TOP-DOWN FUNCTIONAL VERIFICATION FLOW

• Design partitioning and simulation planning

• Concept validation

• AMS/Simulink co-simulation

• AMS functional verification

• Signoff functional verification

• IDDQ simulation

• EM IR drop analysis with DSPF stitching

AMS IP BLOCK CREATION AND REUSE FLOW

• Constraint-driven analog block creation

• Analog block design simulation

• Analog block design optimization

• Interactive assisted analog layout

• Electrical yield optimization

• Layout yield optimization with Virtuoso Layout Optimizer

• Digital block implementation

AMS IP EXPORT AND INTEGRATION FLOW

• Analog IP characterization, front end

• Analog IP characterization, back end

• IP import feasibility study using MTS

• IP Import using Vulcan methodology

Figure 8: AMS top-down physical design

www.cadence.com

• IP import for Virtuoso methodology

CADENCE ANALOG/MIXED-SIGNAL DESIGN METHODOLOGY

5

• Virtuoso integration of digital IP

PRODUCT INTEGRATION

• Digital IP characterization

• Virtuoso Multi-Mode Simulation

• IP packaging for publishing and reuse

• Virtuoso Spectre Circuit Simulator

TOP-DOWN PHYSICAL DESIGN FLOW

• Virtuoso AMS Designer Simulator

• Hierarchical floorplanning

• Virtuoso UltraSim Full-Chip Simulator

• Top-level assembly with Virtuoso Chip Assembly Router

• Virtuoso Analog Design Environment (ADE)

• Top-level assembly with Virtuoso Space-Based Router

• Virtuoso Schematic Editor

• Chip finishing

• Virtuoso Layout Suite

• Physical verification Assura DRC

• Virtuoso Layout Migrate

• Physical verification with Assura LVS

• Virtuoso Analog VoltageStorm Option

• Parasitic extraction with Assura RCX

• Virtuoso Analog ElectronStorm Option

• Assura Design Rule Checker (DRC)

• Assura Layout vs. Schematic (LVS) Verifier

• Assura Parasitic Extraction (RCX)

• SoC Encounter™ RTL-to-GDSII System

For more information

contact Cadence sales at:

+1.408.943.1234

or log on to:

www.cadence.com/

contact_us

© 2009 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, Assura, Encounter, Spectre, Verilog, and Virtuoso are registered

trademarks and SoC Encounter is a trademark of Cadence Design Systems, Inc. All others are properties of their respective holders.

21053 06/09 MK/MVC/DM/PDF