Pipeline ADC - Hong Kong University of Science and Technology

advertisement

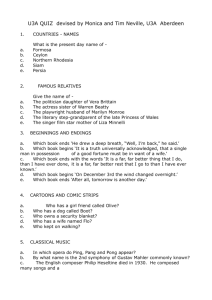

Lecture 4 Pipeline ADC George Yuan Hong Kong University of Science and Technology Fall 2010 © George Yuan, HKUST 1 Outline • Pipeline ADC – MDAC – Comparator • Sample and Hold • Calibration – Linear – Nonlinear © George Yuan, HKUST 2 Applications Signal Frequency MHz Range 10-14 bits Flash Folding Pipeline Σ-Δ Resolution Communication, digital camera/video © George Yuan, HKUST 3 Quantization + Amplification 4-bit Flash Vref Vr14 Vr12 Vr10 Vin 1000 Vr8 Two-Step ADC Vref ×4 Vr3 Vref Vr3 Vi,i+1=4×(Vo,i-Vr) 10 Vr2 Vr2 Vr1 Vr1 Vr6 Vr4 Vr2 Vr1 0 © George Yuan, HKUST 00 0 0 4 Pipeline ADC High throughput Long latency © George Yuan, HKUST 5 1-bit MDAC Algorithmic ADC: Ideal transfer function: © George Yuan, HKUST 6 MDAC Cascade bi-1 Vi-2 2-bit MDAC Vi-2 Vi bi-1, bi 00 0 01 Vref 2 0 - Vref 2 - Vref 4 Vref 4 - © George Yuan, HKUST Vref 2 Vref 2 7 Non-ideal 1-bit MDAC Ideal transfer function: Sub-ADC threshold variation: Can’t be recovered by following stages Vth Vth © George Yuan, HKUST 1. No tolerance on threshold voltage; 2. Flash ADC power consumption is high 8 Over-ranging bi-1 Vi-2 Vi-2 2-bit MDAC Vi bi-1, bi 0 0 Vref 2 - Vref 2 - Vref 4 Vref 4 - © George Yuan, HKUST Vref 2 Vref 2 9 MDAC with Redundancy Ideal transfer function: Sub-ADC threshold variation: Can still be recovered by following stages 1. tolerance on threshold voltage; 2. Flash ADC power consumption reduced © George Yuan, HKUST 10 1.5-bit MDAC ø2 Vres(i) Cf ø1 ø1 Cs ø2 ø1a Comp2 © George Yuan, HKUST Code Gen Comp1 -0.5Vr 0 Vres(i+1) ø1 +0.5Vr 11 1.5-bit MDAC @ phase 1 © George Yuan, HKUST 12 1.5-bit MDAC @ phase 2 © George Yuan, HKUST 13 Ideal 1.5-bit MDAC Transfer Function Vin < Vth1= -1/8 Vref, -1/8Vref=Vth1<Vin<Vth2=+1/8Vref, Vin>Vth2=+1/8Vref, 00 © George Yuan, HKUST 01 Di=00, Vdac=-0.5Vref Di=01, Vdac=0 Di=10, Vdac=+0.5Vref 10 14 ADC with Redundancy Vn V1 Vi STn ST2 ST1 D2 D1 Dn Digital Error Correction Dadc © George Yuan, HKUST 15 Digital Error Correction Shift addition: pipeline output (D11, D12) (D21, D22), (D31, D32),….,(Dn1, Dn2) D11 D12 D21 D22 D31 D32 + …. Digital code For example: If the input signal is -0.5Vref: final code 0 If the input signal is 0.5Vref: final code (1111111….10) If the input signal is 0: final code (100000…00) © George Yuan, HKUST 16 DEC Example © George Yuan, HKUST 17 Error Cascading Effect 1. Accuracies of the MDACs at the front of the pipeline are more significant 2. More power for the front MDACs © George Yuan, HKUST 18 Multi-bit MDAC 00 01 10 11 000 010 100 110 001 011 101 Vo Vo 1 Vref 2 - 1 Vref 2 1 Vref 2 Vi - 1 Vref 2 Vi 1 Vref 2 1 Vref 2 - 1 Vref 2 - 1 Vref 2 1 Vref 16 Resolved bits: M Codes: C = 2M+1-1 Threshold levels: L = C-1 = 2M+1-2 Threshold tolerance: Vref/2M+2 © George Yuan, HKUST 3 Vref 16 5 Vref 16 19 Multi-bit MDAC Circuits ø2 Cf ø1 ø1 Cs Vres(i) ø1 V2 V1 ø2 ø2 b2 +0.5Vrb1 -0.5Vr 0 -0.5Vr 0 Cs b0 +0.5Vr ø1a ø1 ø1 ø2 Vres(i+1) Cs V0 Vo = 4Vi – V0 – V1 – V2 -0.5Vr 0 +0.5Vr © George Yuan, HKUST 20 Thresholds and Codes Vo = 4Vi – V0 – V1 – V2 Code b2 b1 b0 V2 V1 V0 Thresholds 6 1 1 1 0.5Vr 0.5Vr 0.5Vr 3/8Vr 5 1 1 0 0.5Vr 0.5Vr 0 2/8Vr 4 1 0 0 0.5Vr 0 0 1/8Vr 3 0 0 0 0 0 0 0 2 -1 0 0 -0.5Vr 0 0 -1/8Vr 1 -1 -1 0 -0.5Vr -0.5Vr 0 -2/8Vr 0 -1 -1 -1 -0.5Vr -0.5Vr -0.5Vr -3/8Vr © George Yuan, HKUST 21 OTA Speed Cf Cs Cl t settling 10 10 10 1 Ts 2f c 3dB 2 GBWo 4 For example: © George Yuan, HKUST 1 4 GBWo 20 fs GBWo 26 f s 22 Subtraction Accuracy ø1 1. Settling error 2. Charge injection 3. Clock feedthrough © George Yuan, HKUST Vi ø1 ø1a Q 23 Gain Accuracy Cf Cs Vos Vr Ideal gain: A = A Cl Cs Cf © George Yuan, HKUST Real gain? 24 Finite Amplifier Capacitor Mismatch Cs C f Cs C f Cs V V V Vo C s C f os Cs C f r Cs C f i Cf Cf Cf A A A Vo For 12-bit ADC A? c ? Vi © George Yuan, HKUST 25 Noise Rs1 vns1 vncf Rs2 vns2 vncs vns3 Rs3 Rs2 vns2 Cf Rs1 Cs vns1 vna © George Yuan, HKUST 2 vncf kT Cf 2 vncs kT Cs 1 1 1 Rs1 Rs 2 sC f sC s sC f Vo s Vs1 Va Vs 2 1 1 Rs1 Rs1 sC s sC s Rs 2 vno 2 vno Cl 2 2 C f Cs Cf 2 Cs 2 2 vncs vncf vna Cf C f Cs Cf kT 2 Cs vna 1 Cf Cf 2 26 Power Scaling © George Yuan, HKUST 27 Gain Error © George Yuan, HKUST 28 Recovery: Analog and Digital Vin Din MDAC Vres Dres Back-end ADC b Digital recovery: Di = Dres + B×A Analog recovery: Vi = = © George Yuan, HKUST Vres + Vth,b A 1 ( Vres+ AVth,b ) A 29 Code Gap © George Yuan, HKUST 30 Self-Calibration Vi ×A Σ SHA Sub-ADC Sub-DAC Vo Vr D Dcal = D + 1 Analog input Vi: Digital code D Vo1 Digital code D+1 Vo2 Code gap = Vo2 – Vo1 © George Yuan, HKUST 31 Dynamic Comparator Vref+ 2 Vi+ 2a 1 Vcm Vi- C1 2 C2 2 C2 1 Vcm Vx+ Pre-amp Latch D Vx- C1 2 C1 Vref Vr = C2 + C1 2a Vcm Vref© George Yuan, HKUST 32 ADC Timing Vref+ ø2 Vi ø1 ø1 Vcm ø1 Vi- -0.5Vr 0 +0.5Vr MDAC1 Sampling COMP1 Converting C1 2a Vcm 1 Vo ø1a Code Gen Comp2 Vi+ Cs ø2 Comp1 2 Cf 2 2 1 Vref- C2 Vx+ Pre-amp C2 C1 2 2a Vcm MDAC1 Sampling COMP1 Converting MDAC1 Amplifying COMP1 Precharging MDAC2 Sampling COMP2 Converting MDAC2 Amplifying COMP2 Precharging MDAC2 Sampling COMP2 Converting MDAC3 Sampling COMP3 Converting MDAC3 Amplifying COMP3 Precharging © George Yuan, HKUST D Vx- MDAC1 Amplifying COMP1 Precharging 1 Latch 2 33 Pipelined Output half cycle MDAC1 MDAC2 © George Yuan, HKUST MDAC n-1 MDACn 34 Outline • Pipeline ADC – MDAC – Comparator • Sample and Hold • Calibration – Linear – Nonlinear © George Yuan, HKUST 35 Sample-and-Hold Vi Rs Vs fs Input bandwidth: f 3dB 1 2Rs C Vs Vi 1 e t Acquisition time: Switch noise: © George Yuan, HKUST 2 vns C kT C Rs C Settling Error 10% 2.3 1% 4.6 .1% 6.9 .01% 9.2 .001% 11.5 .0001% 13.8 36 Aperture Time Accuracy t = Vsig t1 Ts For sinusoidal signal (a, fsig): Vsig trise Vclk t2 a d 2 dB 20 log f sig t rise Vclk trise=100ps, Vclk=1.2V, a=200mV, fsig=100MHz d2 = -45.6dB © George Yuan, HKUST 37 Differential Sampling Vi+ Rs1 Vs+ fs C1 1 k a d 2 dB 20 log f sig t rise 1 k Vclk k: matching parameter Vi- Rs2 fs C2 a d 3 dB 40 log f sig t rise 2 Vclk Vstrise=100ps, Vclk=1.2V, a=200mV, fsig=100MHz if k=1, d3 = -97.3dB if k=0.9, d2 = -71.2dB © George Yuan, HKUST 38 Bootstrap Vclk doubles, distortion reduces 6dB © George Yuan, HKUST 39 Signal Dependent Bootstrap On-resistance, on-moment are constant © George Yuan, HKUST 40 Signal Dependent Bootstrap © George Yuan, HKUST 41 Low Signal Feedthrough Switch © George Yuan, HKUST 42 Double-buffered SHA © George Yuan, HKUST 43 Feedback SHA © George Yuan, HKUST 44 Fully-differential SHA © George Yuan, HKUST 45 SHA-less • 1st MDAC sampling aperture error • MDAC and flash sampling network match © George Yuan, HKUST 46 Extra Clock Phase • No matching is required • Good for higher sampling accuracy • 1 extra clock phase © George Yuan, HKUST 47 Outline • Pipeline ADC – MDAC – Comparator • Sample and Hold • Calibration – Linear – Nonlinear © George Yuan, HKUST 48 Digital Calibration Concept Vn V1 Vi STn ST2 ST1 D2 D1 Dn Real-time Digital Recovery Dadc • DEC does not work because MDAC gain is not 2 • More accurate digital recovery, e.g. Di = Dres + A·Di+1 © George Yuan, HKUST 49 MDAC Error Model © George Yuan, HKUST 50 Reference Error Removal Vx / VR 2 e2 (Vn / VR1 e1 ) N (e ADC GD1VR1 GD1Vn N ) / VR 2 e2 (Vn / VR1 e1 ) N • Correlation-based • N is a random sequence • On average, = 0 VR1 = VR2/GD1 © George Yuan, HKUST 51 Reference Dithering Dout 2 1 1 Vin VREF PN Vcal 1 1 1 • Obtain the reference error • Subtract from the digital signal © George Yuan, HKUST 52 Digital Error Model Adaptation • Guess error parameters • Recover a rough output • Compare with an accurate channel result • Adapt the error parameters © George Yuan, HKUST 53 Open-Loop MDAC © George Yuan, HKUST 54 Third-order Distortion Estimation © George Yuan, HKUST 55 Gain Distortion Model © George Yuan, HKUST 56 mth-order Gain Distortion Compensation © George Yuan, HKUST 57 Gain Distortion Compensation © George Yuan, HKUST 58 References 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. R. van de Plassche, Integrated Analog-to-Digital and Digital-to-Analog Converters, Kluwer, 2003 D. Johns, and K. Martin, Analog Integrated Circuit Design, Wiley, 1997 B. Song, S. Lee, and M. Tompsett, “A 10-bit 15MHz recycling two-step A/D converter”, IEEE J. Solid-State Circuits, Vol. 25, pp. 1328-1337, Dec. 1990 A. Dingwall, and V. Zazzu, “An 8MHz CMOS subranging 8-bit A/D Converter”, IEEE J. Solid-State Circuits, Vol. SC-20, pp. 1138-1143, Dec. 1985 B. Brandt, and J. Lutsky, “A 75mW, 10-b, 20MSPS CMOS subranging ADC with 9.5 effective bits at Nyquist”, IEEE J. Solid-State Circuits, Vol. 34, pp. 1788-1795, Dec. 1999 D. Cline, and P. Gray, “A Power Optimized 13-b 5 Msamples/s pipelined analog-to-digital converter in 1.2um CMOS”, IEEE J. Solid-State Circuits, Vol. 31, pp. 294-303, Mar. 1996 I. Mehr, and L. Singer, “A 55mW 10bit 40Msample/s Nyquist Rate CMOS ADC”, IEEE J. Solid-State Circuits, Vol. 35, pp. 318-325, Mar. 2000 B. Lee, B. Min, G. Manganaro, J. Valvano, “A 14-b 100MS/s Pipelined ADC with a Merged SHA and First MDAC”, IEEE J. Solid-State Circuits, Vol. 43, pp. 2613-2619, Dec. 2008 U. Moon, B. Song, “Background digital calibration techniques for pipelined ADCs”, IEEE Trans. Circuits & Systems II, Vol. 44, pp. 102-109, Feb. 1997 J. Ming and S. Lewis, “An 8-bit 80-Msample/s pipelined analog-to-digital converter with background calibration,” IEEE J. Solid-Sate Circuits, vol. 36, pp. 1489–1497, Oct. 2001. Yun-Shiang Shu, and Bang-Sup Song, “A 15-bit Linear 20-MS/s Pipelined ADC Digitally Calibrated With Signal-Dependent Dithering” IEEE J. Solid-Sate Circuits, VOL. 43, NO. 2, FEBRUARY 2008, pp. 342–350 Xiaoyue Wang, Paul J. Hurst, and Stephen H. Lewis “A 12-Bit 20-Msample/s Pipelined Analog-to-Digital Converter With Nested Digital Background Calibration ” IEEE J. Solid-Sate Circuits, VOL. 39, NO. 11, NOVEMBER 2004 pp.1799–1808 Boris Murmann, Bernhard E. Boser, “A 12bit 75MS/s pipelined ADC Using Open-loop Residue Amplification,” IEEE J. Solid-State Circuits, vol. 38, no.12, pp.2040-2050, Dec 2003 A. Panigada, and I. Galton, “A 130mW 100MS/s Pipelined ADC with 69dB SNDR Enabled by Digital Harmonic Distortion Correction”, IEEE J. Solid-State Circuits, vol. 44, no.12, pp.3314-3328, Dec. 2009 © George Yuan, HKUST 59