OP-64 - Analog Devices

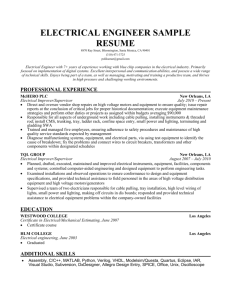

advertisement

--.

ANALOG

W DEVICES

High-Speed,

WideBandwidth

Operational

Amplifier(AycL~ 5)

OP-64

FEATURES

High Slew Rate

Fast Settling Time (+10V,0.1%)

GENERAL DESCRIPTION

..

. Gain-BandwidthProduct(AvCL

= +5)

.

.

. Low Supply Current

""",..""""'

130V/JJ.sMin

100nsTyp

The OP-54 is a high-performance monolithic operational amplifier that combines high speed and wide bandwidth with low power

consumption. Advanced processing techniques have enContinued

80MHzTyp

8mA Max

8nV/-fflZ Typ

1mV Max

:t80mA Typ

".""""".""'"

Low Noise

. Low Offset Voltage

High Output Current

. Eliminates External Buffer

. Standard 8-Pin Packages

Available in Die Form

PIN CONNECTIONS

OBS

.

ORDERING

INFORMATION

t

PACKAGE

8 I DISABLE

OLE

HERMETIC

OPERATING

HERMETIC

PLASTIC

LCC

TEMPERATURE

vos MAX TO-99

DIP

8-PIN

2O-CONTACT

RANGE

(mV)

8-PIN

8-PIN

MIL

OP64ARC/BB3

1.0

OP64AJ' OP64AZ.

XIND

1.0

OP64EJ OP64EZ

XINO

2.0

OP64FJ OP64FZ

XINO

2.5

OP64GP

XINO

2.5

OP64GS,t

TA =+25°C

w

..J

CD

..J

q5q~q

zzzoz

tt

q~q:jq

z

z ~

z z

Burn-in is available on commercial and industrial temperature range parts in

CerDIP, plastic DIP, and TO-99 can packages.

For availability and burn-in information on SO and PLCC packages, contact

your local sales office.

EPOXYMINI-DIP

(P-Suffix)

8-PIN CERDIP

(Z-Suffix)

EPOXYSO

(S-Suffix)

I

XIND= Extended IndustrialTemperature Range, -40°C to +B5°C

. Fordevices processed intotal complianceto MIL-SDT-B83,

add/B83 afterpart

number. Consult factory for 883 data sheet.

t

I

20-LEAD HERMETIC LCC

(RC-Suffix)

DISABLE

TE

~

Y- (CASE)

TO-99

(J-Suffix)

SIMPLIFIED SCHEMATIC

Y+

DISABLE

OUT

Y-

NULL

NULL

--

-----

II

OP-64

GENERAL DESCRIPTION Continued

enabled PMI to make the OP-64 superior in cost and performance to many dielectrically-isolated

and hybrid op amps.

Slew rate of the OP-64 is over 130V/flS. It is stable in gains of ~5

and has a settling time of only 100ns to 0.1 % with a 10V step

input. However, unlike other high-speed op amps which have

high supply requirements, the OP-64 needs less than 8mA of

supply current. This enables the OP-64 to be packaged in space

saving 8-pin packages. The OP-64 can deliver :t80mA of output

current eliminating the need for a separate buffer ~Iifier

in

many applications. Noise of the OP-64 is only 8nV-.JHz, reducing system noise in wide band applications. In addition to its dynamic performance, the OP-64 adds DC precision with an input

offset voltage of under 1 mY.

The OP-64 is an ideal choice for RF, video and pulse amplifier

applications and in new designs can replace the HA-5190/95 or

EL-2190/95 with improved performance and reduced power

consumption. Its high output current also suits the OP-64 for use

in AID or cable driver applications. The OP-64 includes a DISABLE pin which, when set low, shuts the amplifier off and reduces the supply current to 0.75mA.

OBS

ELECTRICAL

PARAMETER

CHARACTERISTICS

SYMBOL

Supply Voltage

20V

TA = +25°C,

OP-64A/E

MIN

TYP

-

Vos

Input Bias

Current

IB

VCM=OV

Input Offset

Current

los

VCM=OV

Input Voltage

Range

IVR

(Note 1)

CMR

VCM=t11V

Power-Supply

Rejection Ratio

PSRR

Vs = t5V to t18V

Large-Signal

Voltage Gain

Avo

RL = 2kn, Vo = t10V

RL = 2000, Vo = t5V

30

12.5

Output Voltage

Swing

Vo

RL = 2k12

RL = 20012

t10

Output

Current

lOUT

Supply

Current

ISY

Common-Mode

Rejection

UNITS

alc

TO-99 (J)

18

.CIW

8-Pin Hermetic DIP (Z)

148

16

.CIW

8-Pin Plastic DIP (P)

103

43

.CIW

98

38

.CIW

158

43

.CIW

20-Contact LCC (RC, TC)

8-Pin SO (S)

-

2. a'A is specified for worst case mounting conditions, Le., aJA is specified for

d~vicein socket for TO, CerDIP, P-DIP, and LCC packages; ajA is specified

for device soldered to printed circuit board for SO package.

unless

MAX

MIN

1

-

0.8

0.2

1

-

0.1

1

TE

MAX

100

84

45

18

20

10

t12.5

t11.7

t11

t10

6.2

-

MAX

UNITS

2.5

mV

0.4

2

0.8

2.5

IlA

0.3

2

0.6

2.5

IlA

-

t11

94

31.6

35

16

t12.5

t11.7

-

t80

8

OP-64G

TYP

1.2

15

17.8

MIN

2

t11

5

t11

noted.

OP-64F

TYP

0.4

t11

90

otherwise

t80

No Load

+175°C

+175°C

+150°C

+300°C

150

OLE

:t18V

Offset

Voltage

alA (Note 2)

-65°C to +175°C

-65°C to +150°C

.

-55°C to +125°C

-40°C to +85°C

-40°C to +85°C

1. Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

at Vs = :t15V,

CONDITIONS

PACKAGE TYPE

Supply Voltage

10 sec

NOTES:

ABSOLUTE MAXIMUM RATINGS (Note 1)

Supply Voltage """""""""""""""""""""""""""""'"""

Input Voltage

Differential Input Voltage

DISABLE Input Voltage

Output Short-Circuit Duration

Storage Temperature Range

(J, Z, RC)

(P, S)

Operating Temperature Range

OP-64A (J, Z, RC)

OP-64E, F (J, Z) """"""""""""""""""""'"

OP-64G (P, S)

Maximum Junction Temperature

OP-64A (J ,Z, RC) """""""""""""""""""""""""'"

OP-64E, F (J, Z)

OP-64G (P, S) """"""""""""""""""""""""""""'"

Lead Temperature (Soldering, 60 see)

6.2

V

84

94

-

dB

-

15

31,6

IlVN

20

10

35

16

t11

t10

V/mV

t12.5

V

t11.7

t80

8

6.2

mA

8

mA

NOTE:

1. Guaranteed

2-702

by CMR test.

OPERA TlONAL AMPLIFIERS

REV. A

-~--

--

~

OP-64

ELECTRICAL

CHARACTERISTICS

at Vs = :t15V, TA= +25°C, unless otherwise noted.

PARAMETER

SYMBOL

CONDITIONS

Disable Supply

Current

ISY DIS

Total lor both supplies

DISABLE

Current

IDIS

DISABLE = OV

Slew Rate

SR

RL = 2kO

Full-Power

Bandwidth

BWp

(Note 2)

Gain-Bandwidth

Product

GBWP

Ay = +5

Settling Time

ts

MIN

DISABLE = OV

film

Input

Capacitance

CIN

Open-Loop

Output

Resistance

Ra

Voltage

Noise

en

Density

10= 10kHz

Current Noise

Density

in

External Vas

Trim Range

Rpot= 20kO

Supply Voltage

Range

Vs

10= 10kHz

-

0.5

1

OP-64F

TYP

MAX

MIN

1

0.75

OP-64G

TYP

MAX

UNITS

1

mA

0.75

-

0.5

0.5

mA

-

130

170

130

170

2

2.7

-

2

2.7

2

2.7

-

MHz

V/S

-

80

-

-

80

-

80

-

MHz

-

100

-

-

100

-

100

-

ns

-

57

-

-

57

-

-

57

-

degrees

-

5

-

-

5

-

-

5

-

pF

-

30

-

0

Ay=+5

I 0 = 10Hz

0.75

MIN

170

10V Step 0.1%

10= 100Hz

I 0 = 1kHz

-

MAX

130

OBS

Phase Margin

OP-64A/E

TYP

OLE

-

30

-

-

30

-

-

-

-

-

30

10

8

8

-

-

30

10

8

8

-

7.5

-

7.5

-

-

4

-

4

-

:t5

:t15

:t18

:t15

:t18

NOTES:

1. Guaranteed by CMR test.

2. Guaranteed by slew-rate test and lormula BWp = SR/(2n10VpEAK).

-

-

-

:t5

-

30

10

8

8

-

7.5

-

4

-

mV

:t5

:t15

:t18

V

TE

-

nV /...fHZ

pN...fHz

II

OP-64

ELECTRICAL

CHARACTERISTICS

PARAMETER

SYMBOL

Offset

Voltage

Vos

Input Bias

Current

IB

VCM=OV

los

VCM=OV

IVR

(Note 1)

CMR

VCM=:t11

PSRR

Vs = :t5Vto :t18V

Input Offset

Current

Input Voltage

Range

Common-Mode

Rejection

Power-Supply

at Vs = ::!:15V,-40°C :;;TA:;; +85°C for OP-64E/F/G,

CONDITIONS

OBS

Rejection Ratio

Large-Signal

Voltage Gain

Avo

Output Voltage

Swing

Vo

Supply

Current

ISY

RL= 2k12,Vo =:t10V

RL = 20012, Vo = :t5V

RL= 2k12

RL = 20012

NOTE:

1. Guaranteed by CMRtest.

ELECTRICAL

PARAMETER

CHARACTERISTICS

SYMBOL

CONDITIONS

-

0.5

1.5

-

1.0

3

-

1.5

3.5

mV

-

0.3

2.5

-

0.5

3

-

1.5

3.5

A

-

0.2

2.5

-

0.5

3

-

1.0

3.5

A

:t11

-

-

:t11

-

-

:t11

-

-

V

86

100

-

80

94

-

80

94

-

dB

-

5

31.6

-

15

50

-

15

50

V/V

20

7.5

40

12

-

15

5

35

10

-

15

5

35

10

V/mV

:t11

:t10

:t12.3

:t11.5

-

:t11

:t10

:t12.3

:t11.5

-

:t11

:t10

:t12.3

:t11.5

V

-

6.3

8.5

-

6.3

8.5

-

6.3

MAX

MIN

OP.64G

TYP MAX

UNITS

8.5

mA

TE

OP-64A

TYP

MAX

0.4

-

Input Bias

Current

IB

VCM = OV

Input Offset

Current

los

VCM=OV

Input Voltage

Range

IVR

(Note 1)

CMR

VCM=:t11

Power-Supply

Rejection Ratio

PSRR

Vs = :t5V to:t18V

Large-Signal

Voltage Gain

Avo

RL = 2kn, Vo =:t10V

RL = 20012, Vo = :t5V

Output Voltage

Swing

Vo

RL= 2kn

RL= 200n

Supply

Current

ISY

No Load

Rejection

MIN

MIN

Vos

Common-Mode

MAX

at Vs = ::!:15V,-55°C:;; T A :;;+ 125°C for OP-64A, unless otherwise noted.

Offset

Voltage

OP-64E

TYP

OLE

No Load

noted.

MIN

-

OP-64F

TYP

unless otherwise

0.35

0.3

UNITS

2

mV

2

~A

2

~A

:t11

-

86

100

-

8

20

7.5

30

10

V/mV

:t11

:t7.5

:t12

:t10

V

6.4

V

dB

31.6

8.5

~V/V

mA

NOTE:

1. Guaranteed by CMR test.

2-704

OPERATIONAL AMPLIFIERS

REV. A

~-

OP-54

DICE CHARACTERISTICS

1.

2.

3.

4.

5.

6.

7.

8.

OBS

NULL

-IN

+IN

vNULL

OUT

V+

DISABLE

II

DIE SIZE 0.086 x 0.065 inch, 5,590 sq. mils

(2.18 x 1.65 mm, 3.60 sq. mm)

OLE

WAFER TEST LIMITS at Vs = :t15V, TA= +25°C, unless otherwise noted.

PARAMETER

SYMBOL

Offset Voltage

Vas

CONDITIONS

Input Bias Current

'8

VCM=OV

Input Offset Current

'as

VCM=OV

Input Voltage Range

IVR

(Note f)

Common-Mode Rejection

CMR

VCM=:tf1V

Power Supply

Rejection Ratio

PSRR

Vs=:t5Vto:tf8V

large-Signal

Voltage Gain

Ava

RL =2kO, Vo=:tfOV

RL = 2000, Va =:t5V

Output Voltage

Swing

Va

RL = 2kO

RL = 2000

Slew Rate

SR

Supply Current

OP-64GBC

LIMITS

UNITS

2.5

mV MAX

2.5

~A MAX

2.5

~A MAX

TE

RL = 2kO

'Sy

No load

:tff

VMIN

84

dBMIN

3f.6

~V/V MAX

20

fO

V/mV MIN

:tff

:tfO

VMIN

f20

V/~s MIN

8

mA MAX

NOTES:

f.

Guaranteed by CMR test.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for

standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

-~~~~~.~.~

- ...~. -

.~.~~~

-

--

OP-64

;

TYPICAL PERFORMANCE CHARACTERISTICS

INPUT OFFSET VOLTAGE

vs TEMPERATURE

0.7

INPUT OFFSET CURRENT

vs TEMPERATURE

INPUT BIAS CURRENT

vs TEMPERATURE

0.4

0.5

I

I

Vs t15V

=

~=:l:15V

CM=OV

0.6

/

:;.E.

w

"<[ 0.5

-

~

0

>

I- 0.4

w

en

...

...

0

~

0.3

Q.

g

--

V

.........

1 0.3

1 0.4

/'

\!

w

a::

a::

::J

\!

w

a::

a::

::J

CJ 0.3

en

S

ID

I::J

Q.

Z

i-""'"

-

~ 0.2

en

It

0

I-

0.2

~

0.1

0.2

OBS

0.1

-75

-50

-25

0

25

50

75

100

0.1

-75

125

-SO

-25

TEMPERATURE ("C)

SLEW RATE vs

TEMPERATURE

25

50

200

iiJ

I<5

>

W

N

(jj

a

I -SR

~-4

0

0

25

50

75

100

7

4

25

50

~

"

60

§

a::

55,

75

~

:z: 50

Q.

,

-10mV

100

45

40

-75

125

'-IN = 20mVp-p

~

<[

a::

w

> 40

0

B

0

135

:i:

w

Q.

0

:z:

Q.

TE

-50

<l>m

:!!

~

I-

100g

80

60

0

0

a::

~

Q

;:

Q

~

ID

:i:

;;:

40 "

-25

0

25

50

75

20

100 125

40

NEGATIVE

EDGE

aw 30

60

0

0

:z:

120-

CLOSED-LOOP OUTPUT

IMPEDANCEvsFREQUENCY

~

"w

140

T.=+25"C

Vs=:l:15V

Ay = .5

;:-

125

50

45

iiJ

w

w

a::

100

TEMPERATURE ("C)

T. = .25"C

VS=.,5V

80

20

65

100

90

75

iiJ

SMALL SIGNAL OVERSHOOT

vs CAPACITIVE LOAD

80

g

+10mV

5ETTLING TIME (ns)

OPEN-LOOP GAIN,

PHASEvsFREQUENCY

40

J

<[

~

w

\

0

100

50

Vs =:l:15V

Ay=+5

Rl = 2000

w

B

I\.

\

TEMPERATURE ("C)

~

0.

25

GAIN-BANDWIDTH PRODUCT, PHASE

MARGIN vs TEMPERATURE

/

2

125

60

0

OLE

Ay = +5

-10

-25

-25

70

T. =+25"C

Vsd:15V

-<I

-50

-50

TEMPERATURE ("C)

SETTLING TIME

vs STEP SIZE

--6

50

iD

~

z

0

-75

125

TEMPERATURE ("C)

i1; 0

Ien

I- -2

::J

u:

0

-75

100

75

10

250

'> 150

I

W

!;;:

a::

100

0

CJ

z

<[

0

'"

~

20

180

20

10

-20

-40

0

0

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

2- 706

0

20

40

CAPACITIVE

80

60

lOAD

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

(pF)

OPERA TIONAL AMPLIFIERS

REV. A

--

---~

OP-64

TYPICAL PERFORMANCE CHARACTERISTICS Continued

50

100

100

~30

z

:;;:

" 20

(I)

(5

z

w

....

AVCL ; +5

10

tf

<

I'-

If

~

w

8

100..

10

g

OBS

0

'\

8

w

(I)

.......

(5 10

z

!i:

w

a:

a:

::>

0

'"

~

6>

(I)

0

TA;+25'C

Vs;%15V

TA-+25'C

Vs %15V

40

'"

w

CURRENT NOISE DENSITY

vs FREQUENCY

VOLTAGE NOISE DENSITY

vs FREQUENCY

CLOSED-LOOP GAIN

vs FREQUENCY

.

-10

1

10

-20

10k

1k

100k

100M

10M

1M

FREQUENCY (Hz)

100

1

10

10k

Ik

Vs;:t15V

NOLOAD

7

1.00

6.&

NOLOAD

6.6

6.4

0.75

-

~5

Q.

0

~

Q.

Q.

::>

(I)

0.25

5.2

5.0

-50

-25

0

25

50

75

100

0

125

:t5

TEMPERATURE ('C)

3.0

TA;+25'C

Vs;:t15V

~ 10

..::>

Q.

!;

0

/

/

VOLTAGE

-75

%20

-

+VOM

~

0

&

:E 2.6

::>

:E

)(

2.5

1!i 6

:E

)(

~

:E 4

=OV

-25

0

25

50

75

100

125

TEMPERATURE ('C)

OPEN-LOOP

GAIN

vs SUPPLY VOLTAGE

60

I I

TA; +25'C

I

I

TA =+25'C

RL;2kn

50

ii)

~ 2.&

0

~

!; 2.7

I-YOM

I

-50

(VOLTS)

2.9

-12

~

0

:tIS

MAXIMUMOUTPUT VOLTAGE

vs LOAD RESISTANCE

Vs =:f:5V

=

14

:t10

SUPPLY

MAXIMUMOUTPUT VOLTAGE

vs LOAD RESISTANCE

Vs :f:15V

16

; tl5V

DISABLE

0

4.&

3

-75

TE

Vs

:;;:§.

!i:

w

a:

a:

::>0.50

~5.4

::>

(I)

Isy DISABLE vs

TEMPERATURE

SUPPLY CURRENT

vs SUPPLY VOLTAGE

:;;:-6.2

§.

!i:

w 6.0

a:

g; 5.&

0

~ 5.6

Q.

L..,.........

10k

Ik

FREQUENCY (Hz)

OLE

SUPPLY CURRENT

vs TEMPERATURE

:;;:§.

!i:

w 6

a:

a:

::>

0

100

FREQUENCY (Hz)

:;;

E

+VOM-I-YOM

I

z 40

:;;:

'"

Q.

0

0

-I 30

z

W

Q.

0

/"

;!

20

2.4

0

100

1k

1Ok

2.3

100

10

1k

LOADRESISTANCE(n)

10k

~--

0

:t5

:t10

:t15

SUPPLY VOLTAGE (VOLTS)

LOADRESISTANCE

(n)

-

:t2O

OP-64

TYPICAL PERFORMANCE CHARACTERISTICS

Continued

OPEN-LOOPGAIN

vs SUPPLYVOLTAGE

COMMON-MODEREJECTION

vs FREQUENCY

25

140

RL=2000

m

-

-

t; 80

-

-

:!!.1oo

z

0

:>

E

~

z 15

;;

"

w

.,w

I-

Vs=:1SV-

120

20

r-

111111111

TA=+2S'C

TA=+25'C

.......

"

a:

w 60

0

0

=i'

z 40

0

::

0:: 20

OJ

Q.

0

0

~

z 10

W

Q.

0

-

OBS

0

:5

0

:10

SUPPLY

:15

VOLTAGE

-20

%20

'-1k

10k

(VOLTS)

OLE

140

m120

:!!.

0

~

100

t;

80

w

UJ

a:

>~

Q.

::>

UJ 40

a:

w

3:

~

0.7

-~

,

0.6

\.

~

w 0.5

a:

\

aUJ 0.4

\

0.1

0

100

1k

10k

1ook

1M

10M

TA=+2S'C

Vs=:1SV-

1\

;!: 0.2

20

10M

,

0.8

'"

iii

... 0.3

::>

Q.

60

1M

INPUTBIAS CURRENTvs

COMMON-MODEVOLTAGE

POWER SUPPLYREJECTION

RATIO vs FREQUENCY

z

0

100k

FREQUENCY (Hz)

0

-12.5 -10.0 -7.5

FREQUENCY(Hz)

-5.0

TE

" -

-2.5

........

0

2.5

5.0

7.5

10.0 12.5

COMMON-MODE VOLTAGE (VOLTS)

BURN-IN CIRCUIT

10kQ

,;w.+15V

-A

3

+

7

DISABLE

I

10012

2

1:"

-=-

2-708

-15V

OPERATlONALAMPLlFIERS

REV.

-

--

~~

~-

A

OP-64

LARGE AND SMALL SIGNAL RESPONSE

TEST CIRCUIT

LARGE SIGNAL RESPONSE (Vs =:t15V)

+v

OUTPUT

-=DISABLE

VIN

INPUT

VOUT

200U

1.6kU

OBS

SMALL SIGNAL RESPONSE

(V s

= :t15V)

LARGE SIGNAL RESPONSE (V s = :t5V)

-=-

10~,+

400n

0.1~F~

OLE

-=-

~-=-

AV = +5

-v

obtaining optimum performance from the OP-64. Proper high

frequency layout reduces unwanted signal coupling in the circuit. When breadboarding a high frequency circuit, use direct

point-to-point wiring, keeping all lead lengths as short as possible. Do not use wire-wrap boards or "plug-in" prototyping

boards.

TE

During PC board layout, keep all lead lengths and traces as

short as possible to minimize inductance. The feedback and

gain-setting resistors should be as close as possible to the inverting input to reduce stray capacitance at that point. To further

V+

APPLICATIONS

INFORMATION

POWER SUPPLY BYPASSING AND

LA YOUT CONSIDERATIONS

Proper power supply bypassing is critical in all high-frequency

circuit applications. For stable operation of the OP-64, the

power supplies must maintain a low impedance-to-ground over

an extremely wide bandwidth. This is most critical when driving

a low resistance or large capacitance, since the current required

to drive the load comes from the power supplies. A 10llF and

O.1IlF ceramic bypass capacitor are recommended for each

supply, as shown in Figure 1, and will provide adequate highfrequency bypassing in most applications. The bypass capacitors should be placed at the supply pins of the OP-64. As with all

high frequencyamplifiers,circuit layout is a critical factor in

V-

I

0.1~F

FIGURE 1: Proper power supply bypassing is required to obtain

optimum performance with the OP-64.

reduce stray capacitance, remove the ground plane from the

area around the inputs of the OP-64. Elsewhere, the use of a

solid unbroken ground plane will insure a good high-frequency

ground.

II

OP-64

v+

+15V

10~F

:!iF-,

DISABLE

0.1~~

1.6kn

-

OUT

J

VOUT

RpOT

=20kn

TO 100kn

200n

v-

10~F

-=-

=1~

FIGURE 2: Input Offset Voltage Nulling

OBS

OFFSET VOLTAGE ADJUSTMENT

Offset voltage is adjusted with a 2OkQpotentiometer as shown

in Figure 2. The potentiometer should be connected between

pins 1 and 5 with its wiper connected to the V- supply. The typical trim range is :t4mV.

OP-64 DISABLE

AMPLIFIER

SHUTDOWN

-15V

FIGURE 4: DISABLE Turn-On/Turn-Off Test Circuit

limits the DISABLE current to around 500J.lA if the DISABLE pin

is grounded with the OP-64 powered by :t15V supplies. These

logic interface methods have the added advantage of level shifting the TTL signal to whatever supply voltage is used to power

the OP-64.

TE

Figure 4 shows a test circuit for measuring the turn-on and turnoff times for the OP-64. The OP-64 is in a gain of 5 with a + 1V DC

input. As the input pulse to the 74LSO4 rises its output falls,

v+

V+

V,N

6

ov~

n

-=-

OLE

Pin 8 of the OP-64, DISABLE, is an amplifier shutdown control

input. The OP-64 operates normally when Pin 8 is left floating.

When greater than 250J.lA is drawn from the DISABLE pin, the

OP-64 is disabled. The supply current drops to 1mA and the

output impedance rises to 2kQ. To draw current from the DISABLE pin, an open collector output logic gate or a discrete NPN

transistor can be used as shown in Figure 3. An internal resistor

2V

0'1~

VIN

VOUT

VOUT

5kU

L

2N2222

LOGIC GATE

WITH OPEN

COLLECTOR/DRAIN

OUTPUT

-=-

V-

V-

FIGURE 3: Simple circuits allow the OP-64 to be shut down.

2-710

OPERA TIONALAMPLIFIERS

REV. A

-------

OP-64

drawing current from the DISABLE pin and disabling the amplifier. The output voltage delay is shown in Figure S and takes

SOOflSto reach ground due to the extra current supplied to the

amplifier by the 10flF electrolytic bypass capacitors. The turnon time is much quicker than the turn-off time. In this situation as

the input to the 74LS04 falls its output rises, returning the OP-64

to normal operation. The amplifier's output turns on in 2S0ns.

The 7sn cable termination resistor minimizes reflections from

the end of the cable. The 7Sn series output resistor absorbs any

reflections caused by a mismatch between the 7sn termination

resistor and the characteristic cable impedance. In this circuit

the output voltage, VOUT' is one-half of the OP-64's output voltage due to the divider formed by the 7Sn terminating resistors.

The output voltage at the end of the terminated cable, V OUT'

spans -1 V to + 1V. The differential gain and phase for the video

amplifier is summarized in Table1.

(a)

OBS

OUTPUT

TABLE 1: Differential Gain and Phase of Video Amplifier/Line

Driver

Differential Gain

3.58MHz

5MHz

~

lOGIC INPUT

:t1SV

:t12V

0.008dB

0.008dB

0.016dB

0.018dB

OLE

(b)

Phase

5MHz

Differential

3.58MHz

0.03°

0.03°

0.03°

0.03°

+15V

1~S.:!:1V

SQUARE

lOGIC INPUT

IO~F

TE

OUTPUT

:i4f-=

J

0.1~

WAVE

VIN

50>2

1

6

Your

200>2

0.1~F

-=-

FIGURE5: (a) OP-64 turn-on and turn-offperformance. (b)

Expanded scale showing turn-onperformance of the OP-64.

-=-

-=-

10~F~

_.~

-=-

-15V

OVERDRIVERECOVERY

Figure 6 shows the overdrive recovery performance of the OP64. Typical recovery time is 270ns from negative overdrive and

80ns from positive overdrive.

FIGURE7: Overdrive Recovery Test Circuit

+15V

VIDEO AMPLIFIERITERMINATED LINE DRIVER

The OP-64 can be used as a video amplifier/terminated line

driver as shown in Figure 8. With its high output current capability, the OP-64 eliminates the need for an external buffer.

DISABLE

VON

VOUT

75>2

R,

.

"

R2

400>2

.

~_1

R

-=-

1.6k>2

-=-

-15V

VOUT-2(~+1)

2

-$$TTL)

!~Fi!

...

..-

.mt~-i~~

.

FIGURE6: OP-64 Overdrive Recovery

---

VON

1V/DIVISION

FIGURE8: Video Amplifier/Terminated Line Driver

II

OP-64

R3

400kO

I ~~~DANCE

I SOURCE

,

1Mn

~

I

-

C,

Iin

G

1pF

VOUT

R.

I

I

I

-=I

I1_____-

R,

soon

:

3000

R2

2000

-15V

-=-

-5V

OBS

-=-

FIGURE 9: Fast Transimpedance Amplifier

OLE

FAST TRANSIMPEDANCE AMPLIFIER

The circuit shown in Figure 9 is a fast transimpedance amplifier

designed to handle high speed signals from a high impedance

source such as the output of a photomultiplier tube. The input

current is amplified and converted to an output voltage by the

transimpedance amplifier.

A JFET source-follower input is used to reduce the input bias

current of the amplifier to 100 pA and lower the input current

noise. Transimpedance of the amplifier is:

VOUT= B1+1

hN

(

R2

)

OP-64 SPICE MACRO-MODEL

and for the values shown equals

(

TE

FIGURE10: Output of the Fast Transimpedance Amplifier

A3

)

VOUT = 800il + 1 400kil

hN

200il

Figure 11 shows the node and net list for a SPICE macro-model of

the OP-64. The model is a simplified version ofthe actual device and

= 2VfllA

Figure 10 shows the output of the transimpedance

amplifier

when driven from a 1Mil source impedance. The input signal of

101lA- is convertedinto an outputvoltageof (1GIlA)2VfIlA=

20V ~: Output slew rate is 1OOVfJls. The slew rate is limited by

the 66mbination of the capacitance of the JFET gate with the

1Mil source impedance. For best performance, the stray input

capacitance should be kept as small as possible. The OP-97 is

used in an integrator loop to reduce the total amplifier offset

voltage to under 25JlV.

2- 712 OPERA TIONAL AMPLIFIERS

simulates important DC parameters such as V os' los. Ie' Avo' CMR.

V 0 and ISY.AC parameters such as slew rate, gain and phase response and CMR change with frequency are also simulated by the

model.

The model uses typical parameters for the OP-64. The poles and

zeros in the model were determined from the actual open and closedloop gain and phase response of the OP-64. In this way the model

presents an accurate AC representation of the actual device. The

model assumes an ambient temperature of 25°C (see following

pages).

REV. A

-

OP-64

99

j

@PM11989

C2

RJ ~.

1°.

2

IN-~Q,

Q 6.

R,

'os

::;:

67

9

~G' iR7 lCJ ~GJ iR> :::= c.

D,

8

CON 13

R.

4

R.

Ml

11

II

~

R2

1

OBS

IN+

-+

Eos

99

l,

1

r L-

G7

1.9

l.o

I

I

::;: C.

(e)

L,

R17

H

1

frt'

Roo l.

TE

$.' ~." f" $.0 ~.. !', ~." k

R18

'. ,,"

I

(b)

R,>

GJ ~-

I,

..LC4 >4>{G4 ~R,O

I

OLE

(8)

16

~

rbG 2 ~R.

Y

.-+

~G,O

~

I

~R22

:::=C.

I

I

>4>{G'2 ~R24

124

:::=c,O >4>{G'4 ~R26

!~,

:::=C'2

-

50~

(d)

(e)

(g)

(I)

(h)

V.

99

. D7

G17 .27

~G,>

~RJ2 ~C,.

D.

G23

~RJ4

~R36

D.

V.

+26

1

R..

G,. .:~

L H

~GOO iR~

f32

lc,.

D.

34

V7

35

-+

(I)

is a registered trademark

of MieroSim Corporation.

.. HSPICE is a tradename 01Meta-Software, Inc.

OUT

~G24

:::>R37

V(J)

FIGURE 11a: OP-64 SPICE Macro-ModelSchematic and Node List

. PSpice

I '--038

iRJO

I

50

~

(k)

OP-64

OP-64 MACRO-MODEL

*

.

*

*

*POLE AT 159 MHz

*

1E6

r23 23 99

1E6

r24 23 50

c9 23 99

1E-15

1E-15

c10 23 50

22 32

911 99 23

32 22

50

*91223

*POLE AT 159 MHz

*

1E6

r25 24 99

r26 24 50

1E6

c1124

99

1E-15

c1224

50

1E-15

23 32

913 99 24

32 23

914 24 50

I/:)PMI1989

subckt OP-64 1 2 38 99 50

INPUT STAGE & POLE AT 39.8 MHz

*

r1 2

5E11

3

r2 1

3

5E11

474.86

r3 5

99

474.86

r4 6

99

r5 4

7

423.26

8

423.26

r6 4

5E-12

Gin 1

2

4.2106E-12

c2 5

6

i1 4

1E-3

50

1E-7

ios 1

2

aos 9

1

poly(1) 26 32 4E-4 1

7

2

q1 5

qx

8

9

q2

6

qx

*

*

1E-6

1E-6

1E-6

1E-6

*COMMON-MODE

GAINNETWORKWITHZEROAT 20kHz

*

OBS

* SECOND STAGE & POLE AT 3.8 kHz

*

r7 11 99

7.1229E6

r8 11 50

7.1229E6

c3 11 99

5.88E-12

c4 11 50

5.88E-12

91 99 11

poly(1) 5 6 4.31E-3 2.1059E-3

92 11 50

poly(1) 6 5 4.31E-3 2.1059E-3

v2 99 10

2.25

v3 12 50

2.25

d1 11 10

dx

d2 12 11

dx

*

* POLE AT 39.8 MHz

*

r9 13 99

1E6

r10 13 50

1E6

c5 13 99

4E-15

c6 13 50

4E-15

11 32 1E-6

93 99 13

32 11 1E-6

*94 13 50

r29

r30

15

16

917

*918

26

26

27

28

99

26

27

28

99

50

26

50

1E6

1E6

7.9575

7.9575

3332 1E-11

32 33 1E-11

OLE

* POLE AT 159 MHz

*

1E6

r32 31 99

1E6

r33 31 50

1E-15

c15 31 99

1E-15

c1631

50

24 32 1E-6

919 99 31

32241E-6

50

*92031

TE

* OUTPUT STAGE

*

r34 32 99

20.0E3

r35 32 50

20.0E3

60

r36 33 99

r37 33 50

60

17 33 38

2.9E-7

31 33 16.6666667E-3

92136

50

33 31 16.6666667E-3

922 37 50

99 31 16.6666667E-3

92333

99

31 50 16.6666667E-3

92450

33

v6 34 33

1.7

1.7

v7 33 35

d5 31 34

dx

d6 35 31

dx

d7 99 36

dx

d8 99 37

dx

d9 50 36

dy

d10 50 37

dy

*

** ZERO-POLE PAIR AT 26.5 MHz 1159 MHz

r13 16 17

1E6

r14 16 18

1E6

r15 17 99

5E6

r16 18 50

5E6

11 17 99

5.005E-3

12 18 50

5.005E-3

13 32 1E-6

95 99 16

32 13 1E-6

*96 16 50

** ZERO-POLE PAIR AT 31.8 MHz 139.8 MHz

r17 19 20

1E6

r18 19 21

1E6

r19 20 99

2.5157E5

r20 21 50

2.5157E5

13 20 99

1.006E-3

14 21 50

1.006E-3

16321E-6

97 99 19

32 161E-6

*98 19 50

* POLE AT 100 MHz

*

r21 22 99

1E6

r22 22 50

1E6

c7 22 99

1.59E-15

c8 22 50

1.59E-15

19 321E-6

99 99 22

32 19 1E-6

910 22 50

* MODELS USED

*

.model qx NPN(BF=2500)

.model dx

D(IS=1E-15)

.model dy

D(IS=1E-15 BV=50)

"ends OP-64

FIGURE 11 b: OP-64 SPICE Net-List

2-714

OPERA TIONAL AMPLIFIERS

REV. A

-~

~--

~

~