introduction to MIPS assembly

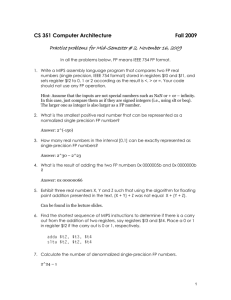

advertisement

Computer Architecture Introduction to MIPS-assembler – november 2008 karl.marklund@it.uu.se ALU Once an ALU is designed, we need to define how it interacts with the rest of the processor. The Von Neuman Model (Stored Program Computer): Data and Instructions both stored in memory. a b ALU The symbol for a ALU with data input a and b, operation input OP and data output c c OP a b ALU What exactly do we mean with a, b and c? c OP a We use registers to hold input data and output data. b ALU OP c Input must be in one of these 32 registers. Each register stores 32 bits. Could use a multiplexer here…. ... ALU OP 0 Input must be in one of these 32 registers. 1 Each register can store 32 bits. 2 3 4 5 6 7 8 a 9 MIPS is a Register-toregister architecture. 10 11 b 12 13 14 Output must go back to a register. 15 c 16 17 18 19 ALU 20 21 22 23 24 25 26 27 28 29 30 31 c Í a OP b OP add add Alternative notation for cÍa+b c, a, b $15, $8, $11 Use $n to specify one of the 32 register ($0, ..., $31). Yihaa! This is the first example of an instruction written in the MIPS assembly language. An assembly language is a low-level language for programming computers. It implements a symbolic representation of the numeric machine codes and other constants needed to program a particular CPU architecture. Design Principle 1 - Simplicity favors regularity Keep the design simple and things tend to behave and look similar to each other. $15 = $8 + $11 add $15, $8, $11 Following the design principle ”Simplicity favors regularity” we define subtraction in a very similar way as addition. $15 = $8 - $11 sub $15, $8, $11 Favors Simplicity Regularity Operands must be in a register and result must be stored back to a register. Different instructions are definied in a similar fashion. ... But for sure we need a way of checking if two numbers are equal (a =?= b) Ok, we can add and subtract... A simple 4-bit comparator. 1 here iff A0 != B0 A B 0 0 0 A == B A XOR B NOT (A XOR B) 1 0 1 1 0 1 0 1 0 0 1 0 1 1 1 0 1 equal equal Enough for one of the inputs to be 1 (on of the bit pair is not equal) for the output from the NOR gate to become 0. 0 1 seq 2 $15, $8, $11 3 4 5 6 7 8 $8 Set EQual 9 10 11 $11 12 13 14 Set to 1 if content of $8 is equal to content of $11, othervise set to 0. 15 $15 16 17 18 19 ALU OP 20 21 22 23 24 25 26 27 28 29 30 31 The format of the seq instruction is very similar to add and sub (regularity). 0 1 2 But why is there only 32 registers? 3 4 5 6 7 8 $8 9 10 11 $11 12 13 14 15 $15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 ALU OP Design Principle 2: Smaller is faster. Logic needed here to select registers. Beeing small is not a bad thing! register a 5 bit 32 bit register b 5 bit 32 Registers 32 bit ALU register c 5 bit 32 bit More registers Î more bits needed to select Î more complicated logic Î take more space on the chip Î take more time OP A MIPS instruction in closeup 6 bits 5 bits 5 bits 5 bits op rs rt rd 5 bits 6 bits shamt funct 32 bits add $16, $17, $8 000000 10001 01000 10000 00000 100000 op rs rt rd shamt funct typ R e Design Principle 3: Make the common case fast. Add Immediate addi $15, $8, 77 Constants known at compile time don’t need to be stored in a register. Let the constant be encoded direcly in the instruction (immediately available). Design principle 4 – Good design demands good compromises All instruction up to now (add, sub, seq) have been regular, using two register for input and one for output. To be able to use immediate constants we must compromise and break the regularity… 6 bits 5 bits 5 bits 16 bits op rs rt immediate 32 bits addi $15, $8, 77 001000 01000 01111 op rs rt Not the same op code as for add 0000000001001101 immediate e p y I-t Sofar, all instruction use data from the registers and write the result back to a register. register a 5 bit 32 bit register b 5 bit 32 Registers 32 bit ALU register c 5 bit 32 bit The generic format of a MIPSassembly instruction. Operation add, sub, addi, etc. The first operand register, source register one. op add addi rd, rs, rt rd, rs, imm sub subi rd, rs, rt rd, rs, rt seq rd, rs, rt rd, rs, rt Register to hold the result. The destination register. The second operand source register two. There is no subi instruction... Instead, we can use addi and a negative immediate constant. Instructions we know so far. MEMORY Address Content 0xFFFFFFFF 0xFFFFFFFE 0xFFFFFFFD Each cell has a unique address. Four adjacent bytes forms a word of 32 bits. In MIPS the memory consists of 232 memory cells. 0xFFFFFFFC . . . 0x00000003 0x00000002 0x00000001 0x00000000 Each cell can store 8 bits – a byte. MIPS is a Load-Store architecture which means only load and store instructions are allowed to access memory. lw sw rt, address rt, address MEMORY Assume the address 0x00000004 is stored in register $8 Address 0xFFFFFFFF Content 0xFFFFFFFE lw $15, 0($8) 0xFFFFFFFD 0xFFFFFFFC Load Word The lw instruction fetches the word at address 0x00000004 and stores it in register $15. . . . 0x00000007 0xDD 0x00000006 0xCC 0x00000005 0xBB 0x00000004 0xAA 0x00000003 0x00000002 0x00000001 0x00000000 A word 0x 0xCC 0xCC 0xBB 0xAA 7 6 5 4 CC CC BB AA Little Endian: The least significant byte (LSB) value (0xAA), is at the lowest address. The other bytes follow in increasing order of significance. Intel x86 and Power PC uses little endian. Some architectures (MIPS) feature switchable endianness and can be configured to use big endian (or little endian). A word Big Endian: The most significant byte (MSB) value (0xAA), is stored at the memory location with the lowest address. 0x 0xAA 0XBB 0xCC 0xDD 4 5 6 7 AA BB CC DD MEMORY Assume the address 0x00000004 is stored in register $8 Address Content 0xFFFFFFFF 0xFFFFFFFE lw $15, -4($8) 0xFFFFFFFD 0xFFFFFFFC We can specify an offset. . . . 0x00000007 0x00000006 This lw instruction feteches the word att address 0x00000004 - 0x4 = 0x00000000 , and stores it in register $15. 0x00000005 0x00000004 0x00000003 0x00000002 0x00000001 0x00000000 Ok, using lw we can fetch data from memory to registers. To do the opposite, store data from a register to a location in memory, we use the sw instruction. lw sw rt, address rt, address MEMORY Assume the address 0x00000004 is stored in register $8 Address Content 0xFFFFFFFF 0xFFFFFFFE sw $15, 0($8) 0xFFFFFFFD 0xFFFFFFFC Store Word . . . 0x00000007 0x00000006 0x00000005 0x00000004 This instruction will store the content of register $15 as a word at address 0x00000004 in memory. 0x00000003 0x00000002 0x00000001 0x00000000 lw $15, 4($8) 100011 01000 01111 op rs rt 0000000000001000 immediate sw $15, 4($8) 101011 01000 01111 op rs rt 0000000000000100 immediate e p y I-t