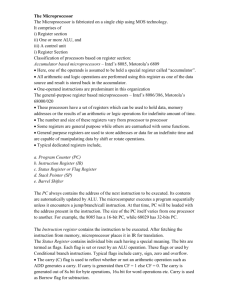

Central Processing Unit

advertisement