here - Edge

advertisement

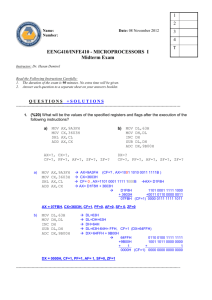

BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE, PILANI II SEMESTER 2014-2015 CSF241/ECEF241/EEEF241/INSTRF241MICROPROCESSOR PROGRAMMING AND INTERFACING TEST I (OPEN BOOK) TIME: 60 Min. 28/02/2015 MM: 40 IDNO: Name: Q1. In an 80486 processor that is working in real mode and 16-bit mode: Suppose that: CS =1000H, ES = 8000H, DS=A000H, SS =7000H , ESI= 0000 0200H , EDI = 0000 0410H ,EBP = 0000 2300H , EBX= 0000 0200H EAX=0000 0400H , ECX = 0000 0020H, EDX = 0000 0008H For the instructions given below determine the following. [Give Values only in Hex only] [1+1+2= 4] a) MOV [BP+SI+2000H],CX Memory Address 74500H Addressing Mode Base Relative Plus Index Machine Code 89 8A 00 20 Q2. Replace the following program segments by a single instruction of 80486. You can assume that all flags (except Trap and Interrupt) are reset at the beginning of each of these program segment [Clarification: Each program segment achieves a certain final result. You need to give a single instruction that will achieve the same result. The single instruction needs only achieve the final result] [6 x 2.5= 15] Program Instruction Program Instruction A PUSH AX XCHG AX,BX B PUSHF LAHF PUSH BX PUSH BP POP AX MOV BP,SP POP BX MOV AH,[BP+2] POP BP POPF C CMP EBX,EAX CMPXCHG D MOV [0200],ESP* PUSHAD JNE X1 EBX,ECX PUSH EAX MOV EBX,ECX PUSH ECX JMP X2 PUSH EDX X1: MOV EAX,EBX PUSH EBX X2: PUSH DWORD PTR[0200] PUSH EBP PUSH ESI PUSH EDI E PUSHF MOVSX BX,BL F PUSHF MOVSW MOV BH,FF PUSH AX CMP BL,0 MOV AX,[SI] JL X1 MOV ES: [DI],AX NOT BH POP AX X1: POPF INC SI INC SI INC DI INC DI POPF *DS: [0200] – is just a temp location – what happens to it does not matter in the final result. 1 Marks on this page Q3. For the following Instructions what will be the machine cycles executed by 8086. Enter the machine cycles in proper order [1x4 = 4] A Instruction ADD [BX+SI+1000] , CX C NOP Q4. Cycles 1 MEMR (opcode) 1 MEMR (disp) 1 MEMR (operand) 1 MEMW (result) 1 MEMR (opcode) B Instruction XCHG AX,[BX] Cycles 1 MEMR (opcode) 1 MEMR (operand) 1 MEMW (exchange) D CMP [SI],AX 1 MEMR (opcode) 1 MEMR (operand) If a processor is working at 5 MHz and the memory access time is 750ns. The number of wait states required will be 2 , considering an address set-up time of 110ns, data set- up time of 40ns with a latching and buffer delays of 30ns. Q5. What will be the effect of executing the following code snippet on an 8086 processor? [2] [2] MOV BX, FFFFH AND BX, 0700H PUSH BX POPF Sets all condition flags and resets all status flags (TF, IF, DF =1; SF, ZF, AC, CF, OF, PF =0) Q6. Write an 80486 ALP that will examine a series of memory locations for small alphabets. If a memory location has a small alphabet it will convert it into capitals. If the memory location does not have a small alphabet it will not modify the contents of the memory location. The series of memory location to be examined start at alph1. The count of memory locations to be examined is stored in cnt1 and will not exceed 1000d. The checking and the conversion of one small alphabet to one capital alphabet must be done using a macro called CAPSON. [13] [YOU CAN USE THE BLANK SPACE AT THE BACK OF THIS PAGE FOR WRITING THE PROGRAM] .Model tiny .486 .data alph1 db '3','4','a','B','c','d','E','l','0','n' db 990 dup (?) cnt1 dw 1000 Program Structure -2 capson macro cmp al,'a' Initialization of pointer & count -1 jl x2 cmp al,'z' Comparing for between ‘a’ to ‘z’ – 3 jg x2 Looping – 2 sub al,20h x2: Macro structure -1 endm .code Macro Position -1 .startup Conversion - 3 lea di,alph1 mov cx,cnt1 x1: mov al,[di] capson stosb loop x1 .exit end 2 Marks on this page