Elementary Logic Gates: AND, OR, NOT, XOR, NAND, NOR

advertisement

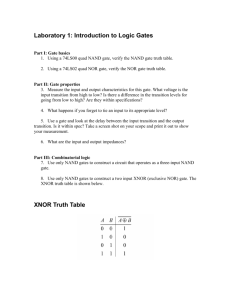

Elementary Logic Gates Name Inverter (NOT Gate) Symbol Truth Table Logic Equation C. E. Stroud A Z AND Gate A B OR Gate Z A B Z A B Z A B Z A Z 0 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 1 1 1 1 Z = A’ = A Z = A • B = AB Combinational Logic Design (1/06) Z=A+B 1 Other Elementary Logic Gates NAND Gate (NOT AND) A B Name Z A B Z Symbol NOR Gate A B (NOT OR) Z A B Z A B Z 0 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0 A B Z 0 0 1 0 1 1 1 Truth Table Z = (A • B)’ = AB Logic Equation Z = (A + B)’ = A+B C. E. Stroud Combinational Logic Design (1/06) 2 Using Truth Tables to Prove Theorems • DeMorgan’s Theorems T8a: (X+Y)’ = X’•Y’ a NOR gate is equivalent to an AND gate with inverted inputs X Y Z NOR X Y C. E. Stroud X Y Z 0 0 1 0 1 0 1 0 0 1 1 0 T8b: (X•Y)’ = X’+Y’ a NAND gate is equivalent to an OR gate with inverted inputs X ⇔ Z Y Z NOR X Y NAND X alternate Y logic symbols Combinational Logic Design (1/06) Z X Y Z 0 0 1 0 1 1 1 0 1 1 1 0 X ⇔ Z Y Z NAND 3 Other Logic Gates Name Symbol Truth Table Buffer A Z Exclusive-OR Gate Exclusive-NOR Gate aka XOR Gate aka XNOR or NXOR Gate A A Z Z B B A B Z A B Z A Z 0 0 0 0 0 1 0 0 0 1 1 0 1 0 1 1 1 0 1 1 0 0 1 1 0 1 1 1 Logic Z =A Equation C. E. Stroud Z = A⊕B = AB + AB Z = A⊕B = A B + AB also denoted Z = A B Combinational Logic Design (1/06) 4 Interesting Properties of Exclusive-OR • Controlled inverter ¾ X⊕0=X ¾ X⊕1=X’ • XOR with one input inverted = XNOR ¾ X⊕Y’=X’⊕Y=(X⊕Y)’ • XNOR with one input inverted = XOR ¾ (X⊕Y’)’=(X’⊕Y)’=X⊕Y • Constant output ¾ X⊕X=0 ¾ X⊕X’=1 C. E. Stroud Combinational Logic Design (1/06) 5 Exclusive-OR Implementations A’ A • Z=A’B+AB’ • XOR & XNOR not considered elementary logic gates by many designers B A (A(AB)’)’ 4 gates = A AB • B AB = A AB + B AB = A(A+B) + B(A+B) = AA’+AB’+A’B+BB’=AB’+A’B C. E. Stroud B’ A (B(AB)’)’ B Z=((A(AB)’)’(B(AB)’)’)’ Z 5 gates Z (AB)’ A’B AB’ (A+B)’ 3 gates Z AB B Z=((A+B)’+AB)’ = A+B+AB = (A+B)•AB = (A+B)(A+B) = AA’+AB’+A’B+BB’ = 0+AB’+A’B+0 = AB’+A’B Combinational Logic Design (1/06) 6 Functionally Complete Set of Gates • If any digital circuit can be built from a set of gates, that set is said to be functionally complete • Functionally complete sets of gates: ¾ AND, OR, & NOT ¾ NAND ¾ NOR ¾ Multiplexers • To show a set of gates is functionally complete, we must show that you can construct AND, OR and NOT functions C. E. Stroud Combinational Logic Design (1/06) 7 Functionally Complete Set of Gates A A B A B C. E. Stroud Z=A’ • The NAND gate is functionally complete ¾ We can build any digital logic circuit out of all NAND gates • Same holds true for the NOR Z=AB gate and the multiplexer • The XOR & XNOR are not functionally complete Z=A+B using DeMorgan’s Theorem Combinational Logic Design (1/06) 8 Gate-level Representations • SOP expressions A ¾ AND-OR • With inverters for complemented literals Z=A’B’C+A’BC+ABC’+ABC ¾ aka 2-level AND-OR logic representation • POS expressions C 8 gates A ¾ OR-AND • With inverters for complemented literals Z=(A+B+C)•(A+B’+C) •(A’+B+C)•(A’+B+C’) ¾ aka 2-level OR-AND logic representation C. E. Stroud Z B Z B C Combinational Logic Design (1/06) 9 Gate Level Representation • from Boolean equation Z = (((A’B)’C)’+D’)’= ((A•B)•C)+D A A’ (A’B)’ ((A’B)’C)’ B C D C. E. Stroud Z D’ Combinational Logic Design (1/06) 10 Circuit Analysis • Going from gate-level to ¾truth table • Apply 0s & 1s to inputs to get outputs ¾Boolean equation • Move equations to output Z=(A+B’)C+A’BC’=AC+B’C+A’BC’ A B C A+B’ B’ (A+B’)C C. E. Stroud B C Z 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1 Z A’ C’ A A’BC’ Combinational Logic Design (1/06) 11 Circuit Analysis • We can implement different circuits for same logic function that are functionally equivalent (produce the correct output response for all input values) ¾ Which implementation is the best? • Depends on design goals and criteria • Area analysis ¾ Number of gates, G (most commonly used) ¾ Number of gate inputs and outputs, GIO (more accurate) • Bigger gates take up more area • Performance analysis (worst case path from inputs to outputs) ¾ Number of gates in worst case path from input to output, Gdel ¾ More accurate delay measurement per gate • Propagation delay = intrinsic (internal) delay + extrinsic (external) delay • Relative prop delay, Pdel = # inputs to gate (intrinsic) + # loads (extrinsic) C. E. Stroud Combinational Logic Design (1/06) 12 Circuit Analysis Example • From previous example: Z=(A+B’)C+A’BC’ ¾# gates: G = 7 ¾# gate I/O: GIO = 19 ¾Gate delay: Gdel = 4 • worst case path: B→Z ¾Prop delay: Pdel = 12 2A 2B 2C B’ A+B’ 1+1 2+1 A’ 1+1 C’ 1+1 (A+B’)C 2+1 3+1 Z 2+0 A’BC’ • worst case path: B→Z C. E. Stroud Combinational Logic Design (1/06) 13 Circuit Optimization • Obviously we want smallest, fastest circuit • Some Basic Goals: ¾Minimizing # product terms minimizes # of AND gates and # inputs to OR gate in a 2-level SOP (AND-OR) representation ¾Minimizing # literals in each product term minimizes # inputs to its AND gate • We can use postulates & theorems, but… ¾It would be nice to find a more reliable procedure C. E. Stroud Combinational Logic Design (1/06) 14