Lecture 16 - ECE Users Pages

advertisement

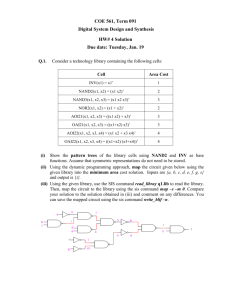

ECE 3060 VLSI and Advanced Digital Design Lecture 16 Technology Mapping/Library Binding Outline • Modeling and problem analysis • Rule-based systems for library binding • Algorithms for library binding – structural covering/matching – boolean covering/matching • Concurrent minimization and binding Disclaimer: lecture notes based on originals by Giovanni De Micheli Technology Mapping/Library Binding • Given an unbound logic network, already minimized, and a set of library cells – transform into an interconnection of instances of library cells – various design goals 8optimize area (under delay constraints) 8optimize delay (under area constraints) 8optimize power (under delay constraints) • Method used for redesigning circuits in different technologies Library models • Combinational elements – single-output functions 8e.g., AND, OR, AOI – compound cells 8e.g., adders, encoders • Sequential elements – registers, counters • Miscellaneous – three-state drivers Major Approaches • Rule-based systems: – mimic designer activity – handle all types of cells • Heuristic algorithms – In general, restricted to single-output combinational cells • Most tools use a combination of both rulebased and heuristic algorithms – e.g., replace adders in design with adders in library (rule-based), use heuristic algorithms for random logic Rule-based library binding • Binding by stepwise transformations • Data-base – set if patterns associated with best implementation • Rules – select subnetwork to be mapped – handle high-fanout problems, buffering, etc. Example Algorithms for library binding • Mainly for single-output combinational cells • Fast and efficient – quality comparable to rule-based systems • Library description/update is simple – each cell modeled by its function or equivalent pattern Problem analysis • To do library binding (technology mapping), we need to solve two subproblems: – Matching 8a cell matches a subnetwork if their terminal behaviors are the same 8input-variable assignment problem – Covering 8a cover of an unbound network is a partition into subnetworks which can be replaced by library cells Assumptions • Network granularity is fine – decomposition into base functions 82-input AND, OR, NAND, NOR • Trivial binding – replacement of each vertex by base cell Example Example Example • Vertex covering: – cover v1: m1 + m4 + m5 – cover v2: m2 + m4 – cover v3: m3 + m5 • Note that – match m2 requires m1 – match m3 requires m1 • This problem is intractable Heuristic algorithms • Strategy: apply two preprocessing steps before covering, decomposition and partitioning • Decomposition – cast network and library in standard form – decompose into base functions – example: NAND2 and INV • Partitioning: – break network into cones – transform network from multiple-input multiple-output to many mutiple-input single-output subnetworks • Covering – cover each subnetwork by library cells Decomposition Partitioning Covering Structural matching and covering • Expression patterns – represented by dags • Identify pattern dags in network – sub-graph isomorphism • Simplification – use tree patterns Example Tree-based matching • Network – partitioned and decomposed 8NOR2 (or NAND) + INV 8generic base functions – each cone is called a subject tree • Library – represented by trees – possibly more than one tree per library cell • Can solve library binding problem with pattern recognition – simple binary tree match Disclaimer: lecture notes based on originals by Giovanni De Micheli Simple library Tree covering • Dynamic programming – visit subject tree from the bottom up (from the input variables up) • At each vertex – attempt to match 8locally rooted subtree 8all library cells • Optimum solution (e.g., to minimize area) for the subtree Example Example Tree covering - labeling • For all vertices in the subject tree, the covering algorithm determines matches between locally rooted subtrees and pattern trees • Three possible conditions for any vertex and a given pattern tree: – the cell tree and the rooted subtree are isomorphic 8the vertex is labeled with the cell cost – the cell tree is isomorphic to a subtree with leaves L 8the vertex is labeled with the cell cost plus the labels of the vertices L – there is no match 8cannot happen when the base functions are in the library Example of labeling • Goal: minimum area cover • Area costs: – INV:2; NAND2:3; AND2:4; AOI21:6 • Best choice found: – AOI21 fed by a NAND2 gate Example Minimum delay cover • Dynamic programming approach • Cost related to gate delay • Delay modeling – constant gate delay 8straightforward – load dependent delay: constant + load dependent term 8load fanout unknown – for most libraries, values of input capacitance are finite and small 8therefore, can use binning techniques, where we label each vertex with all possible load values Minimum delay cover constant delays • Same labeling rules as the minimum area case • If the cell pattern tree and the rooted subtree are isomorphic, – the vertex is labeled with the cell delay • If the cell tree is isomorphic to a subtree with leaves L, each leaf already labeled, – the vertex is labeled with the cell cost plus the maximum of the labels of L Example • Inputs are all ready at time 0, except for d, which arrives at time 6 • Constant delays: – INV:2; NAND2:4; AND2:5; AOI21:10 • Compute label for each vertex from the bottom up – labels ti are data-ready times – tx = 4; ty = 2; tz = 4; tw = 2; • Best choice: – AND2, two NAND2 and INV Example Minimum delay cover load dependent delays • Model: – assume a finite set of load values • Dynamic programming approach: – compute an array of solutions for each possible load – for each input to a matching cell, the best match for any load is selected • Optimum solution, when all possible loads are considered Example • Input data-ready times are 0, except for td = 6 • Load-dependent delays: – = oad at output – INV:1+ ; NAND2:3+ ; AND2:4+ ; AOI21:9+ • Loads: (for use with ) – INV:1; NAND2:1; AND2:1; AOI21:1 • If output load is also 1, the we find the same solution as before Example • Input data-ready times are 0, except for td = 6 • Add super inverter to library: larger area, less delay • Load-dependent delays: – INV:1+ ; NAND2:3+ ; AND2:4+ ; AOI21:9+ ; SINV:1+0.5 • Loads: – INV:1; NAND2:1; AND2:1; AOI21:1; SINV:2 • Assume output load is 1 – same solution as before • Assume output load is 5 – solution uses SINV cell Example